|

ąÉą┐ą┐ą░čĆą░čéąĮčŗą╣ ą╝ąŠą┤čāą╗čī PWM ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī čüąĖą│ąĮą░ą╗čŗ čłąĖčĆąŠčéąĮąŠ-ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ ą╝ąŠą┤čāą╗čÅčåąĖąĖ (ą©ąśą£, pulse width modulation, PWM) ąĮą░ ąĮąŠąČą║ą░čģ ą┐ąŠčĆč鹊ą▓ GPIO. ąĀąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ čüč湥čéčćąĖą║ čü ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčīčÄ čüč湥čéą░ ą▓ą▓ąĄčĆčģ ąĖ ą▓ąĮąĖąĘ, čü 4 ą║ą░ąĮą░ą╗ą░ą╝ąĖ PWM, ą║ąŠč鹊čĆčŗąĄ čāą┐čĆą░ą▓ą╗čÅčÄčé ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╝ąĖ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ ą┐ąŠčĆč鹊ą▓ GPIO.

ąóčĆąĖ ą▒ą╗ąŠą║ą░ ą╝ąŠą┤čāą╗čÅ PWM ą╝ąŠą│čāčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą┤ąŠ 12 ą║ą░ąĮą░ą╗ąŠą▓ PWM čü ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ čćą░čüč鹊č鹊ą╣ ą▓ ą│čĆčāą┐ą┐ą░čģ, ą▓ ą║ąŠč鹊čĆčŗčģ ąĮą░čģąŠą┤čÅčéčüčÅ ą┤ąŠ 4 ą║ą░ąĮą░ą╗ąŠą▓. ąÜčĆąŠą╝ąĄ č鹊ą│ąŠ, ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą┤ąĄą║ąŠą┤ąĄčĆ ąĖ čäčāąĮą║čåąĖčÅ EasyDMA ą┤ąĄą╗ą░čÄčé ą▓ąŠąĘą╝ąŠąČąĮčŗą╝ ą╝ą░ąĮąĖą┐čāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ PWM ą▒ąĄąĘ ą▓ą╝ąĄčłą░č鹥ą╗čīčüčéą▓ą░ CPU. ą¤čĆąŠąĖąĘą▓ąŠą╗čīąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüą║ą▓ą░ąČąĮąŠčüč鹥ą╣ čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ąĖąĘ Data RAM, ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓čŗčüčéčĆąŠąĄąĮčŗ ą▓ čåąĄą┐ąŠčćą║čā, čćč鹊ą▒čŗ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░čéčī ą┤ą▓ąŠą╣ąĮčāčÄ ą▒čāč乥čĆąĖąĘą░čåąĖčÄ (ping-pong buffering) ąĖą╗ąĖ ą┐ąŠą▓č鹊čĆąĄąĮąĖąĄ čüą╗ąŠąČąĮčŗčģ čåąĖą║ą╗ąŠą▓ ąĖąĘ ą▒čāč乥čĆąŠą▓.

ą×čüąĮąŠą▓ąĮčŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą╝ąŠą┤čāą╗čÅ PWM:

ŌĆó ążąĖą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüč鹊čéą░ PWM čü ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╝ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓.

ŌĆó ąöąŠ 4 ą║ą░ąĮą░ą╗ąŠą▓ PWM čü ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ąĮą░čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓.

ŌĆó ążąŠčĆą╝ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮą░ ą║ą░ąĮą░ą╗ą░čģ PWM ąĖą╝ą┐čāą╗čīčüąŠą▓, ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗčģ ą┐ąŠ ąĮą░čćą░ą╗čā ą┐ąĄčĆąĖąŠą┤ą░ (edge aligned), ą╗ąĖą▒ąŠ čü ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗčģ čüąĖą╝ą╝ąĄčéčĆąĖčćąĮąŠ (center aligned).

ŌĆó ąØąĄčüą║ąŠą╗čīą║ąŠ ą╝ą░čüčüąĖą▓ąŠą▓ čüą║ą▓ą░ąČąĮąŠčüč鹥ą╣ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĖąĘ ą▒čāč乥čĆąŠą▓) ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ ą▓ Data RAM.

ŌĆó ąÉą▓č鹊ąĮąŠą╝ąĮąŠąĄ, ą▒ąĄąĘ ą┤čĆąŠąČą░ąĮąĖčÅ čäčĆąŠąĮč鹊ą▓ ąĖą╝ą┐čāą╗čīčüąŠą▓, ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ąĘąĮą░č湥ąĮąĖą╣ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ąĖąĘ ą┐ą░ą╝čÅčéąĖ čü ą┐ąŠą╝ąŠčēčīčÄ EasyDMA.

ŌĆó ąśąĘą╝ąĄąĮąĄąĮąĖąĄ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ, čüą║ą▓ą░ąČąĮąŠčüčéąĖ ąĖ ą▒ą░ąĘąŠą▓ąŠą╣ čćą░čüč鹊čéčŗ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ą▓ ą║ą░ąČą┤ąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ PWM.

ŌĆó ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĖąĘ Data RAM ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą▓č鹊čĆąĄąĮčŗ ąĖą╗ąĖ ąŠą▒čŖąĄą┤ąĖąĮąĄąĮčŗ ą▓ čåąĖą║ą╗čŗ.

ąĀąĖčü. 1. ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ čüčéčĆčāą║čéčāčĆą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą╝ąŠą┤čāą╗čÅ PWM.

[ąĪč湥čéčćąĖą║]

ąĪč湥čéčćąĖą║ PWM (wave counter) ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ą│ąĄąĮąĄčĆą░čåąĖčÄ ąĖą╝ą┐čāą╗čīčüąŠą▓ čüąŠ čüą║ą▓ą░ąČąĮąŠčüčéčīčÄ, ą║ąŠč鹊čĆą░čÅ ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĘąĮą░č湥ąĮąĖą╣ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (COMP0 .. COMP3) ąĖ ąŠčé čćą░čüč鹊čéčŗ PWM, ą║ąŠč鹊čĆą░čÅ ąĘą░ą▓ąĖčüąĖčé ąŠčé ą┐čĆąĄą┤ąĄą╗ą░ čüč湥čéą░ COUNTERTOP.

ąśą╝ąĄąĄčéčüčÅ ąŠą┤ąĖąĮ ąŠą▒čēąĖą╣ 15-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ čüč湥čéčćąĖą║ čü 4 ą║ą░ąĮą░ą╗ą░ą╝ąĖ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▓čüąĄ čŹčéąĖ 4 ą║ą░ąĮą░ą╗ą░ čĆą░ą▒ąŠčéą░čÄčé čü ąŠą▒čēąĖą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝ (ąĮą░ ąŠą▒čēąĄą╣ čćą░čüč鹊č鹥 PWM), ąŠą┤ąĮą░ą║ąŠ čā ą║ą░ąČą┤ąŠą│ąŠ ąĖąĘ ąĮąĖčģ ą╝ąŠąČąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčāčÄ čüą║ą▓ą░ąČąĮąŠčüčéčī ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ąĖą╝ą┐čāą╗čīčüąŠą▓ PWM. ą¤ąŠą╗čÅčĆąĮąŠčüčéčī čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝, ą┐čĆąŠčćąĖčéą░ąĮąĮčŗą╝ ąĖąĘ RAM (čüą╝. čĆąĖčü. 4), ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ čĆąĄą│ąĖčüčéčĆ MODE čāą┐čĆą░ą▓ą╗čÅąĄčé čĆąĄąČąĖą╝ąŠą╝ čüč湥čéą░ - ą╗ąĖą▒ąŠ čüč湥čé ą▓ą▓ąĄčĆčģ, ą╗ąĖą▒ąŠ čüč湥čé ą▓ą▓ąĄčĆčģ ąĖ ą▓ąĮąĖąĘ. ąÆąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüč湥čéą░ ąĘą░ą┤ą░ąĄčé čĆąĄą│ąĖčüčéčĆ COUNTERTOP. ąŚąĮą░č湥ąĮąĖąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą▓ą╝ąĄčüč鹥 čü ą▓čŗą▒čĆą░ąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ą┤ą╗čÅ PRESCALER čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ PWM_CLK ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą┐ąĄčĆąĖąŠą┤ PWM. ąŚąĮą░č湥ąĮąĖąĄ COUNTERTOP ą╝ąĄąĮčīčłąĄąĄ, č湥ą╝ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčéčüčāčéčüčéą▓ąĖčÄ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ PWM. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąĮą░ OUT[n] ą▒čāą┤ąĄčé čāą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą╗ąŠą│. 1, ąĄčüą╗ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ąĮą░ FallingEdge. ąÆčüąĄ čĆąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ, ąĖ ą╝ąŠą│čāčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ ą┤ąĄą║ąŠą┤ąĄčĆ, ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮčŗą╣ ą┤ą░ą╗ąĄąĄ.

ąĀąĄą│ąĖčüčéčĆ COUNTERTOP ą╝ąŠąČąĮąŠ ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ąĘą░ą┐ąĖčüą░čéčī ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ. ąĢą│ąŠ ąĘąĮą░č湥ąĮąĖąĄ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčéčüčÅ ąĖ čāčćąĖčéčŗą▓ą░ąĄčéčüčÅ čüčĆą░ąĘčā ą┐ąŠčüą╗ąĄ ąĘą░ą┤ą░čćąĖ ąĘą░ą┐čāčüą║ą░ (START task). ąĢčüą╗ąĖ ą▓ DECODER.LOAD ąĘą░ą┐ąĖčüą░ąĮąŠ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ąŠčéą╗ąĖčćą░čÄčēąĄąĄčüčÅ ąŠčé WaveForm, č鹊 COUNTERTOP čéą░ą║ąČąĄ ą▒čāą┤ąĄčé ą░ąĮą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąŠčüą╗ąĄ ąĘą░ą┤ą░čćąĖ STARTSEQ[n], ąĖ č鹊ą│ą┤ą░ ą▒čāą┤ąĄčé ąĘą░ą│čĆčāąČąĄąĮąŠ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ RAM ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüą║ą▓ą░ąČąĮąŠčüč鹥ą╣. ąĢčüą╗ąĖ DECODER.LOAD=WaveForm, č鹊 ąĘąĮą░č湥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░ COUNTERTOP ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ąĖ ą▓ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ RAM (čüą╝. ą┤ą░ą╗ąĄąĄ "ąöąĄą║ąŠą┤ąĄčĆ + EasyDMA").

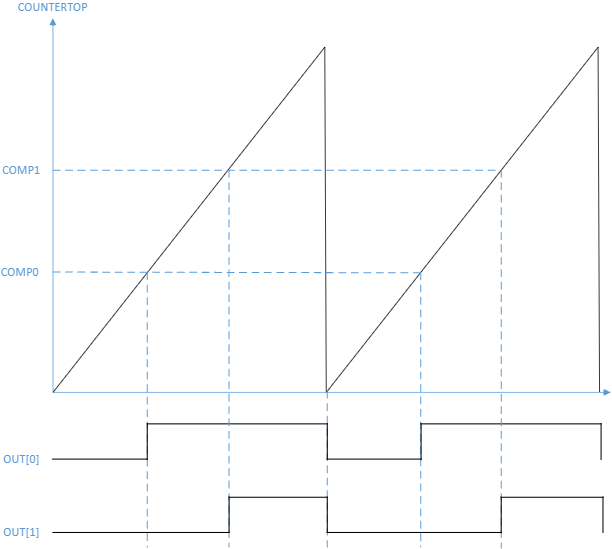

ąĀąĖčü. 2 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čĆą░ą▒ąŠčéčā čüč湥čéčćąĖą║ą░ ą▓ čĆąĄąČąĖą╝ąĄ čüč湥čéą░ ą▓ą▓ąĄčĆčģ (MODE=PWM_MODE_Up) čü čéčĆąĄą╝čÅ ą║ą░ąĮą░ą╗ą░ą╝ąĖ PWM, čĆą░ą▒ąŠčéą░čÄčēąĖą╝ąĖ ąĮą░ ąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥, ąĮąŠ čü čĆą░ąĘąĮčŗą╝ąĖ čüą║ą▓ą░ąČąĮąŠčüčéčÅą╝ąĖ. ąĪč湥čéčćąĖą║ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüą▒čĆą░čüčŗą▓ą░ąĄčéčüčÅ ą▓ 0, ą║ąŠą│ą┤ą░ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ COUNTERTOP, ąĖ čāčĆąŠą▓ąĄąĮčī ąĮą░ OUT[n] ą▒čāą┤ąĄčé ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░čéčīčüčÅ. OUT[n] čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 0, ąĄčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ 0, ąĖ čāą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą▓ ą╗ąŠą│. 1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ COUNTERTOP, ą║ąŠą│ą┤ą░ ą┐ąŠą╗čÅčĆąĮąŠčüčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą▓ FallingEdge. ąĀąĄąČąĖą╝ čüąŠ čüč湥č鹊ą╝ ą▓ą▓ąĄčĆčģ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĖą╝ą┐čāą╗čīčüčŗ ą©ąśą£ čü ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ ą┐ąŠ ąĮą░čćą░ą╗čā ą┐ąĄčĆąĖąŠą┤ą░ (PWM edge-aligned). ąØąĖąČąĄ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐čĆąĖą╝ąĄčĆ ą║ąŠą┤ą░:

uint16_t pwm_seq[4] = {PWM_CH0_DUTY, PWM_CH1_DUTY, PWM_CH2_DUTY, PWM_CH3_DUTY};

NRF_PWM0->PSEL.OUT[0] = (first_pin << PWM_PSEL_OUT_PIN_Pos) |

(PWM_PSEL_OUT_CONNECT_Connected <<

PWM_PSEL_OUT_CONNECT_Pos);

NRF_PWM0->PSEL.OUT[1] = (second_pin << PWM_PSEL_OUT_PIN_Pos) |

(PWM_PSEL_OUT_CONNECT_Connected <<

PWM_PSEL_OUT_CONNECT_Pos);

NRF_PWM0->ENABLE = (PWM_ENABLE_ENABLE_Enabled << PWM_ENABLE_ENABLE_Pos);

NRF_PWM0->MODE = (PWM_MODE_UPDOWN_Up << PWM_MODE_UPDOWN_Pos);

NRF_PWM0->PRESCALER = (PWM_PRESCALER_PRESCALER_DIV_1 <<

PWM_PRESCALER_PRESCALER_Pos);

NRF_PWM0->COUNTERTOP = (16000 << PWM_COUNTERTOP_COUNTERTOP_Pos); //1 msec

NRF_PWM0->LOOP = (PWM_LOOP_CNT_Disabled << PWM_LOOP_CNT_Pos);

NRF_PWM0->DECODER = (PWM_DECODER_LOAD_Individual << PWM_DECODER_LOAD_Pos) |

(PWM_DECODER_MODE_RefreshCount << PWM_DECODER_MODE_Pos);

NRF_PWM0->SEQ[0].PTR = ((uint32_t)(pwm_seq) << PWM_SEQ_PTR_PTR_Pos);

NRF_PWM0->SEQ[0].CNT = ((sizeof(pwm_seq) / sizeof(uint16_t)) <<

PWM_SEQ_CNT_CNT_Pos);

NRF_PWM0->SEQ[0].REFRESH = 0;

NRF_PWM0->SEQ[0].ENDDELAY = 0;

NRF_PWM0->TASKS_SEQSTART[0] = 1;

ąĀąĖčü. 2. ą¤čĆąĖą╝ąĄčĆ PWM čüąŠ čüč湥č鹊ą╝ ą▓ą▓ąĄčĆčģ, ą┐ąŠą╗čÅčĆąĮąŠčüčéčī FallingEdge.

ąöą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ PWM TPWM(Up) ąĖ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ Tsteps ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č乊čĆą╝čāą╗čŗ:

TPWM(Up) = TPWM_CLK * COUNTERTOP

Tsteps = TPWM_CLK

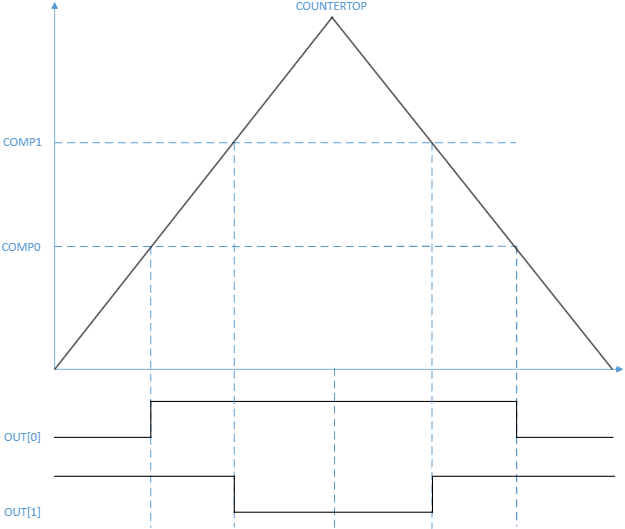

ąØą░ čĆąĖčü. 3 ą┐ąŠą║ą░ąĘą░ąĮ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ čüčćąĖčéą░ąĄčé ą▓ą▓ąĄčĆčģ ąĖ ą▓ąĮąĖąĘ (ąŠčé ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ ąŠčéą╗ąĖčćą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ MODE=PWM_MODE_UpAndDown), čü ą┤ą▓čāą╝čÅ ą║ą░ąĮą░ą╗ą░ą╝ąĖ PWM, čĆą░ą▒ąŠčéą░čÄčēąĖą╝ąĖ ąĮą░ ąŠą┤ąĮąŠą╣ čćą░čüč鹊č鹥, ąĮąŠ čü čĆą░ąĘąĮčŗą╝ąĖ čüą║ą▓ą░ąČąĮąŠčüčéčÅą╝ąĖ ąĖ ą┐ąŠą╗čÅčĆąĮąŠčüčéčīčÄ ąĖą╝ą┐čāą╗čīčüąŠą▓. ąĪč湥čéčćąĖą║ ąĮą░čćąĖąĮą░ąĄčé ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ąŠ 0, ą║ąŠą│ą┤ą░ ą┐čĆąĖ čüč湥č鹥 ą▓ą▓ąĄčĆčģ ą┤ąŠčüčéąĖą│ąĮčāč鹊 ąĘąĮą░č湥ąĮąĖąĄ COUNTERTOP, ąĖ ąĖąĮą▓ąĄčĆčéąĖčĆčāąĄčéčüčÅ OUT[n], ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┤ąŠčüčéąĖą│ąĮčāč鹊 ą▓č鹊čĆąŠą╣ čĆą░ąĘ. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┐ąŠą╗čāčćą░čÄčéčüčÅ ąĖą╝ą┐čāą╗čīčüčŗ PWM, ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą║ąŠč鹊čĆčŗčģ ą╝ąĄąĮčÅąĄčéčüčÅ čü ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ (PWM center-aligned).

uint16_t pwm_seq[4] = {PWM_CH0_DUTY, PWM_CH1_DUTY, PWM_CH2_DUTY, PWM_CH3_DUTY};

NRF_PWM0->PSEL.OUT[0] = (first_pin << PWM_PSEL_OUT_PIN_Pos) |

(PWM_PSEL_OUT_CONNECT_Connected <<

PWM_PSEL_OUT_CONNECT_Pos);

NRF_PWM0->PSEL.OUT[1] = (second_pin << PWM_PSEL_OUT_PIN_Pos) |

(PWM_PSEL_OUT_CONNECT_Connected <<

PWM_PSEL_OUT_CONNECT_Pos);

NRF_PWM0->ENABLE = (PWM_ENABLE_ENABLE_Enabled << PWM_ENABLE_ENABLE_Pos);

NRF_PWM0->MODE = (PWM_MODE_UPDOWN_UpAndDown << PWM_MODE_UPDOWN_Pos);

NRF_PWM0->PRESCALER = (PWM_PRESCALER_PRESCALER_DIV_1 <<

PWM_PRESCALER_PRESCALER_Pos);

NRF_PWM0->COUNTERTOP = (16000 << PWM_COUNTERTOP_COUNTERTOP_Pos); //1 msec

NRF_PWM0->LOOP = (PWM_LOOP_CNT_Disabled << PWM_LOOP_CNT_Pos);

NRF_PWM0->DECODER = (PWM_DECODER_LOAD_Individual << PWM_DECODER_LOAD_Pos) |

(PWM_DECODER_MODE_RefreshCount << PWM_DECODER_MODE_Pos);

NRF_PWM0->SEQ[0].PTR = ((uint32_t)(pwm_seq) << PWM_SEQ_PTR_PTR_Pos);

NRF_PWM0->SEQ[0].CNT = ((sizeof(pwm_seq) / sizeof(uint16_t)) <<

PWM_SEQ_CNT_CNT_Pos);

NRF_PWM0->SEQ[0].REFRESH = 0;

NRF_PWM0->SEQ[0].ENDDELAY = 0;

NRF_PWM0->TASKS_SEQSTART[0] = 1;

ąĀąĖčü. 3. ą¤čĆąĖą╝ąĄčĆ PWM čüąŠ čüč湥č鹊ą╝ ą▓ą▓ąĄčĆčģ/ą▓ąĮąĖąĘ.

ąÆ čĆąĄąČąĖą╝ąĄ čüč湥čéą░ ą▓ą▓ąĄčĆčģ/ą▓ąĮąĖąĘ ą┤ą╗čÅ ą▓čŗčćąĖčüą╗ąĄąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ą░ PWM TPWM(Up And Down) ąĖ čĆą░ąĘčĆąĄčłą░čÄčēąĄą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ą┐ąŠ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ Tsteps ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č乊čĆą╝čāą╗čŗ:

TPWM(Up And Down) = TPWM_CLK * 2 * COUNTERTOP

Tsteps = TPWM_CLK * 2

[ąöąĄą║ąŠą┤ąĄčĆ + EasyDMA]

ąöąĄą║ąŠą┤ąĄčĆ ąĖčüą┐ąŠą╗čīąĘčāąĄčé EasyDMA ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ PWM, čüąŠčģčĆą░ąĮąĄąĮąĮčŗčģ ą▓ Data RAM, ąĖ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, ąŠčüąĮąŠą▓čŗą▓ą░čÅčüčī ąĮą░ čĆąĄąČąĖą╝ąĄ čĆą░ą▒ąŠčéčŗ.

ąŻą┐ąŠą╝čÅąĮčāčéčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ PWM ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī, čüąŠą┤ąĄčƹȹ░čēčāčÄ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ą┐ąŠą╗ąŠą▓ąĖąĮčā čüą╗ąŠą▓ą░ (16 ą▒ąĖčé). ąĪą░ą╝čŗą╣ čüčéą░čĆčłąĖą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé ąĘą┤ąĄčüčī (MSB, bit[15]) ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčī OUT[n], ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ ąŠčüčéą░ą╗čīąĮčŗąĄ bit[14:0] ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄčé čüąŠą▒ąŠą╣ 15-čĆą░ąĘčĆčÅą┤ąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ čüčĆą░ą▓ąĮąĄąĮąĖčÅ:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

COMPARE |

ąØą░čüčéčĆąŠą╣ą║ą░ čüą║ą▓ą░ąČąĮąŠčüčéąĖ - ąĘąĮą░č湥ąĮąĖąĄ, ąĘą░ą│čĆčāąČą░ąĄą╝ąŠąĄ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. |

| B |

RW |

POLARITY |

ąŻčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąŠą╗čÅčĆąĮąŠčüčéčī ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ PWM ąĮą░ ą▓čŗčģąŠą┤ąĄ.

0: RisingEdge, ą┐ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▓ ą┐ąĄčĆąĖąŠą┤ąĄ ąĖą╝ą┐čāą╗čīčüąŠą▓ - ąĮą░čĆą░čüčéą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ (0 -> 1).

1: FallingEdge, ą┐ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĄą┐ą░ą┤ ą▓ ą┐ąĄčĆąĖąŠą┤ąĄ ąĖą╝ą┐čāą╗čīčüąŠą▓ - čüą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ (1 -> 0). |

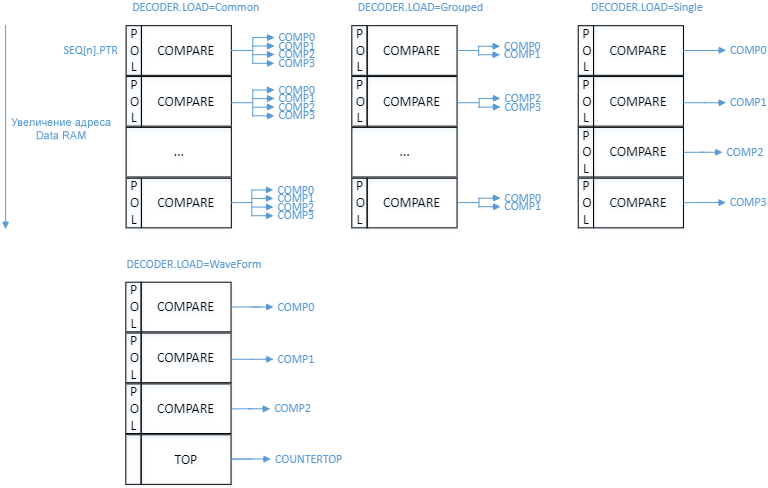

ąĀąĄą│ąĖčüčéčĆ DECODER čāą┐čĆą░ą▓ą╗čÅąĄčé, ą║ą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ RAM ąĖąĮč鹥čĆą┐čĆąĄčéąĖčĆčāąĄčéčüčÅ ąĖ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. ą¤ąŠą╗ąĄ LOAD ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĘą░ą│čĆčāąĘą║ąŠą╣ - ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą╗ąĖ ąĘąĮą░č湥ąĮąĖčÅ RAM ą▓ąŠ ą▓čüąĄ ą║ą░ąĮą░ą╗čŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, ąĖą╗ąĖ ąČąĄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠ ą▒čāą┤ąĄčé ąŠą▒ąĮąŠą▓ą╗čÅčéčīčüčÅ ą│čĆčāą┐ą┐ą░, ą╗ąĖą▒ąŠ ą▓čüąĄ ą║ą░ąĮą░ą╗čŗ ą▒čāą┤čāčé ąŠą▒ąĮąŠą▓ą╗čÅčéčīčüčÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčŗą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ. ąĀąĖčü. 4 ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé, ą║ą░ą║ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮčŗ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗąĄ ą▓ RAM, ąĖ ą║ą░ą║ ąŠąĮąĖ ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą▓ čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą║ą░ąĮą░ą╗čŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą▓ čĆą░ąĘąĮčŗčģ čĆąĄąČąĖą╝ą░čģ.

ąĀąĖčü. 4. ąĀąĄąČąĖą╝čŗ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ čüąŠ čüč鹊čĆąŠąĮčŗ ą┤ąĄą║ąŠą┤ąĄčĆą░.

ąöąŠčüčéčāą┐ąĄąĮ čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ, ą║ąŠą│ą┤ą░ DECODER.LOAD čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ WaveForm. ąÆ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą╝ąŠąČąĮąŠ čĆą░ąĘčĆąĄčłąĖčéčī ą┤ąŠ 3 ą║ą░ąĮą░ą╗ąŠą▓ PWM - OUT[0], OUT[1] ąĖ OUT[2]. ąÆ RAM ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ąĘą░ ąŠą┤ąĖąĮ čĆą░ąĘ 4 ąĘąĮą░č湥ąĮąĖčÅ: ą┐ąĄčĆą▓ą░čÅ, ą▓č鹊čĆą░čÅ ąĖ čéčĆąĄčéčīčÅ čÅč湥ą╣ą║ąĖ RAM ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ąĘąĮą░č湥ąĮąĖą╣ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ, ąĖ č湥čéą▓ąĄčĆčéą░čÅ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ čĆąĄą│ąĖčüčéčĆą░ COUNTERTOP. ąŁč鹊 ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠ 3 ą║ą░ąĮą░ą╗ąŠą▓ PWM, ą┐čĆąĖ ą║ąŠč鹊čĆąŠą╝ ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüč鹊čéą░ PWM. ąŁč鹊čé čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ ą┐ąŠą╗ąĄąĘąĄąĮ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ąŠą▓ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą╣ č乊čĆą╝čŗ ą▓ čéą░ą║ąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą║ą░ą║ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąĮąŠąĄ ąŠčüą▓ąĄčēąĄąĮąĖąĄ.

ąĀąĄą│ąĖčüčéčĆ SEQ[n].REFRESH=N (ąŠą┤ąĖąĮ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī n=0 ąĖą╗ąĖ 1) ą▒čāą┤ąĄčé ąĖąĮčüčéčĆčāą║čéąĖčĆąŠą▓ą░čéčī ąŠ ąĮąŠą▓ąŠą╣ ą▓ąĄą╗ąĖčćąĖąĮąĄ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą╣ ą▓ RAM, ąĮą░ ą║ą░ąČą┤ąŠą╝ (N+1)-ąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ PWM. ąŻčüčéą░ąĮąŠą▓ą║ą░ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą▓ 0 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĮąŠą▓ąŠą╣ čüą╝ąĄąĮąĄ čĆą░ą▒ąŠč湥ą│ąŠ čåąĖą║ą╗ą░ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ PWM ą┤ąŠ č鹥čģ ą┐ąŠčĆ, ą┐ąŠą║ą░ ąĮą░ą▒ą╗čÄą┤ą░ąĄčéčüčÅ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ ą┐ąĄčĆąĖąŠą┤ PWM.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čĆąĄą│ąĖčüčéčĆčŗ SEQ[n].REFRESH ąĖ SEQ[n].ENDDELAY ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ, ą║ąŠą│ą┤ą░ DECODER.MODE=NextStep. ąĪą╗ąĄą┤čāčÄčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ą┐čĆąĖ ą┐ąŠą╗čāč湥ąĮąĖąĖ ą║ą░ąČą┤ąŠą╣ ąĮąŠą▓ąŠą╣ ąĘą░ą┤ą░čćąĖ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čłą░ą│ą░ (NEXTSTEP task).

SEQ[n].PTR čŹč鹊 čāą║ą░ąĘą░č鹥ą╗čī, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą║ąĖ ąĘąĮą░č湥ąĮąĖą╣ COMPARE ąĖąĘ RAM. ąĢčüą╗ąĖ SEQ[n].PTR ąĮąĄ čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ąŠą▒ą╗ą░čüčéčī Data RAM, č鹊 čéčĆą░ąĮąĘą░ą║čåąĖčÅ EasyDMA ą╝ąŠąČąĄčé ą▓čŗąĘą▓ą░čéčī HardFault ąĖą╗ąĖ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠą│ąŠ RAM. ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ čĆą░ąĘąĮčŗą╝ čĆąĄą│ąĖąŠąĮą░ą╝ ą┐ą░ą╝čÅčéąĖ čüą╝. [2].

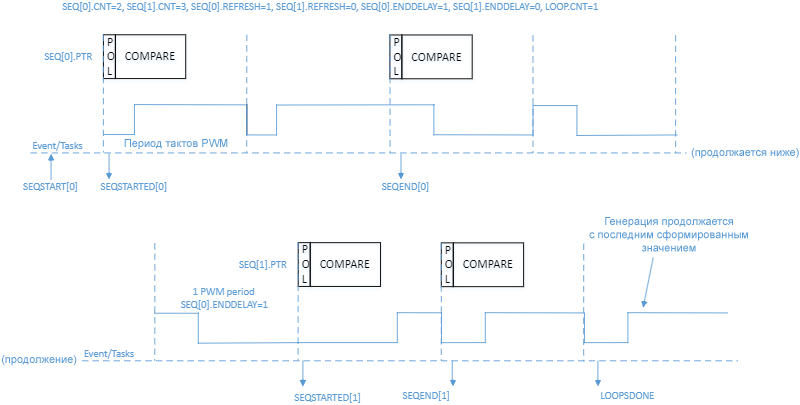

ą¤ąŠčüą╗ąĄ čāčüčéą░ąĮąŠą▓ą║ąĖ čāą║ą░ąĘą░č鹥ą╗čÅ SEQ[n].PTR ąĮą░ ąČąĄą╗ą░ąĄą╝čāčÄ ąŠą▒ą╗ą░čüčéčī RAM, ą▓ čĆąĄą│ąĖčüčéčĆąĄ SEQ[n].CNT ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąŠą╗ąŠą▓ąĖąĮąŠą║ čüą╗ąŠą▓ (ą┐ąŠčĆčåąĖą╣ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ 16-ą▒ąĖčé), ąĮą░čģąŠą┤čÅčēąĖčģčüčÅ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ. ąÆą░ąČąĮąŠ ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 čĆąĄąČąĖą╝čŗ Grouped ąĖ Single čéčĆąĄą▒čāčÄčé ąŠą┤ąĮčā ą┐ąŠą╗ąŠą▓ąĖąĮą║čā čüą╗ąŠą▓ą░ ąĮą░ ą│čĆčāą┐ą┐čā, ą╗ąĖą▒ąŠ ą╗ąĖą▒ąŠ ąŠą┤ąĮčā ą┐ąŠą╗ąŠą▓ąĖąĮą║čā čüą╗ąŠą▓ą░ ąĮą░ ą║ą░ąĮą░ą╗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ, čćč鹊 čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčé čĆą░čüčģąŠą┤ RAM. ąĢčüą╗ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą│ąĄąĮąĄčĆą░čåąĖčÅ PWM ąĄčēąĄ ąĮąĄ ąĘą░ą┐čāčēąĄąĮą░, ąŠčéą┐čĆą░ą▓ą║ą░ SEQSTART[n] task ąĘą░ą│čĆčāąĘąĖčé ą┐ąĄčĆą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ RAM, ąĘą░č鹥ą╝ ąĘą░ą┐čāčüčéąĖčé ą│ąĄąĮąĄčĆą░čåąĖčÄ PWM. ąæčāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ čüąŠą▒čŗčéąĖąĄ SEQSTARTED[n], ą║ą░ą║ č鹊ą╗čīą║ąŠ EasyDMA ą┐čĆąŠčćąĖčéą░ą╗ ą┐ąĄčĆą▓čŗą╣ ą┐ą░čĆą░ą╝ąĄčéčĆ PWM ąĖąĘ RAM, ąĖ čüč湥čéčćąĖą║ ąĮą░čćą░ą╗ ąĄą│ąŠ ą▓čŗą┐ąŠą╗ąĮčÅčéčī. ąÜąŠą│ą┤ą░ LOOP.CNT=0, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī n=0 ąĖą╗ąĖ 1 ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĄčéčüčÅ ąŠą┤ąĖąĮ čĆą░ąĘ. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąČąĄąĮąŠ ąĖ ąĘą░ą┐čāčēąĄąĮąŠ ąĮą░ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖąĄ, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄ SEQEND[n]. ąōąĄąĮąĄčĆą░čåąĖčÅ The PWM ą┐čĆąŠą┤ąŠą╗ąČąĖčéčüčÅ čü ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ąĘą░ą│čĆčāąČąĄąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝. ąĪą╝. čĆąĖčü. 5 ą┤ą╗čÅ ą┐čĆąĖą╝ąĄčĆą░ čéą░ą║ąŠą│ąŠ ą┐čĆąŠčüč鹊ą│ąŠ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÅ.

ą¦č鹊ą▒čŗ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠčüčéą░ąĮąŠą▓ąĖčéčī ą│ąĄąĮąĄčĆą░čåąĖčÄ PWM ąĖ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ąĮąŠąČą║ąĖ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ą╝ąŠąČąĮąŠ ą▓ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ąĘą░ą┐čāčüčéąĖčéčī STOP task. ąĪą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄ STOPPED, ą│ąŠą┤ą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ PWM ąŠčüčéą░ąĮąŠą▓ąĖą╗ą░čüčī ą▓ ą║ąŠąĮčåąĄ č鹥ą║čāčēąĄą│ąŠ č乊čĆą╝ąĖčĆčāąĄą╝ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ PWM, ąĖ ąĮąŠąČą║ąĖ ą┐ąĄčĆąĄą╣ą┤čāčé ą▓ čüąŠčüč鹊čÅąĮąĖąĄ ąŠąČąĖą┤ą░ąĮąĖčÅ, ą║ą░ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ GPIO->OUT. ąŚą░č鹥ą╝ ą│ąĄąĮąĄčĆą░čåąĖčÅ PWM ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čāčēąĄąĮą░ ąĘą░ąĮąŠą▓ąŠ ą▓čŗą┤ą░č湥ą╣ SEQSTART[n] task. SEQSTART[n] ą▓ąŠąĘąŠą▒ąĮąŠą▓ąĖčé ą│ąĄąĮąĄčĆą░čåąĖčÄ PWM ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą│čĆčāąĘąĖčéčüčÅ ą┐ąĄčĆą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ ą▒čāč乥čĆą░ RAM, ą║ąŠč鹊čĆčŗą╣ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ čĆąĄą│ąĖčüčéčĆąŠą╝ SEQ[n].PTR.

ąÆ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ąŠą│ą┤ą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ. ąĪą╗ąĄą┤čāąĄčé ą┐čĆąŠčÅą▓ą╗čÅčéčī ąŠčüč鹊čĆąŠąČąĮąŠčüčéčī, ą║ąŠą│ą┤ą░ ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī čüąĖčéčāą░čåąĖąĖ, ą║ąŠą│ą┤ą░ ąĘąĮą░č湥ąĮąĖčÅ ą┐čĆąĖą╝ąĄąĮčÅčÄčéčüčÅ čĆą░ąĮčīčłąĄ, č湥ą╝ čŹč鹊 ąŠąČąĖą┤ą░ą╗ąŠčüčī.

ąóą░ą▒ą╗ąĖčåą░ 1. ąÜąŠą│ą┤ą░ ą╝ąŠąČąĮąŠ ą▒ąĄąĘąŠą┐ą░čüąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī čĆąĄą│ąĖčüčéčĆčŗ PWM.

| ąĀąĄą│ąĖčüčéčĆ |

ąŻčćąĖčéčŗą▓ą░ąĄčéčüčÅ ą▓ ą░ą┐ą┐ą░čĆą░čéčāčĆąĄ |

ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝čŗą╣ (ą▒ąĄąĘąŠą┐ą░čüąĮčŗą╣) ą╝ąŠą╝ąĄąĮčé ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ |

| SEQ[n].PTR |

ąÜąŠą│ą┤ą░ ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ SEQSTART[n] task. |

ą¤ąŠčüą╗ąĄ ą┐ąŠą╗čāč湥ąĮąĖčÅ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[n]. |

| SEQ[n].CNT |

| SEQ[0].ENDDELAY |

ąÜąŠą│ą┤ą░ ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ SEQSTART[0] task.

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0 ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąČąĄąĮąŠ ąĖąĘ RAM, ąĖ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 Wave Counter (ąĖąĮą┤ąĖčåąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ PWMPERIODEND). |

ą¤ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0 ą┐čāč鹥ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ SEQSTART[0] task.

ąÜąŠą│ą┤ą░ ą▒ąŠą╗čīčłąĄ ąĮąĄčé ąĘąĮą░č湥ąĮąĖą╣ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮčŗ ąĖąĘ RAM (ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ SEQEND[0]).

ąÆ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 1 (ą║ąŠč鹊čĆą░čÅ čüčéą░čĆčéčāąĄčé, ą║ąŠą│ą┤ą░ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ čüąŠą▒čŗčéąĖąĄ SEQSTARTED[1]). |

| SEQ[1].ENDDELAY |

ąÜąŠą│ą┤ą░ ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ SEQSTART[1] task.

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1 ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąČąĄąĮąŠ ąĖąĘ RAM, ąĖ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 Wave Counter (ąĖąĮą┤ąĖčåąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ PWMPERIODEND). |

ą¤ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1 ą┐čāč鹥ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ SEQSTART[1] task.

ąÜąŠą│ą┤ą░ ą▒ąŠą╗čīčłąĄ ąĮąĄčé ąĘąĮą░č湥ąĮąĖą╣ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮčŗ ąĖąĘ RAM (ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ SEQEND[1]).

ąÆ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 0 (ą║ąŠč鹊čĆą░čÅ čüčéą░čĆčéčāąĄčé, ą║ąŠą│ą┤ą░ čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąŠ čüąŠą▒čŗčéąĖąĄ SEQSTARTED[0]). |

| SEQ[0].REFRESH |

ąÜąŠą│ą┤ą░ ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ SEQSTART[0] task. |

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0 ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąČąĄąĮąŠ ąĖąĘ RAM, ąĖ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 Wave Counter (ąĖąĮą┤ąĖčåąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ PWMPERIODEND).

ą¤ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0 ą┐čāč鹥ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ SEQSTART[0] task.

ąÆ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 1 (ą║ąŠč鹊čĆą░čÅ čüčéą░čĆčéčāąĄčé ą┐čĆąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[1]). |

| SEQ[1].REFRESH |

ąÜąŠą│ą┤ą░ ą┐ąŠčüčŗą╗ą░ąĄčéčüčÅ SEQSTART[1] task. |

ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1 ą▒čŗą╗ąŠ ąĘą░ą│čĆčāąČąĄąĮąŠ ąĖąĘ RAM, ąĖ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 Wave Counter (ąĖąĮą┤ąĖčåąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ PWMPERIODEND).

ą¤ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1 ą┐čāč鹥ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ SEQSTART[1] task.

ąÆ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠą│ą┤ą░ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 0 (ą║ąŠč鹊čĆą░čÅ čüčéą░čĆčéčāąĄčé ą┐čĆąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[0]). |

| COUNTERTOP |

ą¤čĆąĖ DECODER.LOAD=WaveForm čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ.

ąÆąŠ ą▓čüąĄčģ ą┤čĆčāą│ąĖčģ čĆąĄąČąĖą╝ą░čģ LOAD: ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ PWM (ąĖąĮą┤ąĖčåąĖčĆčāąĄčéčüčÅ čüąŠą▒čŗčéąĖąĄą╝ PWMPERIODEND). |

ą¤ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ PWM ą┐čāč鹥ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ SEQSTART[n] task.

ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čŗą╗ą░ ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░ąĮą░ STOP task, ąĖ ą║ąŠą│ą┤ą░ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 čüąŠą▒čŗčéąĖąĄ STOPPED. |

| MODE |

ąØąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ |

| DECODER |

| PRESCALER |

| LOOP |

| PSEL.OUT[n] |

ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ: SEQ[n].REFRESH ąĖ SEQ[n].ENDDELAY ąĖą│ąĮąŠčĆąĖčĆčāčÄčéčüčÅ ą▓ ą║ąŠąĮčåąĄ čüą╗ąŠąČąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, ąŠ č湥ą╝ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠą▒čŗčéąĖąĄ LOOPSDONE. ą¤čĆąĖčćąĖąĮą░ čŹč鹊ą│ąŠ ą▓ č鹊ą╝, čćč鹊 ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ ąĘą░ą│čĆčāąČąĄąĮąĮąŠąĄ ąĖąĘ RAM ąĘąĮą░č湥ąĮąĖąĄ ąŠčüčéą░ąĄčéčüčÅ ą┤ąĄą╣čüčéą▓čāčÄčēąĖą╝, ą┐ąŠą║ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ąĮąĄ ą┐čĆąĄą┤ą┐čĆąĖą╝ąĄčé ą┤ą░ą╗čīąĮąĄą╣čłąĖąĄ ą┤ąĄą╣čüčéą▓ąĖčÅ (ą┐ąŠą║ą░ ąĮąĄ ą┐ąĄčĆąĄąĘą░ą┐čāčüčéąĖčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī, ą╗ąĖą▒ąŠ ąĮąĄ ąŠčüčéą░ąĮąŠą▓ąĖčé ą│ąĄąĮąĄčĆą░čåąĖčÄ PWM).

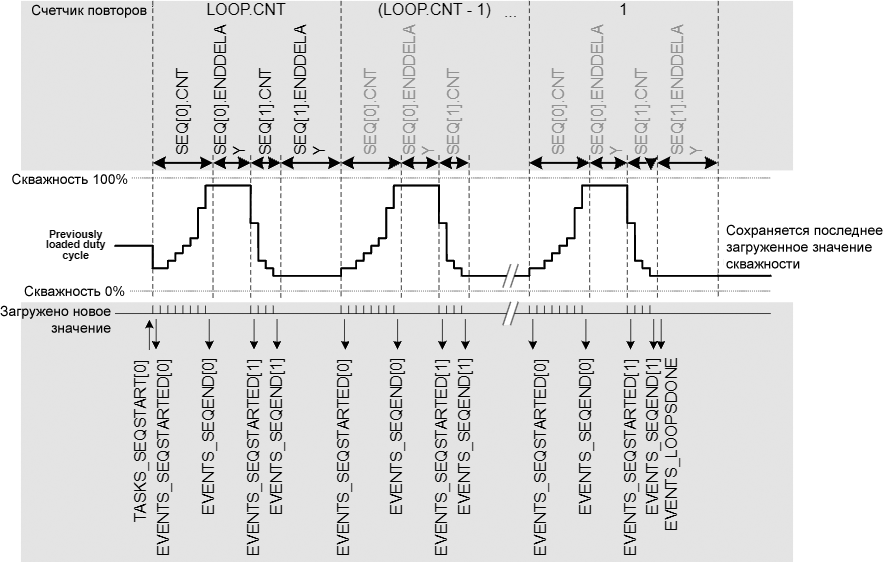

ąØą░ čĆąĖčü. 5 ą┐ąŠą║ą░ąĘą░ąĮą░ čĆą░ą▒ąŠčéą░ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ą║ąŠą┤ą░, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą┤ą╗čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ, ą│ą┤ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 0, ąĖ ąŠąĮą░ ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆą░ąĘ čü ąĮąŠą▓čŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ čüą║ą▓ą░ąČąĮąŠčüčéąĖ PWM ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░.

NRF_PWM0->PSEL.OUT[0] = (first_pin << PWM_PSEL_OUT_PIN_Pos) |

(PWM_PSEL_OUT_CONNECT_Connected <<

PWM_PSEL_OUT_CONNECT_Pos);

NRF_PWM0->ENABLE = (PWM_ENABLE_ENABLE_Enabled << PWM_ENABLE_ENABLE_Pos);

NRF_PWM0->MODE = (PWM_MODE_UPDOWN_Up << PWM_MODE_UPDOWN_Pos);

NRF_PWM0->PRESCALER = (PWM_PRESCALER_PRESCALER_DIV_1 <<

PWM_PRESCALER_PRESCALER_Pos);

NRF_PWM0->COUNTERTOP = (16000 << PWM_COUNTERTOP_COUNTERTOP_Pos); //1 msec

NRF_PWM0->LOOP = (PWM_LOOP_CNT_Disabled << PWM_LOOP_CNT_Pos);

NRF_PWM0->DECODER = (PWM_DECODER_LOAD_Common << PWM_DECODER_LOAD_Pos) |

(PWM_DECODER_MODE_RefreshCount << PWM_DECODER_MODE_Pos);

NRF_PWM0->SEQ[0].PTR = ((uint32_t)(seq0_ram) << PWM_SEQ_PTR_PTR_Pos);

NRF_PWM0->SEQ[0].CNT = ((sizeof(seq0_ram) / sizeof(uint16_t)) <<

PWM_SEQ_CNT_CNT_Pos);

NRF_PWM0->SEQ[0].REFRESH = 0;

NRF_PWM0->SEQ[0].ENDDELAY = 0;

NRF_PWM0->TASKS_SEQSTART[0] = 1;

ąĀąĖčü. 5. ą¤čĆąĖą╝ąĄčĆ ąĘą░ą┐čāčüą║ą░ ą┐čĆąŠčüč鹊ą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ.

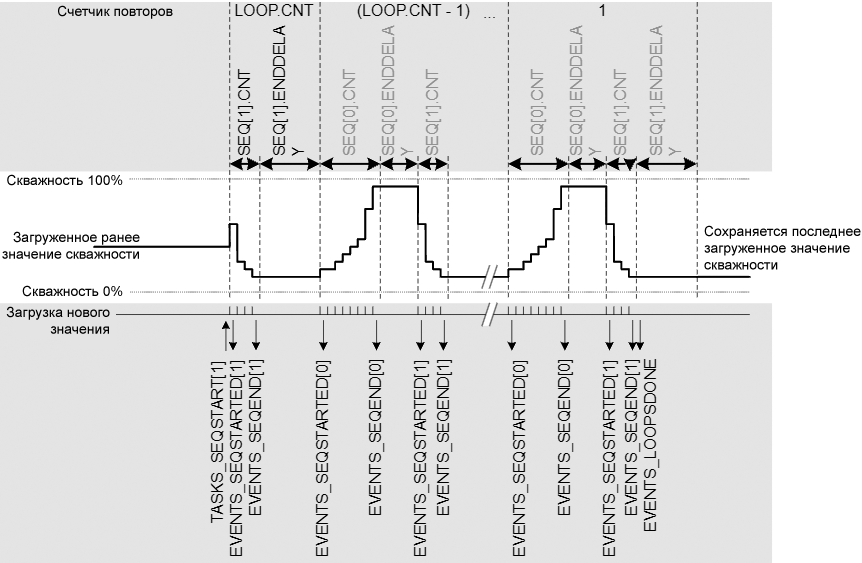

ąæąŠą╗ąĄąĄ čüą╗ąŠąČąĮčŗą╣ ą┐čĆąĖą╝ąĄčĆ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 6, ą│ą┤ąĄ LOOP.CNT > 0 . ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠąĄ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖąĄ, čüąŠčüč鹊čÅčēąĄąĄ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ SEQ[0], ąĘą░ą┤ąĄčƹȹ║ąĖ delay 0, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ SEQ[1], ąĘą░ą┤ąĄčƹȹ║ąĖ delay 1, ąĖ ąĘą░č鹥ą╝ čüąĮąŠą▓ą░ ą┐ąŠ ą║čĆčāą│čā SEQ[0], ąĖ čéą░ą║ ą┤ą░ą╗ąĄąĄ. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī ą╝ąŠąČąĄčé ą▓čŗą▒čĆą░čéčī ąĘą░ą┐čāčüą║ čüą╗ąŠąČąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čü SEQ[0] ąĖą╗ąĖ SEQ[1] ą┐čāč鹥ą╝ ą░ą║čéąĖą▓ą░čåąĖąĖ ą╗ąĖą▒ąŠ SEQSTART[0], ą╗ąĖą▒ąŠ SEQSTART[1] task.

ąĪą╗ąŠąČąĮąŠąĄ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖąĄ ą▓čüąĄą│ą┤ą░ ąĘą░ą▓ąĄčĆčłą░ąĄčéčüčÅ čü delay 1.

ąöą▓ąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0 ąĖ 1 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą░ą┤čĆąĄčüą░ą╝ąĖ čéą░ą▒ą╗ąĖčå ąĘąĮą░č湥ąĮąĖą╣ ą▓ Data RAM (čāą║ą░ąĘčŗą▓ą░čÄčéčüčÅ SEQ[n].PTR) ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ąĖ čĆą░ąĘą╝ąĄčĆą░ą╝ąĖ ą▒čāč乥čĆą░ (SEQ[n].CNT). ąĪą║ąŠčĆąŠčüčéčī, čü ą║ąŠč鹊čĆąŠą╣ ąĮąŠą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ, ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ č湥čĆąĄąĘ SEQ[n].REFRESH. ą¤ąĄčĆąĄčģąŠą┤ ąŠčé ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1 ą║ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0 ąĮąĄčÅą▓ąĮčŗą╣, čĆąĄą│ąĖčüčéčĆ LOOP.CNT ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĘą░ą┤ą░čéčī ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║ąĖčģ ą┐ąĄčĆąĄčģąŠą┤ąŠą▓ (ą┐ąŠą▓č鹊čĆąĮčŗčģ ąĘą░ą┐čāčüą║ąŠą▓). ąöčĆčāą│ąĖą╝ąĖ čüą╗ąŠą▓ą░ą╝ąĖ, LOOP.CNT ąĘą░ą┤ą░ąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖčģ ą┐ąŠą▓č鹊čĆąŠą▓ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÅ čüą╗ąŠąČąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ.

ąÆ ą┐čĆąĖą╝ąĄčĆąĄ ąĮąĖąČąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī 0 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ čü SEQ[0].REFRESH, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▓ 1 - čŹč鹊 ąĘąĮą░čćąĖčé, čćč鹊 ąĮąŠą▓čŗą╣ čåąĖą║ą╗ čüą║ą▓ą░ąČąĮąŠčüčéąĖ PWM ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ąĮą░ ą║ą░ąČą┤ąŠą╝ ą▓č鹊čĆąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ PWM. ąŁčéą░ čüą╗ąŠąČąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą░ą║čéąĖą▓ą░čåąĖąĄą╣ SEQSTART[0], ą┐ąŠčŹč鹊ą╝čā čüąĮą░čćą░ą╗ą░ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĄčéčüčÅ SEQ[0]. ą¤ąŠčüą║ąŠą╗čīą║čā SEQ[0].ENDDELAY=1, ąĘą┤ąĄčüčī ą▒čāą┤ąĄčé ąĘą░ą┤ąĄčƹȹ║ą░ ąĮą░ 1 ą┐ąĄčĆąĖąŠą┤ PWM ą╝ąĄąČą┤čā ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0 ąĖ ą┐ąĄčĆą▓čŗą╝ ą┐ąĄčĆąĖąŠą┤ąŠą╝ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1. ą¤ąŠčüą║ąŠą╗čīą║čā SEQ[1].ENDDELAY=0, ąĘą┤ąĄčüčī ąĮąĄčé ąĘą░ą┤ąĄčƹȹ║ąĖ delay 1, čéą░ą║ čćč鹊 SEQ[0] ąĘą░ą┐čāčüčéąĖčéčüčÅ čüčĆą░ąĘčā ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ SEQ[1]. ą×ą┤ąĮą░ą║ąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā LOOP.CNT = 1, ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖąĄ ąŠčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą│ąŠ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÅ SEQ[1], ąĖ čüą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ąŠą▒ą░ čüąŠą▒čŗčéąĖčÅ SEQEND[1] ąĖ LOOPSDONE (ą▓ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą┐ąŠčĆčÅą┤ąŠą║ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ čŹčéąĖčģ čüąŠą▒čŗčéąĖą╣ ąĮąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ).

NRF_PWM0->PSEL.OUT[0] = (first_pin << PWM_PSEL_OUT_PIN_Pos) |

(PWM_PSEL_OUT_CONNECT_Connected <<

PWM_PSEL_OUT_CONNECT_Pos);

NRF_PWM0->ENABLE = (PWM_ENABLE_ENABLE_Enabled << PWM_ENABLE_ENABLE_Pos);

NRF_PWM0->MODE = (PWM_MODE_UPDOWN_Up << PWM_MODE_UPDOWN_Pos);

NRF_PWM0->PRESCALER = (PWM_PRESCALER_PRESCALER_DIV_1 <<

PWM_PRESCALER_PRESCALER_Pos);

NRF_PWM0->COUNTERTOP = (16000 << PWM_COUNTERTOP_COUNTERTOP_Pos); //1 msec

NRF_PWM0->LOOP = (1 << PWM_LOOP_CNT_Pos);

NRF_PWM0->DECODER = (PWM_DECODER_LOAD_Common << PWM_DECODER_LOAD_Pos) |

(PWM_DECODER_MODE_RefreshCount << PWM_DECODER_MODE_Pos);

NRF_PWM0->SEQ[0].PTR = ((uint32_t)(seq0_ram) << PWM_SEQ_PTR_PTR_Pos);

NRF_PWM0->SEQ[0].CNT = ((sizeof(seq0_ram) / sizeof(uint16_t)) <<

PWM_SEQ_CNT_CNT_Pos);

NRF_PWM0->SEQ[0].REFRESH = 1;

NRF_PWM0->SEQ[0].ENDDELAY = 1;

NRF_PWM0->SEQ[1].PTR = ((uint32_t)(seq1_ram) << PWM_SEQ_PTR_PTR_Pos);

NRF_PWM0->SEQ[1].CNT = ((sizeof(seq1_ram) / sizeof(uint16_t)) <<

PWM_SEQ_CNT_CNT_Pos);

NRF_PWM0->SEQ[1].REFRESH = 0;

NRF_PWM0->SEQ[1].ENDDELAY = 0;

NRF_PWM0->TASKS_SEQSTART[0] = 1;

ąĀąĖčü. 6. ą¤čĆąĖą╝ąĄčĆ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┤ą▓čāčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣, ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĄą╝čŗčģ ą┤čĆčāą│ ąĘą░ ą┤čĆčāą│ąŠą╝.

ąöąĄą║ąŠą┤ąĄčĆ ą╝ąŠąČąĄčé ą▒čŗčéčī čéą░ą║ąČąĄ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą░čüąĖąĮčģčĆąŠąĮąĮąŠą╣ ąĘą░ą│čĆčāąĘą║ąĖ ąĮąŠą▓ąŠą╣ čüą║ą▓ą░ąČąĮąŠčüčéąĖ PWM. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ DECODER.MODE = NextStep, č鹊 ą░ą║čéąĖą▓ą░čåąĖčÅ NEXTSTEP task ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÄ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ ą┐ąĄčĆąĖąŠą┤ąĄ PWM.

ąĀąĖčüčāąĮą║ąĖ ąĮąĖąČąĄ ą┤ą░čÄčé ąŠą▒ąĘąŠčĆ ą║ą░ąČą┤ąŠą╣ čćą░čüčéąĖ ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ čĆąĄąČąĖą╝ą░čģ (LOOP.CNT=0 ąĖ LOOP.CNT>0). ąÆ čćą░čüčéąĮąŠčüčéąĖ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąŠ čüą╗ąĄą┤čāčÄčēąĄąĄ:

ŌĆó ąØą░čćą░ą╗čīąĮčŗą╣ ąĖ ą║ąŠąĮąĄčćąĮčŗą╣ čåąĖą║ą╗ čüą║ą▓ą░ąČąĮąŠčüčéąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ (ą▓čŗčģąŠą┤ą░čģ) PWM.

ŌĆó ąĪąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą▓ čåąĄą┐ąŠčćą║čā SEQ[0] ąĖ SEQ[1], ąĄčüą╗ąĖ LOOP.CNT>0.

ŌĆó ąÆą╗ąĖčÅąĮąĖąĄ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī.

ŌĆó ąĪąŠą▒čŗčéąĖčÅ, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ.

ŌĆó ąÉą║čéąĖą▓ąĮąŠčüčéčī DMA: ąĘą░ą│čĆčāąĘą║ą░ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ ąĄą│ąŠ ąĮą░ ą▓čŗčģąŠą┤ąĄ (ą▓čŗčģąŠą┤ą░čģ).

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąĖą╝ąĄčĆ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą│ąŠ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖą╝ąĄąĮąĖą╝ čéą░ą║ąČąĄ ąĖ ą║ SEQ[1], ąĘą┤ąĄčüčī SEQ[0] ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮą░ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ.

ąĀąĖčü. 7. ą×ą┤ąĮąŠą║čĆą░čéąĮąŠąĄ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖąĄ (LOOP.CNT=0).

ąĀąĖčü. 8. ąĪą╗ąŠąČąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī (LOOP.CNT>0), ąĮą░čćąĖąĮą░čÄčēą░čÅčüčÅ čü SEQ[0].

ąĀąĖčü. 9. ąĪą╗ąŠąČąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī (LOOP.CNT>0), ąĮą░čćąĖąĮą░čÄčēą░čÅčüčÅ čü SEQ[1].

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐čĆąŠčüčéą░čÅ ąĖą╗ąĖ čüą╗ąŠąČąĮą░čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī, čā ąĮąĄčæ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ą┤ą╗ąĖąĮą░ SEQ[n].CNT>0 .

[ą×ą│čĆą░ąĮąĖč湥ąĮąĖčÅ]

ą¤čĆąĄą┤čŗą┤čāčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą▒čāą┤ąĄčé ą┐ąŠą▓č鹊čĆąĄąĮąŠ, ąĄčüą╗ąĖ ą▓čŗą▒čĆą░ąĮ ą┐ąĄčĆąĖąŠą┤ PWM ą║ąŠčĆąŠč湥, č湥ą╝ ą▓čĆąĄą╝čÅ, čéčĆąĄą▒čāąĄą╝ąŠąĄ ą┤ą╗čÅ EasyDMA, čćč鹊ą▒čŗ čüą┤ąĄą╗ą░čéčī ą▓čŗą▒ąŠčĆą║čā ąĖąĘ RAM ąĖ ąŠą▒ąĮąŠą▓ąĖčéčī ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ.

ąŁč鹊 čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ ą▒ąĄąĘ ą┐ą░čĆą░ąĘąĖčéąĮčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą▓čŗą▒čĆą░ąĮčŗ ąŠč湥ąĮčī ą║ąŠčĆąŠčéą║ąĖąĄ ą┐ąĄčĆąĖąŠą┤čŗ PWM.

[ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąĮąŠąČąĄą║ ą┐ąŠčĆč鹊ą▓]

ąĪąĖą│ąĮą░ą╗čŗ OUT[n] (n=0..3), čüą▓čÅąĘą░ąĮąĮčŗąĄ čü ą║ą░ąČą┤čŗą╝ ą║ą░ąĮą░ą╗ąŠą╝ ą╝ąŠą┤čāą╗čÅ PWM, ąŠč鹊ą▒čĆą░ąČą░čÄčéčüčÅ ąĮą░ čäąĖąĘąĖč湥čüą║ąĖąĄ ą▓čŗą▓ąŠą┤čŗ ą┐ąŠčĆč鹊ą▓ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĄą╣, čāą║ą░ąĘą░ąĮąĮąŠą╣ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ąĖ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ PSEL.OUT[n]. ąĢčüą╗ąĖ SEL.OUT[n].CONNECT čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ Disconnected, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čüąĖą│ąĮą░ą╗ ą╝ąŠą┤čāą╗čÅ PWM ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ ą║ ą╗čÄą▒ąŠą╝čā čäąĖąĘąĖč湥čüą║ąŠą╝čā ą▓čŗą▓ąŠą┤čā.

ąĀąĄą│ąĖčüčéčĆčŗ PSEL.OUT[n] ąĖ ąĖčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠą║ą░ ą╝ąŠą┤čāą╗čī PWM čĆą░ąĘčĆąĄčłąĄąĮ, ąĖ ą░ą║čéąĖą▓ąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ PWM (čüč湥čéčćąĖą║ ąĘą░ą┐čāčēąĄąĮ), ąĖ čŹč鹊 čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą┐ąŠą║ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ System ON, čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą╝ąŠą┤čāą╗čÅ POWER [3] ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ąŠ čĆąĄąČąĖą╝ą░čģ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ.

ąöą╗čÅ ą│ą░čĆą░ąĮčéąĖąĖ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÅ ą╝ąŠą┤čāą╗čÅ PWM ą▓čŗą▓ąŠą┤čŗ, ą║ąŠč鹊čĆčŗąĄ PWM ąĖčüą┐ąŠą╗čīąĘčāąĄčé, ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ GPIO [4], ą║ą░ą║ čŹč鹊 ąŠą┐ąĖčüą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 2, ąĖ čŹč鹊 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮąŠ ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝ ą╝ąŠą┤čāą╗čÅ PWM. ąśčüčģąŠą┤ąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą▓, ą║ąŠą│ą┤ą░ ąŠąĮąĖ ąĮą░čģąŠą┤čÅčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ąŠąČąĖą┤ą░ąĮąĖčÅ (pins idle state) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ OUT ą▓ ą╝ąŠą┤čāą╗ąĄ GPIO. ąŁč鹊 ą│ą░čĆą░ąĮčéąĖčĆčāąĄčé, čćč鹊 ą▓čŗą▓ąŠą┤čŗ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą╝ąŠą┤čāą╗ąĄą╝ PWM, ą┐ąĄčĆąĄą║ą╗čÄčćą░čÄčéčüčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠ, ąĄčüą╗ąĖ ą│ąĄąĮąĄčĆą░čåąĖčÅ PWM ąŠčüčéą░ąĮąŠą▓ą╗ąĄąĮą░ ą░ą║čéąĖą▓ą░čåąĖąĄą╣ STOP task, ąĄčüą╗ąĖ čüą░ą╝ ą╝ąŠą┤čāą╗čī PWM ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ąŠčłą╗ąŠ ą▓ System OFF. ąŁčéą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┤ąŠą╗ąČąĮą░ čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ą▓ GPIO ą┤ą╗čÅ ą▓čŗą▒čĆą░ąĮąĮčŗčģ ąĮąŠąČąĄą║ IO ą┐čĆąĖ čāčüą╗ąŠą▓ąĖąĖ, čćč鹊 ą╝ąŠą┤čāą╗čī PWM ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ ą║ ą▓ąĮąĄčłąĮąĄą╣ čüčģąĄą╝ąĄ PWM (ąĮą░ą┐čĆąĖą╝ąĄčĆ čüąĖą╗ąŠą▓čŗąĄ ą║ą╗čÄčćąĖ).

ąÆ ą╗čÄą▒ąŠą╣ ą╝ąŠą╝ąĄąĮčé ą▓čĆąĄą╝ąĄąĮąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ąĘąĮą░č湥ąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ ąĮąŠąČą║ąĖ GPIO. ąĢčüą╗ąĖ ąĮąĄ ą▓čŗą┐ąŠą╗ąĮąĖčéčī čŹč鹊 čāčüą╗ąŠą▓ąĖąĄ, č鹊 ą▓ąŠąĘą╝ąŠąČąĮąŠ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ.

ąóą░ą▒ą╗ąĖčåą░ 2. ąĀąĄą║ąŠą╝ąĄąĮą┤čāąĄą╝ą░čÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÅ GPIO ą┐ąĄčĆąĄą┤ ąĘą░ą┐čāčüą║ąŠą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ PWM.

| ąĪąĖą│ąĮą░ą╗ PWM |

ąØąŠąČą║ą░ ą┐ąŠčĆčéą░ PWM |

ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ |

ąŚąĮą░č湥ąĮąĖąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖą╣ |

| OUT[n] |

ąÜą░ą║ čāą║ą░ąĘą░ąĮąŠ ą▓ PSEL.OUT[n], n=0..3 |

ąÆčŗčģąŠą┤ |

0 |

ąĪąŠčüč鹊čÅąĮąĖąĄ ąŠčéčüčāčéčüčéą▓ąĖčÅ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ GPIO->OUT. |

[ąĀąĄą│ąĖčüčéčĆčŗ PWM]

ąóą░ą▒ą╗ąĖčåą░ 3. ąŁą║ąĘąĄą╝ą┐ą╗čÅčĆčŗ PWM, ą▒ą░ąĘąŠą▓čŗąĄ ą░ą┤čĆąĄčüą░ ąĮą░čćą░ą╗ą░ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ čĆąĄą│ąĖčüčéčĆąŠą▓.

| ąæą░ąĘ. ą░ą┤čĆąĄčü |

ą¤ąĄčĆąĖčä. čāčüčéčĆąŠą╣čüčéą▓ąŠ |

ąŁą║ąĘ. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ |

| 0x4001C000 |

PWM |

PWM0 |

ąæą╗ąŠą║ čłąĖčĆąŠčéąĮąŠ-ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ ą╝ąŠą┤čāą╗čÅčåąĖąĖ 0 |

|

| 0x40021000 |

PWM1 |

ąæą╗ąŠą║ čłąĖčĆąŠčéąĮąŠ-ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ ą╝ąŠą┤čāą╗čÅčåąĖąĖ 1 |

|

| 0x40022000 |

PWM2 |

ąæą╗ąŠą║ čłąĖčĆąŠčéąĮąŠ-ąĖą╝ą┐čāą╗čīčüąĮąŠą╣ ą╝ąŠą┤čāą╗čÅčåąĖąĖ 2 |

|

ąóą░ą▒ą╗ąĖčåą░ 4. ą×ą▒ąĘąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ PWM.

| ąĀąĄą│ąĖčüčéčĆ |

ąĪą╝ąĄčē. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| TASKS_STOP |

0x004 |

ą×čüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ąĖą╝ą┐čāą╗čīčüą░ PWM ąĮą░ ą▓čüąĄčģ ą║ą░ąĮą░ą╗ą░čģ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ PWM, ąĖ ąŠčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÅ. |

| TASKS_SEQSTART[0] |

0x008 |

ąŚą░ą│čĆčāąČą░ąĄčé ą┐ąĄčĆą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ PWM ąĮą░ ą▓čüąĄčģ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą║ą░ąĮą░ą╗ą░čģ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0, ąĖ ąĘą░ą┐čāčüą║ą░ąĄčé ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ, ą║ąŠč鹊čĆą░čÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓ SEQ[0].REFRESH ąĖ/ąĖą╗ąĖ DECODER.MODE. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ PWM, ąĄčüą╗ąĖ ąŠąĮą░ ąĮąĄ ą▒čŗą╗ą░ čāąČąĄ ąĘą░ą┐čāčēąĄąĮą░. |

| TASKS_SEQSTART[1] |

0x00C |

ąŚą░ą│čĆčāąČą░ąĄčé ą┐ąĄčĆą▓ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ PWM ąĮą░ ą▓čüąĄčģ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą║ą░ąĮą░ą╗ą░čģ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1, ąĖ ąĘą░ą┐čāčüą║ą░ąĄčé ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ čüąŠ čüą║ąŠčĆąŠčüčéčīčÄ, ą║ąŠč鹊čĆą░čÅ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓ SEQ[1].REFRESH ąĖ/ąĖą╗ąĖ DECODER.MODE. ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ PWM, ąĄčüą╗ąĖ ąŠąĮą░ ąĮąĄ ą▒čŗą╗ą░ čāąČąĄ ąĘą░ą┐čāčēąĄąĮą░. |

| TASKS_NEXTSTEP |

0x010 |

ąÆčŗą┐ąŠą╗ąĮčÅąĄčé 1 čłą░ą│ ą▓ą┐ąĄčĆąĄą┤ ąĮą░ ąŠą┤ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ ą▓ č鹥ą║čāčēąĄą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ąĮą░ ą▓čüąĄčģ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗčģ ą║ą░ąĮą░ą╗ą░čģ, ąĄčüą╗ąĖ DECODER.MODE=NextStep. ąØąĄ ąĘą░ą┐čāčüą║ą░ąĄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ PWM, ąĄčüą╗ąĖ ąŠąĮą░ ąĮąĄ ą▒čŗą╗ą░ ąĘą░ą┐čāčēąĄąĮą░. |

| EVENTS_STOPPED |

0x104 |

ą×čéą▓ąĄčé ąĮą░ STOP task, ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐ąĄčĆąĄčüčéą░ą╗ąĖ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ąĖą╝ą┐čāą╗čīčüčŗ PWM. |

| EVENTS_SEQSTARTED[0] |

0x108 |

ąØą░čćą░ą╗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĖąŠą┤ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0. |

| EVENTS_SEQSTARTED[1] |

0x10C |

ąØą░čćą░ą╗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┐ąĄčĆą▓čŗą╣ ą┐ąĄčĆąĖąŠą┤ ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1. |

| EVENTS_SEQEND[0] |

0x110 |

ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╝ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0, ą║ąŠą│ą┤ą░ ąĄčæ ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čŗą╗ąŠ ąĖąĘą▓ą╗ąĄč湥ąĮąŠ ąĖąĘ RAM ąĖ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 Wave Counter. |

| EVENTS_SEQEND[1] |

0x114 |

ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╝ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1, ą║ąŠą│ą┤ą░ ąĄčæ ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čŗą╗ąŠ ąĖąĘą▓ą╗ąĄč湥ąĮąŠ ąĖąĘ RAM ąĖ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 Wave Counter. |

| EVENTS_PWMPERIODEND |

0x118 |

ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ PWM. |

| EVENTS_LOOPSDONE |

0x11C |

ąŚą░ą▓ąĄčĆčłąĄąĮąŠ LOOP.CNT ą┐ąŠą▓č鹊čĆąĄąĮąĖą╣ čüąŠąĄą┤ąĖąĮąĄąĮąĮčŗčģ ą▓ čåąĄą┐ąŠčćą║čā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣. |

| SHORTS |

0x200 |

ąĀąĄą│ąĖčüčéčĆ čłąŠčĆčéą║ą░čéą░. |

| INTEN |

0x300 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖ ąĘą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| INTENSET |

0x304 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| INTENCLR |

0x308 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. |

| ENABLE |

0x500 |

ąĀąĄą│ąĖčüčéčĆ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą╝ąŠą┤čāą╗čÅ PWM. |

| MODE |

0x504 |

ąÆčŗą▒ąŠčĆ čĆą░ą▒ąŠč湥ą│ąŠ čĆąĄąČąĖą╝ą░ Wave Counter. |

| COUNTERTOP |

0x508 |

ąŚąĮą░č湥ąĮąĖąĄ, ą┤ąŠ ą║ąŠč鹊čĆąŠą│ąŠ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čüč湥čéčćąĖą║. |

| PRESCALER |

0x50C |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┤ą╗čÅ PWM_CLK. |

| DECODER |

0x510 |

ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ą┤ąĄą║ąŠą┤ąĄčĆą░. |

| LOOP |

0x514 |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąŠą▓č鹊čĆąŠą▓ čåąĖą║ą╗ąŠą▓ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖčÅ. |

| SEQ[0].PTR |

0x520 |

ąØą░čćą░ą╗ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0 ą▓ Data RAM. |

| SEQ[0].CNT |

0x524 |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ąĘąĮą░č湥ąĮąĖą╣ (čüą║ą▓ą░ąČąĮąŠčüč鹥ą╣) ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0. |

| SEQ[0].REFRESH |

0x528 |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ PWM ą╝ąĄąČą┤čā ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ, ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┐čĆąĖ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0. |

| SEQ[0].ENDDELAY |

0x52C |

ąÆčĆąĄą╝čÅ, ą┤ąŠą▒ą░ą▓ą╗čÅąĄą╝ąŠąĄ ą▓ ą║ąŠąĮčåąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 0. |

| SEQ[1].PTR |

0x540 |

ąØą░čćą░ą╗ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1 ą▓ Data RAM. |

| SEQ[1].CNT |

0x544 |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ąĘąĮą░č湥ąĮąĖą╣ (čüą║ą▓ą░ąČąĮąŠčüč鹥ą╣) ą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1. |

| SEQ[1].REFRESH |

0x548 |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ PWM ą╝ąĄąČą┤čā ą▓čŗą▒ąŠčĆą║ą░ą╝ąĖ, ąĘą░ą│čĆčāąČą░ąĄą╝čŗą╝ąĖ ą▓ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ ą┐čĆąĖ ą┐čĆąŠąĖą│čĆčŗą▓ą░ąĮąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1. |

| SEQ[1].ENDDELAY |

0x54C |

ąÆčĆąĄą╝čÅ, ą┤ąŠą▒ą░ą▓ą╗čÅąĄą╝ąŠąĄ ą▓ ą║ąŠąĮčåąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ 1. |

| PSEL.OUT[0] |

0x560 |

ąÆčŗą▒ąŠčĆ ą▓čŗčģąŠą┤ąĮąŠą╣ ąĮąŠąČą║ąĖ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 0 PWM. |

| PSEL.OUT[1] |

0x564 |

ąÆčŗą▒ąŠčĆ ą▓čŗčģąŠą┤ąĮąŠą╣ ąĮąŠąČą║ąĖ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 1 PWM. |

| PSEL.OUT[2] |

0x568 |

ąÆčŗą▒ąŠčĆ ą▓čŗčģąŠą┤ąĮąŠą╣ ąĮąŠąČą║ąĖ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 2 PWM. |

| PSEL.OUT[3] |

0x56C |

ąÆčŗą▒ąŠčĆ ą▓čŗčģąŠą┤ąĮąŠą╣ ąĮąŠąČą║ąĖ ą┤ą╗čÅ ą║ą░ąĮą░ą╗ą░ 3 PWM. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x200. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé čłąŠčĆčéą║ą░čé, ąĘą░ą┐ąĖčüčī 0 ąĘą░ą┐čĆąĄčēą░ąĄčé. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹥ą║čāčēąĄąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ SHORTS:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

D |

C |

B |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

SEQEND0_STOP |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ EVENTS_SEQEND[0] ąĖ ąĘą░ą┤ą░č湥ą╣ TASKS_STOP. |

| B |

RW |

SEQEND1_STOP |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ EVENTS_SEQEND[1] ąĖ ąĘą░ą┤ą░č湥ą╣ TASKS_STOP. |

| C |

RW |

LOOPSDONE_SEQSTART0 |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ LOOPSDONE ąĖ ąĘą░ą┤ą░č湥ą╣ TASKS_SEQSTART[0]. |

| D |

RW |

LOOPSDONE_SEQSTART1 |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ LOOPSDONE ąĖ ąĘą░ą┤ą░č湥ą╣ TASKS_SEQSTART[1]. |

| E |

RW |

LOOPSDONE_STOP |

ą©ąŠčĆčéą║ą░čé ą╝ąĄąČą┤čā čüąŠą▒čŗčéąĖąĄą╝ LOOPSDONE ąĖ ąĘą░ą┤ą░č湥ą╣ TASKS_STOP. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x300. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, ąĘą░ą┐ąĖčüčī 0 ąĘą░ą┐čĆąĄčēą░ąĄčé. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTEN:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

G |

F |

E |

D |

C |

B |

|

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| B |

RW |

STOPPED |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ STOPPED. ąĪą╝. EVENTS_STOPPED. |

| C |

RW |

SEQSTARTED0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[0]. ąĪą╝. EVENTS_SEQSTARTED[0]. |

| D |

RW |

SEQSTARTED1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[1]. ąĪą╝. EVENTS_SEQSTARTED[1]. |

| E |

RW |

SEQEND0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQEND[0]. ąĪą╝. EVENTS_SEQEND[0]. |

| F |

RW |

SEQEND1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQEND[1]. ąĪą╝. EVENTS_SEQEND[1]. |

| G |

RW |

PWMPERIODEND |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ PWMPERIODEND. ąĪą╝. EVENTS_PWMPERIODEND. |

| H |

RW |

LOOPSDONE |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ LOOPSDONE. ąĪą╝. EVENTS_LOOPSDONE. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x304. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTENSET:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

G |

F |

E |

D |

C |

B |

|

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| B |

RW |

STOPPED |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ STOPPED. ąĪą╝. EVENTS_STOPPED. |

| C |

RW |

SEQSTARTED0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[0]. ąĪą╝. EVENTS_SEQSTARTED[0]. |

| D |

RW |

SEQSTARTED1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[1]. ąĪą╝. EVENTS_SEQSTARTED[1]. |

| E |

RW |

SEQEND0 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQEND[0]. ąĪą╝. EVENTS_SEQEND[0]. |

| F |

RW |

SEQEND1 |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQEND[1]. ąĪą╝. EVENTS_SEQEND[1]. |

| G |

RW |

PWMPERIODEND |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ PWMPERIODEND. ąĪą╝. EVENTS_PWMPERIODEND. |

| H |

RW |

LOOPSDONE |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ LOOPSDONE. ąĪą╝. EVENTS_LOOPSDONE. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x308. ąŚą░ą┐ąĖčüčī 1 ąĘą░ą┐čĆąĄčēą░ąĄčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ. ąŚą░ą┐ąĖčüčī 0 ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąĮąĖą║ą░ą║ąŠą│ąŠ ą▓ą╗ąĖčÅąĮąĖčÅ. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 0 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ, 1 čĆą░ąĘčĆąĄčłąĄąĮąŠ.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ INTENCLR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

G |

F |

E |

D |

C |

B |

|

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| B |

RW |

STOPPED |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ STOPPED. ąĪą╝. EVENTS_STOPPED. |

| C |

RW |

SEQSTARTED0 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[0]. ąĪą╝. EVENTS_SEQSTARTED[0]. |

| D |

RW |

SEQSTARTED1 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQSTARTED[1]. ąĪą╝. EVENTS_SEQSTARTED[1]. |

| E |

RW |

SEQEND0 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQEND[0]. ąĪą╝. EVENTS_SEQEND[0]. |

| F |

RW |

SEQEND1 |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ SEQEND[1]. ąĪą╝. EVENTS_SEQEND[1]. |

| G |

RW |

PWMPERIODEND |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ PWMPERIODEND. ąĪą╝. EVENTS_PWMPERIODEND. |

| H |

RW |

LOOPSDONE |

ąŚą░ą┐čĆąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čüąŠą▒čŗčéąĖčÅ LOOPSDONE. ąĪą╝. EVENTS_LOOPSDONE. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x500. ąŚą░ą┐ąĖčüčī 1 čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā ą╝ąŠą┤čāą╗čÅ PWM. ą¦č鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüąŠčüč鹊čÅąĮąĖąĄ: 0 čĆą░ą▒ąŠčéą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą╝ąŠą┤čāą╗čÅ PWM ąĘą░ą┐čĆąĄčēąĄąĮą░, 1 čĆą░ąĘčĆąĄčłąĄąĮą░.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ ENABLE:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

ENABLE |

ąĀą░ąĘčĆąĄčłąĄąĮąĖąĄ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčé ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą╝ąŠą┤čāą╗čÅ PWM. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x504. ąŚą░ą┐ąĖčüčī ą▓čŗą▒ąĖčĆą░ąĄčé čĆąĄąČąĖą╝ čüč湥čéą░, čćč鹥ąĮąĖąĄ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé č鹥ą║čāčēąĖą╣ ą▓čŗą▒čĆą░ąĮąĮčŗą╣ čĆąĄąČąĖą╝.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ MODE:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

MODE |

0: Up, čüč湥čé ą▓ą▓ąĄčĆčģ. ąōąĄąĮąĄčĆą░čåąĖčÅ ą▒čŗčüčéčĆčŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£ čü ą▓čŗčĆą░ą▓ąĮąĖą▓ą░ąĮąĖąĄą╝ ą┐ąŠ ąĮą░čćą░ą╗čā ą┐ąĄčĆąĖąŠą┤ą░ (edge-aligned PWM).

1: UpAndDown, čüč湥čé ą▓ą▓ąĄčĆčģ ąĖ ą▓ąĮąĖąĘ. ąōąĄąĮąĄčĆą░čåąĖčÅ ąĖą╝ą┐čāą╗čīčüąŠą▓ ą©ąśą£ ąĮą░ čćą░čüč鹊č鹥 ą▓ 2 čĆą░ąĘą░ ą╝ąĄąĮčīčłąĄą╣, ąĮąŠ ąĘą░č鹊 ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗčģ ą┐ąŠčüąĄčĆąĄą┤ąĖąĮąĄ (center-aligned PWM). |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x508. ąÆąĄčĆčģąĮąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą┤ąŠ ą║ąŠč鹊čĆąŠą│ąŠ čüčćąĖčéą░ąĄčé čüč湥čéčćąĖą║.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ COUNTERTOP:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x000003FF |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

COUNTERTOP |

ąŚąĮą░č湥ąĮąĖąĄ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 3..32767. ą¤čĆąĄą┤ąĄą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ą┤ąŠ ą║ąŠč鹊čĆąŠą│ąŠ ą┤ąŠčģąŠą┤ąĖčé čüč湥čé ą▓ą▓ąĄčĆčģ. ąŁč鹊čé čĆąĄą│ąĖčüčéčĆ ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ DECODER.MODE = WaveForm, ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąĖąĘ RAM. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x50C.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ PRESCALER:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PRESCALER |

0: DIV_1, ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ (PWM_CLK = 16 ą£ąōčå).

1: DIV_2, ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 2 (PWM_CLK = 8 ą£ąōčå).

2: DIV_4, ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 4 (PWM_CLK = 4 ą£ąōčå).

3: DIV_8, ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 8 (PWM_CLK = 2 ą£ąōčå).

4: DIV_16, ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 16 (PWM_CLK = 1 ą£ąōčå).

5: DIV_32, ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 32 (PWM_CLK = 500 ą║ąōčå).

6: DIV_64, ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 64 (PWM_CLK = 250 ą║ąōčå).

7: DIV_128, ą┤ąĄą╗ąĄąĮąĖąĄ čćą░čüč鹊čéčŗ ąĮą░ 128 (PWM_CLK = 125 ą║ąōčå). |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x510.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ DECODER:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

LOAD |

ą×ą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą║ą░ą║ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī čüčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąĖąĘ RAM, ąĖ ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ.

0: Common, ą┐ąĄčĆą▓ą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą║ą░ čüą╗ąŠą▓ą░ (16 ą▒ąĖčé) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą▓čüąĄčģ ą║ą░ąĮą░ą╗ąŠą▓ 0..3.

1: Grouped, ą┐ąĄčĆą▓ą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą║ą░ čüą╗ąŠą▓ą░ (16 ą▒ąĖčé) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ą░ąĮą░ą╗ą░čģ 0 ąĖ 1, ą▓č鹊čĆą░čÅ ą▓ ą║ą░ąĮą░ą╗ą░čģ 2 ąĖ 3.

2: Individual, ą┐ąĄčĆą▓ą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą║ą░ čüą╗ąŠą▓ą░ (16 ą▒ąĖčé) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ą░ąĮą░ą╗ąĄ 0, ą▓č鹊čĆą░čÅ ą▓ ą║ą░ąĮą░ą╗ąĄ 1, čéčĆąĄčéčīčÅ ą▓ ą║ą░ąĮą░ą╗ąĄ 2, č湥čéą▓ąĄčĆčéą░čÅ ą▓ ą║ą░ąĮą░ą╗ąĄ 3.

3: WaveForm, ą┐ąĄčĆą▓ą░čÅ ą┐ąŠą╗ąŠą▓ąĖąĮą║ą░ čüą╗ąŠą▓ą░ (16 ą▒ąĖčé) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ą░ąĮą░ą╗ąĄ 0, ą▓č鹊čĆą░čÅ ą▓ ą║ą░ąĮą░ą╗ąĄ 1, čéčĆąĄčéčīčÅ ą▓ ą║ą░ąĮą░ą╗ąĄ 2, č湥čéą▓ąĄčĆčéą░čÅ ą▓ COUNTERTOP. |

| B |

RW |

MODE |

ąÆčŗą▒ąĖčĆą░ąĄčé ąĖčüč鹊čćąĮąĖą║ ą┤ą╗čÅ ąĖč鹥čĆą░čåąĖąĖ ą┐ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ.

0: RefreshCount, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ SWQ[n].REFRESH ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąĖąĮč鹥čĆą▓ą░ą╗ą░ ąĘą░ą│čĆčāąĘą║ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ čüčĆą░ą▓ąĮąĄąĮąĖčÅ.

1: NextStep, ą░ą║čéąĖą▓ą░čåąĖčÅ NEXTSTEP task ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░ą│čĆčāąĘą║ąĖ ąĮąŠą▓ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čüčĆą░ą▓ąĮąĄąĮąĖčÅ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x514.

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ LOOP:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

CNT |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┐ąŠą▓č鹊čĆąŠą▓ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüč鹥ą╣. ąĢčüą╗ąĖ 0, č鹊 ą┐ąŠą▓č鹊čĆčŗ ąĘą░ą┐čĆąĄčēąĄąĮčŗ (ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ąŠčüčéą░ąĮąŠą▓ą║ą░ ą▓ ą║ąŠąĮčåąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ). |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x520 + (n * 0x20).

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ SEQ[n].PTR:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PTR |

ąÉą┤čĆąĄčü ąĮą░čćą░ą╗ą░ ą▒čāč乥čĆą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ Data RAM. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x524 + (n * 0x20).

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ SEQ[n].CNT:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

CNT |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ąĘąĮą░č湥ąĮąĖą╣ (čüą║ą▓ą░ąČąĮąŠčüč鹥ą╣) ą▒čāč乥čĆą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ ą▓ Data RAM. ąĢčüą╗ąĖ 0, č鹊 ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĘą░ą┐čĆąĄčēąĄąĮą░ ąĖ ąĮąĄ ą┤ąŠą╗ąČąĮą░ ąĘą░ą┐čāčüą║ą░čéčīčüčÅ, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮą░ ą┐čāčüčéą░čÅ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x528 + (n * 0x20).

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ SEQ[n].REFRESH:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

CNT |

ąÜąŠą╗ąĖč湥čüčéą▓ąŠ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ ą┐ąĄčĆąĖąŠą┤ąŠą▓ PWM ą╝ąĄąČą┤čā ąĘą░ą│čĆčāąĘą║ą░ą╝ąĖ ą▓čŗą▒ąŠčĆąŠą║ ą▓ čĆąĄą│ąĖčüčéčĆ čüčĆą░ą▓ąĮąĄąĮąĖčÅ (ąĘą░ą│čĆčāąĘą║ą░ ą║ą░ąČą┤čŗąĄ REFRESH.CNT+1 ą┐ąĄčĆąĖąŠą┤ąŠą▓ PWM). ąĢčüą╗ąĖ 0 (Continuous), č鹊 ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą▓ ą║ą░ąČą┤ąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ PWM. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x52C + (n * 0x20).

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ SEQ[n].ENDDELAY:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

A |

| Reset 0x00000000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

CNT |

ąÆčĆąĄą╝čÅ ą▓ ą║ąŠą╗ąĖč湥čüčéą▓ąĄ ą┐ąĄčĆąĖąŠą┤ąŠą▓ PWM, ą┤ąŠą▒ą░ą▓ą╗čÅąĄą╝čŗčģ ą▓ ą║ąŠąĮčåąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéąĖ. |

ąĪą╝ąĄčēąĄąĮąĖąĄ ą░ą┤čĆąĄčüą░: 0x560 + (n * 0x04).

ąæąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ PSEL.OUT[n]:

| Ōä¢ ą▒ąĖčéą░ |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| Id |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

A |

A |

A |

A |

| Reset 0xFFFFFFFF |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčé:

| Id |

RW |

ą¤ąŠą╗ąĄ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| A |

RW |

PIN |

ąØąŠą╝ąĄčĆ čĆą░ąĘčĆčÅą┤ą░ ą┐ąŠčĆčéą░ [0..31]. |

| C |

RW |

CONNECT |

0: Connected

1: Disconnected |

[ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ PWM]

| ąĪąĖą╝ą▓. |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

min |

Typ. |

MAX |

ąĢą┤. |

| IPWM,16MHz |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéą░čÄčēąĄą│ąŠ PWM, ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ DIV_1 (16 ą£ąōčå), ą▒ąĄąĘ čāč湥čéą░ DMA ąĖ GPIO. |

|

200 |

|

ą╝ą║ąÉ |

| IPWM,8MHz |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéą░čÄčēąĄą│ąŠ PWM, ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ DIV_2 (8 ą£ąōčå), ą▒ąĄąĘ čāč湥čéą░ DMA ąĖ GPIO. |

|

150 |

|

| IPWM,125kHz |

ąóąŠą║ ą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčéą░čÄčēąĄą│ąŠ PWM, ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĮą░ DIV_128 (125 ą║ąōčå), ą▒ąĄąĘ čāč湥čéą░ DMA ąĖ GPIO. |

|

150 |

|

[ąĪčüčŗą╗ą║ąĖ]

1. nRF52832 PWM Pulse width modulation site:nordicsemi.com.

2. nRF52: ą┐ą░ą╝čÅčéčī.

3. nRF52: ąĖčüč鹊čćąĮąĖą║ąĖ ą┐ąĖčéą░ąĮąĖčÅ.

4. nRF5x: ą┐ąŠčĆčéčŗ GPIO. |