|

Этот документ (перевод апноута XAPP784[1]) объединил в себе многолетний опыт решения проблем пользователей микросхем CPLD Xilinx.

С помощью простого набора правил, описанного ниже, можно получить надежный дизайн на основе схем CPLD. Большинство из этих правил хорошо знакомы разработчикам цифровых устройств. Следующие рекомендации по разработке поделены на 2 секции: практические рекомендации по аппаратуре (hardware) и практические рекомендации по программному обеспечению (software).

[Hardware]

1. Проследите, что все выводы питания VCC и GND правильно разведены на печатной плате.

2. Делайте качественную развязку и фильтрацию цепей выводов VCC (VCCINT и VCCIO).

3. Используйте строго синхронный дизайн.

4. Не оставляйте не подключенными свободные (не используемые) выводы микросхем CPLD.

5. Для управления светодиодами используйте втекающий в вывод выхода ток (sink current, светодиод загорается, когда на выходе лог. 0).

6. Используйте терминирование высокоскоростных выходов.

7. Избегайте использования нижних (pull-down) притягивающих резисторов на выводах.

8. Избегайте управление вводом/выводом с уровнями, превышающими VCCIO.

9. Помните о добавлении интерфейсов JTAG на печатную плату устройства.

10. Не используйте внешнее терминирование JTAG для выводов, которые имеют внутреннее терминирование.

11. Убедитесь, что регулятор напряжения предоставляет достаточный ток.

12. Если это возможно, подавайте питание на VCCINT перед подачей питания на VCCIO.

Дополнительные рекомендации по аппаратуре, касающиеся определенных семейств CPLD:

13. CoolRunner-II: для низкоскоростных входных сигналов используйте триггеры Шмитта (задается атрибутами при описании портов).

14. XPLA3: разберитесь, для чего нужен сигнал JTAG Port Enable, и правильно его используйте.

15. XC9500/XL/XV: используйте режим низкого энергопотребления (low power mode) для всех не критичных сигналов.

[Software]

1. Не оставляйте без внимания предупреждения файла отчета.

2. Используйте строго синхронный дизайн.

3. Разберитесь с ограничениями интервалов времени и соответствующими предупреждениями.

4. Просматривайте выражения CPLD Fitter Report.

5. Всегда правильно конфигурируйте сигналы ввода вывода I/O (LVCMOS 3.3, LVCMOS 1.8, и т. д.).

6. Если возможно, позвольте ПО разработки свободную (без ограничений) привязку внешних выводов чипа.

7. Очень полезно проводить симуляцию дизайна.

[Hardware, более подробно]

1. Проследите, что все выводы питания VCC и GND правильно разведены на печатной плате.

Микросхемы Xilinx CPLD не содержат избыточное количество выводов для подключения напряжения питания (VCC и земля). Эти выводы предоставляются с целью предоставления полноценного питания для всего устройства. Невозможно определить, какие выводы VCCINT применимы к определенным секциям устройства, так что существует риск пропустить соединение к любому из этих выводов. Выводы VCCIO явно назначаются для специфичных секций ввода/вывода кристалла, но если пропустить подключение каких-либо выводов питания может привести к утечкам тока, а также к дизбалансу питания остальной части устройства. Подобным образом выводы земли (GND) работают совместно для всех сигнальных цепей, и если пропустить подключение одного из них, то это может ухудшить общую работоспособность устройства. Оставленные без подключения выводы могут увеличить потребление тока и ухудшить помехозащищенность от импульсов, распространяющихся по шине земли. Соблюдайте простое правило: обеспечивайте ясное и короткое подключение всех выводов VCC и GND.

2. Делайте качественную развязку и фильтрацию цепей выводов VCC (VCCINT и VCCIO).

Все микросхемы Xilinx CPLD разработаны для использования в высокоскоростных устройствах. Для этого в любом случае требуется предоставления достаточного внутреннего тока. Самый лучший способ предоставления стабильного и надежного питания - применять дополнительные блокирующие конденсаторы по питанию, сглаживающие пульсации от быстрых переходных процессов, возникающих при переключениях. Дополнительно блокирующая развязка по питанию устраняет дополнительные источники помех, которые могут проходить через общие шины питания. Требуется применять как высокочастотную, так и низкочастотную развязку для каждого вывода питания VCCINT и VCCIO. Подробные указания можно найти в даташите XAPP112 для семейств XC9500/XL/XV, и даташитах XAPP377 и XAPP378 для семейств CoolRunner. Для улучшения развязки рекомендуется ставить конденсаторы как можно ближе к выводам VCC и GND устройства. Часто обратная сторона печатной платы непосредственно под корпусом устройства - лучшее место размещения блокирующих конденсаторов.

3. Используйте строго синхронный дизайн.

Большинство университетских учебников хвалят достоинство синхронного дизайна. И все же многим проектировщикам не удается следовать этому совету. Синхронный проект чрезвычайно прост. В нем все происходит в момент события активного такта. Это либо положительный перепад, либо отрицательный. Нет никаких асинхронных сбросов, кроме как общего глобального, который срабатывает в самом начале, при включении питания.

Установлено, что часто возникают ситуации, когда нужно соединить друг с другом две части логической схемы, которые тактируются раздельно от двух независимых источников (программисты это называют синхронизацией потоков). Самый лучший способ достичь этого - гарантировать строгую синхронность каждого региона (отдельного домена тактирования), кроме места, где происходит обмен информацией (обыно это данные). Для таких интерфейсов должен быть разработан отдельный ресурс синхронизации, осуществляющий обмен. В микросхемах FPGA таким ресурсом почти всегда служит структура FIFO с независимыми тактами чтения и записи. Из-за того, что у микросхемы CPLD недостаточно памяти, чтобы создать на её кристалле FIFO, нужно использовать маленький FIFO, сконструированный из регистров, где есть возможность записи с одной стороны регистра и чтения с другой. В некоторых случаях это потребуется осуществлять асинхронно. Тем не менее, если произойдет отказ в схеме, то Вы точно будете знать, где находится проблема - в интерфейсе!

В общем придерживайтесь правила не использовать совместно перепады спада и нарастания от одного источника тактов, и не смешивайте тактирование схемы от двух разных источников тактов.

4. Не оставляйте не подключенными свободные (не используемые) выводы микросхем CPLD.

Висящие входы (floating inputs) как правило увеличивают ток потребления CPLD, или по крайней мере не делает его предсказуемым. Каждый такой висящий вход добавляет один или два миллиампера к общему току потребления. Кроме того, наводки и шумы на не подключенном входе вредны, так как влияют на работу внутренних узлов CPLD.

Есть несколько способов простого терминирования висящих выводов. Наиболее гибкий из них - программируемая пользователем земля (user programmable ground), что доступно на кристаллах микросхем XC9500/XL/XV и CoolRunner-II (технология software switch). Также помогает внешнее подключение к шине земли, если "плавающие" выводы не планируются для использования в будущих редакциях. Также хорошо работает подтяжка выводов к высокому уровню (хотя большое количество резисторов pull-up, также хорошее решение, но более дорогое). Используйте software switch, это просто и бесплатно!

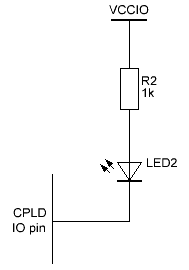

5. Используйте втекающий ток для управления светодиодами.

|

|

Source (управление светодиодом

через вытекающий ток) |

Sink (управление светодиодом

через втекающий ток) |

У всех микросхем Xilinx CPLD на выходе стоят N-канальные транзисторы FET, замыкающие ножку вывода на землю (нижнее плечо выходного драйвера). Обычно N-канальные транзисторы мощнее, чем P-канальные (которые ставят на верхнее плечо выходного драйвера). N-канальные транзисторы разработаны для протекания через них более сильных токов, которые обычно связаны с питанием светодиодов (LED). Конкретные значения можно узнать из даташитов Xilinx, подробнее про управление светодиодами можно почитать в апноуте XAPP805. Самые лучшие результаты получаются, когда катод светодиода подключен к выводу CPLD, а анод подключен через резистор к шине VCCIO соответствующего банка. Это также обеспечивает самую высокую яркость свечения LED-индикатора.

6. Используйте терминирование высокоскоростных выходов.

Все микросхемы Xilinx CPLD весьма быстрые. Они разработаны для получения быстрой реакции на любой вход. Даже медленно переключающиеся входы дают быстрый ответ. Последовательное терминирование самое дешевое, так что по крайней мере планируйте это при разработке схемы и печатной платы. Можно реализовать обозначение таких мест терминирования на печатной плате резисторами с нулевым сопротивлением (zero ohm), так что в последствии их можно удалить и заменить на резисторы с нужным сопротивлением. Труднее вставить резистор в уже спроектированную схему, чем выпаять нулевой резистор и заменить его. Базовые указания можно найти в даташитах XAPP115 для XC9500/XL/XV и XAPP379 для CoolRunner.

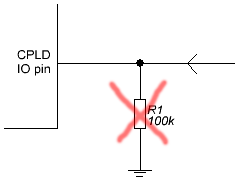

7. Избегайте использования нижних (pull-down) притягивающих резисторов на выводах.

Все микросхемы Xilinx CPLD имеют дополнительную схемотехнику на выводе корпуса вокруг буфера I/O. Это включает как защиту от статического электричества (ESD), так и схемы для управления поведением логики при включении. Например:

a. XC9500 при включении переводит выводы в состояние высокого сопротивления (отключено, High-Z)

b. XC9500XL/XV при включении сначала переводят выводы в High-Z, затем на удерживающую защелку (keeper latch)

c. XPLA3 при включении сначала переводят выводы в High-Z, затем на keeper "half latch"

d. CoolRunner-II при включении сначала переводят выводы в High-Z, затем на keeper latch

Резисторы pull-down "сражаются" с внутренней схемотехникой вывода, что может привести с неправильному поведению логики CPLD. Для более предсказуемого поведения избегайте использования нижних притягивающих с земле резисторов.

8. Избегайте управление вводом/выводом с уровнями, превышающими VCCIO.

Плохая идея управлять напряжением на выводе, превышающем напряжение питания банка VCCIO. В этом случае может течь обратный ток в регулятор напряжения, что повлияет на его производительность и на другие устройства, получающие питание от этого регулятора. Перегрузка также увеличивает утечку через соответствующую цепь устройства перегрузки течение периода перегрузки. В некоторых условиях это может ограничить время работоспособности CPLD. Максимальные пределы управления выходными нагрузками определены в даташите, убедитесь, что выполняете их условия.

9. Помните о добавлении интерфейсов JTAG на печатную плату устройства.

Стеки JTAG требуются для тестирования CPLD, когда она установлена на печатную плату (printed circuit board, PCB). Без этого проверка, если она понадобится, может оказаться очень затруднительной. Хорошая практика - как минимум предусмотреть на PCB место для установки коннектора JTAG. CPLD можно тестировать и программировать через специальные пробники JTAG (наподобие iMPACT cable, Parallel Cable IV или Platform Cable USB II). Интерфейс JTAG дает возможность использовать JTAG INTEST и EXTEST, чтобы наблюдать за внутренним поведением и внешними подключениями устройства. Считайте JTAG необходимой поддержкой Вашего проекта.

10. Не используйте внешнее терминирование JTAG для выводов, которые имеют внутреннее терминирование.

Стандарт IEEE 1149.1 явно устанавливает, что JTAG-совместимое устройство должно быть оборудовано сигналами TDI и TMS, которые имеют внутренние верхние подтягивающие (pull-up) резисторы. Для сигналов TCK и TDO нет требований к разрешению существования нескольких топологий тестирования. Однако внешнее терминирование TDI и TMS может быть вредным для эффективности цепочки JTAG, в частности, если Вы подключаете нижние притягивающие резисторы (pull-down) к выводам TDI и TMS. Притяжка pull-down будет пытаться перевести выводы TDI и TMS в смещенное состояние, в сторону уровней порога переключения логики, и сделает выводы более чувствительными к шумам и помехам. Это также увеличит потребление тока устройством. Внешние верхние (pull-up) подтягивающие резисторы также могут увеличить потребляемый ток, так как они окажутся подключенными параллельно с резисторами, предоставленными внутри CPLD, уменьшая тем самым общее сопротивление цепи сигнала JTAG.

11. Убедитесь, что регулятор напряжения предоставляет достаточный ток.

Микросхема CPLD требует достаточного тока при включении. Регуляторы, работающие на пределе нагрузки, могут привести к неправильному конфигурированию CPLD и как следствие сильно повлиять на её поведение. Утилиты оценки энергопотребления (power estimation tools) дают информацию об установившемся поведении, но не оценивают ток потребления при включении. Если Вы выбрали свой регулятор, нацеливая его на значение, вычисленное по проекту (с помощью утилиты XPower, выражения вычисления потребления мощности, или из документации), то может оказаться, что вычисленное значение будет слишком мало. Выбор регулятора лучше всего осуществить экспериментально, для конкретного дизайна, и следует провести исследование во время процесса разработки. Хороший метод - выбрать регулятор, совместимый по выводам с другими существующими регуляторами, имеющими запас по мощности. После этого проверьте, насколько хорошо все работает, как того требует разработка. Запас по мощности также обеспечит возможность изменения разработки в будущем.

12. Если это возможно, подавайте питание на VCCINT перед подачей питания на VCCIO.

Xilinx CPLD не испортятся при любой последовательности подачи напряжений питания, но есть возможность, что сигналы, создаваемые внутри микросхемы, могут при включении питания попасть на другие схемы. Чтобы минимизировать эту возможность, самый простой способ сначала подавать напряжение VCCINT, соблюсти задержку на конфигурирование CPLD и потом подать напряжение VCCIO. При этих условиях питание не будет подано на банк I/O, пока не завершится процесс внутренней конфигурации схемы логики CPLD. Подробности о поведении Xilinx CPLD при включении питания см. в даташите XAPP440.

Дополнительные рекомендации по аппаратуре, касающиеся определенных семейств CPLD:

CoolRunner-II: используйте триггеры Шмитта на входных сигналах, которые переключаются слишком медленно. Медленные шумоподобные сигналы могут ухудшить работу проекта. Высокоскоростные CoolRunner-II CPLD будут захватывать помехи на медленных сигналах, и Ваша система может счесть их за полезные сигналы, которые могут вызвать дополнительные проблемы. Такую проблему проще всего решить простым подключением на входе функции Schmitt Trigger, что "очистит" плохие сигналы, и преобразует их в сигналы с четкими перепадами уровней. ПО разработки и архитектура позволяет выполнять конфигурирование триггера Шмитта для каждого вывода. При разработке проекта поэкспериментируйте с этой функцией.

CoolRunner XPLA3: хорошее понимание сигнала JTAG Port Enable и корректное его использование. Port Enable это специальный вывод CoolRunner XPLA3, который разрешает использование четырех выводов JTAG как ножки I/O место функций интерфейса JTAG. Если Вам не нужны выводы JTAG для программирования или тестирования, то эти четыре вывода можно забрать, но сигнал Port Enable следует использовать соответствующим образом. Подробности см. в даташите XAPP343.

XC9500/XL/XV: использование Low Power Mode на всех не критичных сигналах. Как уже упоминалось, все Xilinx CPLD очень быстрые. Это касается буферного усилителя (sense amp), находящихся в чипах XC9500/XL/XV. Более надежный дизайн потребляет меньше мощности от источника питания, и генерирует меньше шумов переключения. Этого можно достичь с использованием маломощных макроячеек (low power macrocell switches), что задается в ПО разработки. Для включения этой функции используется легкий скоростной сумматор (slight speed adder), так что это должно использоваться только для логики, которая не работает на предельной скорости. Часто это может составить до 80% от всего проекта! Чтобы увеличить выигрыш от снижения энергопотребления и чтобы снизить шум, к low power макроячейкам добавляется гистерезис. ПО разработки может сделать это автоматически, так что Вы можете очень просто поэкспериментировать с функцией Low Power Mode.

[Software, более подробно]

1. Не оставляйте без внимания предупреждения файла отчета.

ПО разработки Xilinx идентифицирует потенциальные проблемы во время компиляции, чтобы помочь Вам в разработке. Ключевой файл отчета носит имя по названию проекта или имени верхнего модуля, и имеет расширение *.rpt. Вы можете свободно открыть его любым просмотрщиком текста или текстовым редактором, и его можно легко просмотреть и проанализировать. Файл отчета называется CPLD report file, в нем содержится общая информация о потреблении ресурсов (resource summary), все выражения (design equations), общие ограничения (constraints), выбранные при компиляции и другая полезная информация (например, установки по умолчанию для компилятора). Это хорошее место, чтобы бросить общий взгляд на то, как программное обеспечение отображает Ваш дизайн на архитектуру CPLD. Также в отчете содержится сводка по предупреждениям (warnings), которые следует прочитать и понять, что они означают.

Независимо от способа создания Вашего проекта (по составленной схеме или с помощью языка HDL), Xilinx fitter модифицирует полученный список цепей в список цепей, специфичный и для архитектуры, и поток данных для программирования (JEDEC bitstream). При выполнении этих действий он анализирует сделанные выборы вариантов, и сообщает Вам об областях возможных проблем в виде списка предупреждений. Анализом этих предупреждений Вы можете определить, где может быть проблема с Вашей разработкой. Для получения самых лучших результатов хорошей идеей будет понять предупреждения, и предпринять для них соответствующие действия, если это необходимо.

2. Используйте строго синхронный дизайн.

Как уже упоминалось, эта рекомендация относится и к проектированию аппаратуры. Но она касается и к области практики программирования, потому что Вы можете в процессе разработки проекта наблюдать, стал ли проект "асинхронным". Из-за неоднозначностей в описаниях HDL и разных интерпретаций между ними, Вы можете думать, что схема синхронна, но позже обнаружите, что это не так! Файл отчета CPLD - хорошее место для анализа точного отображения логики схемы на архитектуру чипа. В особенности пользователи могут проанализировать, сколько используется глобальных тактовых сигналов, где и когда используются асинхронные ресурсы "p-term", и так далее. Убедитесь, что проверили управляемое тактирование логических блоков (gated p-term clocks), которые часто становятся источником проблем. Все это хорошие индикаторы того, что произошло с Вашим дизайном верхнего уровня, когда прошли различные оптимизации. Лучшие результаты получается при модификации на уровне HDL, чтобы улучшить "синхронность" поведения конечного дизайна. Предупреждения тут являются дополнительным плюсом.

3. Разберитесь с ограничениями интервалов времени и соответствующими предупреждениями.

CPLD Timing Report также дает хорошую информацию по общему быстродействию разработки. Кроме файла CPLD Report, данные предоставляются в виде таблиц, по каждой ветви разработки. Общий высокоуровневый отчет дает верхние пределы скорости, идентифицирует узкие места и предоставляет общие предупреждения, так что Вы можете после компиляции оценить общий размер ущерба или доступную дополнительную скорость. Время, потраченное на понимание этого отчета, дает дополнительный выигрыш по затратам времени, потраченного на отладку.

4. Просматривайте выражения CPLD Fitter Report.

Как упоминалось ранее, CPLD Fitter Report ясно показывает, как дизайн отображается на архитектуру. Это отслеживает файл JEDEC. Четкое отображение того, как архитектура обрабатывает важные точки дизайна, помогает быстро изолировать области, которые следует лучше понять или улучшить. Во многих случаях простое инспектирование обзора опций в конце отчета покажет ключевые факторы наподобие низкого энергопотребления, и выбор других простых переключений настроек в ПО разработки.

5. Всегда правильно конфигурируйте сигналы ввода вывода I/O (LVCMOS 3.3, LVCMOS 1.8, и т. д.).

CPLD не знает, с какими уровнями логики нужно работать. Таким образом Вы определяете, какие есть внешние подключения, но также в своем проекте информируете об этом и ПО разработки. ПО будет устанавливать внутренние биты программирования, которые диктуют корректные конфигурации транзисторов на ножках I/O микросхемы, чтобы достичь правильное управление внешними выводами. Это действие находится в зоне ответственности разработчика, поэтому обязательно сделайте правильный выбор.

Примечание: я допустил подобную ошибку, оставив настройки по умолчанию для проекта на поддержку КМОП-логики 1.8V (Default Voltage Standard for All Outputs: LVCMOS18), и при этом задал в файле ограничений *.ucf для некоторых внешних (но не для всех!) выходов систему уровней логики TTL 3.3V (LVTTL). Конечно, это было ошибкой - надо было либо изменить настройку по умолчанию на LVTTL, либо задать в файле UCF для всех выходов одинаковые настройки LVTTL. Для некоторых выводов я это не сделал, и потом долго удивлялся, почему для простой схемы проект не компилировался с сообщением "Ваш дизайн не помещается в ресурсы кристалла".

6. Если возможно, позвольте ПО разработки свободную (без ограничений) привязку внешних выводов чипа.

ПО разработки Xilinx написано таким образом, чтобы дать максимальные возможности для разработчика по управлению трассировкой логики до выводов I/O корпуса чипа (это позволяет упростить разводку печатной платы для конечного устройства), одновременно стараясь уменьшить потребление ресурсов микросхемы. Это означает, что ПО будет намеренно пытаться объединять логику в кластеры внутри функциональных блоков, чтобы максимально повторно использовать сигналы. Также будет сделана попытка избежать чрезмерного использования входов функциональных блоков и ресурсов логики, чтобы они были доступны в случае необходимости в будущих изменениях дизайна. В частности, это критично для разработок, которые работают многие годы в готовых устройствах, и при этом есть возможность поддерживать многие ревизии логики в соответствии с меняющимися условиями техзадания. Вы должны принять решение, давать ли программному обеспечению возможность самому делать распределение входов и выходов логики по выводам кристалла (что возможно усложнит разводку платы, но зато освободит ресурсы CPLD и потенциально повысит производительность), либо задать жесткие ограничения (что упростит плату, но усложнит для ПО условия по трассировке логики по кристаллу и займет дополнительные ресурсы). Помните, что в ПО разработки аккумулирован многолетний опыт работы множества специалистов, и если это возможно, полагайтесь на свободный выбор и управление ресурсами со стороны системы синтеза, компиляции и размещения на кристалле.

7. Очень полезно проводить симуляцию дизайна.

Симуляция проекта предоставляет возможность оценить его в работе под моделью ожидаемой рабочей нагрузки. Моделирование может идентифицировать проблемы с интервалами времени, которые были пропущены в в файлах отчета времени и размещения (timing report, fitter report), потому что эти отчеты основаны на "статической" модели дизайна. Это может также использоваться для проверки функционирования при изменяющихся рабочих условиях. Например, когда дизайн работает при низких температурах, устройство имеет тенденцию работать быстрее. И наоборот, при высокой температуре медленнее. Можно выбрать различные варианты имеющейся модели кристалла по быстродействию (speed grade), и запустить симуляцию с различными speed grade, чтобы понять поведение устройства по модели в "горячих" и "холодных" условиях. Когда осуществляется моделирование по такому методу, асинхронное поведение может показать новое функционирование устройства. В целом симуляция это довольно большая работа, но часто эта работа оказывается меньше, чем отладка и поиск ошибок в плохо разработанном проекте.

[Ссылки]

1. XAPP784 Bulletproof CPLD Design Practices site:xilinx.com.

2. CoolRunner II site:xilinx.com (документация, апноуты и статьи). |