|

–°–µ–≥–Њ–і–љ—П –∞–њ–њ–∞—А–∞—В—Г—А–∞ —А–∞–Ј—А–∞–±–∞—В—Л–≤–∞–µ—В—Б—П –љ–∞ –≤—Л—Б–Њ–Ї–Њ—Г—А–Њ–≤–љ–µ–≤—Л—Е —П–Ј—Л–Ї–∞—Е, –Њ–±–ї–∞—Б—В–Є —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –∞–њ–њ–∞—А–∞—В—Г—А—Л –Є –Я–Ю —Б—В—А–µ–Љ—П—В—Б—П –Ї —Б–ї–Є—П–љ–Є—О. –Т —Н—В–Њ–є —Б—В–∞—В—М–µ —Б–і–µ–ї–∞–љ–∞ –њ–Њ–њ—Л—В–Ї–∞ –≤–≤–µ–і–µ–љ–Є—П –≤ —А–∞–Ј—А–∞–±–Њ—В–Ї—Г –љ–∞ Verilog –і–ї—П —В–µ—Е, –Ї—В–Њ –њ–Њ–Ї–∞ —З—В–Њ –љ–µ —Б–Є–ї—М–љ–Њ –≤ —В–µ–Љ–µ (–њ–µ—А–µ–≤–Њ–і [1]).

–Т –±–ї–Є–ґ–∞–є—И–µ–Љ –±—Г–і—Г—Й–µ–Љ —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–Є –≤—Б—В—А–∞–Є–≤–∞–µ–Љ—Л—Е —Б–Є—Б—В–µ–Љ –±—Г–і—Г—В —Б–њ–Њ—Б–Њ–±–љ—Л –≤–Ј–∞–Є–Љ–Њ–Ј–∞–Љ–µ–љ—П–µ–Љ–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –ґ–µ–ї–µ–Ј–Њ –Є –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–µ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В —В–Њ–≥–Њ, –Ї–∞–Ї–Њ–є –Є–Ј —Б–њ–Њ—Б–Њ–±–Њ–≤ —А–µ—И–µ–љ–Є—П –Ј–∞–і–∞—З –ї—Г—З—И–µ –њ–Њ–Љ–Њ–ґ–µ—В –і–ї—П —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є —В–µ—Е–Ј–∞–і–∞–љ–Є—П. –Ф–Њ –љ–∞—Б—В–Њ—П—Й–µ–≥–Њ –Љ–Њ–Љ–µ–љ—В–∞ –Ї—А–Є–≤–∞—П —Б–ї–Њ–ґ–љ–Њ—Б—В–Є –Є–Ј—Г—З–µ–љ–Є—П –≤–Њ–њ—А–Њ—Б–∞ —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –ґ–µ–ї–µ–Ј–∞ –±—Л–ї–∞ —Б–ї–Є—И–Ї–Њ–Љ –Ї—А—Г—В–∞, —З—В–Њ–±—Л –≤ –љ–µ—С –Љ–Њ–≥–ї–Є –Њ–Ї—Г–љ—Г—В—М—Б—П –Њ–њ—Л—В–љ—Л–µ —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–Є –≤—Б—В—А–Њ–µ–љ–љ–Њ–≥–Њ –Я–Ю. –Э–Њ —Н—В–Њ—В –±–∞—А—М–µ—А –њ–Њ—Б—В–µ–њ–µ–љ–љ–Њ —А—Г—И–Є—В—Б—П –Є–Ј-–Ј–∞ —В–Њ–≥–Њ, —З—В–Њ —П–Ј—Л–Ї–Є –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П –∞–њ–њ–∞—А–∞—В—Г—А—Л —Б—В—А–µ–Љ—П—В—Б—П –±—Л—В—М –њ–Њ—Е–Њ–ґ–Є–Љ–Є –љ–∞ —В—А–∞–і–Є—Ж–Є–Њ–љ–љ—Л–µ —П–Ј—Л–Ї–Є –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П. –Ґ–∞–Ї–ґ–µ —Б—В–∞–љ–Њ–≤—П—В—Б—П –і–Њ—Б—В—Г–њ–љ—Л–Љ–Є –њ–Њ —Ж–µ–љ–µ –љ–µ–і–Њ—А–Њ–≥–Є–µ –і–µ–Љ–Њ–љ—Б—В—А–∞—Ж–Є–Њ–љ–љ—Л–µ –њ–ї–∞—В—Л, –Ї–Њ—В–Њ—А—Л–µ –Є–Љ–µ—О—В –љ–∞ –±–Њ—А—В—Г –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Г—О –Љ–Є–Ї—А–Њ—Б—Е–µ–Љ—Г –ї–Њ–≥–Є–Ї–Є (—Н—В–Њ –Љ–Њ–ґ–µ—В –±—Л—В—М –Љ–Њ—Й–љ–∞—П —Б—Е–µ–Љ–∞ field-programmable gate array, FPGA –Є–ї–Є –Љ–µ–љ–µ–µ –Љ–Њ—Й–љ–∞—П CPLD), –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А, –Є–Љ–µ—О—В—Б—П –≤ –љ–∞–ї–Є—З–Є–Є –љ–µ–і–Њ—А–Њ–≥–Є–µ –њ—А–Њ–≥—А–∞–Љ–Љ–∞—В–Њ—А—Л JTAG –Є –±–µ—Б–њ–ї–∞—В–љ—Л–µ –Є–љ—Б—В—А—Г–Љ–µ–љ—В—Л —А–∞–Ј—А–∞–±–Њ—В–Ї–Є (–Ї–∞–Ї –љ–∞–њ—А–Є–Љ–µ—А Xilinx ISE WebPack [2]). –Т—Б–µ —Н—В–Њ –њ–Њ–Ј–≤–Њ–ї—П–µ—В —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–∞–Љ –≤—Б—В—А–∞–Є–≤–∞–µ–Љ–Њ–≥–Њ firmware –љ–∞—З–∞—В—М –Є–Ј—Г—З–∞—В—М –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є–µ —Ж–Є—Д—А–Њ–≤–Њ–є –∞–њ–њ–∞—А–∞—В—Г—А—Л.

–Т —Н—В–Њ–є —Б—В–∞—В—М–µ –њ—А–µ–і–Њ—Б—В–∞–≤–ї–µ–љ –њ—А–Є–Љ–µ—А, –Ї–∞–Ї –≤—Л–њ–Њ–ї–љ–Є—В—М –љ–Њ–≤—Г—О —А–∞–Ј—А–∞–±–Њ—В–Ї—Г —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ FPGA. –С—Г–і–µ—В –њ–Њ–Ї–∞–Ј–∞–љ–∞ —А–µ–∞–ї–Є–Ј–∞—Ж–Є—П —И–Є—А–Њ—В–љ–Њ-–Є–Љ–њ—Г–ї—М—Б–љ–Њ–є –Љ–Њ–і—Г–ї—П—Ж–Є–Є, –®–Ш–Ь (pulse width modulation, PWM) –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ, –Є –Ј–∞—В–µ–Љ –±—Г–і–µ—В –њ—А–Њ–Є–Ј–≤–µ–і–µ–љ –њ–Њ—А—В–Є—А–Њ–≤–∞–љ–Є–µ –і–Є–Ј–∞–є–љ–∞ –≤ –ї–Њ–≥–Є—З–µ—Б–Ї–Є–є –±–ї–Њ–Ї, –Ї–Њ—В–Њ—А—Л–є –Љ–Њ–ґ–µ—В –±—Л—В—М –Ј–∞–њ—Г—Й–µ–љ –≤ FPGA, –Є —Г–њ—А–∞–≤–ї—П—В—М—Б—П –њ—А–Њ–≥—А–∞–Љ–Љ–љ—Л–Љ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ–Љ —З–µ—А–µ–Ј –Њ—В–Њ–±—А–∞–ґ–µ–љ–љ—Л–є –љ–∞ –њ–∞–Љ—П—В—М –Є–љ—В–µ—А—Д–µ–є—Б –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ (I/O). –Т—Л –Љ–Њ–ґ–µ—В–µ –њ–Њ–≤—В–Њ—А–Є—В—М –≤—Б–µ –і–µ–є—Б—В–≤–Є—П –≤ —Н—В–Њ–є —Б—В–∞—В—М–µ —Б –ї—О–±—Л–Љ –Ї–Є—В–Њ–Љ —А–∞–Ј—А–∞–±–Њ—В–Ї–Є FPGA, –Ї–Њ—В–Њ—А—Л–µ –њ—А–µ–і–Њ—Б—В–∞–≤–ї—П—О—В —Б–µ–≥–Њ–і–љ—П –Њ—Б–љ–Њ–≤–љ—Л–µ —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–Є FPGA (–Њ—Б–Њ–±–µ–љ–љ–Њ –њ–Њ–њ—Г–ї—П—А–љ—Л Xilinx –Є Altera), –Є —В–∞–Ї–ґ–µ –≤ –Є–Ј–Њ–±–Є–ї–Є–Є –Љ–Њ–ґ–љ–Њ –Ї—Г–њ–Є—В—М —З–µ—А–µ–Ј –Ш–љ—В–µ—А–љ–µ—В –≤ –Љ–∞–≥–∞–Ј–Є–љ–µ AliExpress.

[–†–∞–Ј–і–µ–ї–µ–љ–Є–µ –Љ–µ–ґ–і—Г –ґ–µ–ї–µ–Ј–Њ–Љ –Є –Я–Ю]

–Х—Б—В—М –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ —Д–∞–Ї—В–Њ—А–Њ–≤, —Г–њ—А–Њ—Й–∞—О—Й–Є—Е –і–ї—П –њ—А–Њ–≥—А–∞–Љ–Љ–Є—Б—В–Њ–≤ —Г—З–∞—Б—В–Є–µ –≤ —А–∞–Ј—А–∞–±–Њ—В–Ї–µ –∞–њ–њ–∞—А–∞—В—Г—А—Л. –Ш –і–ї—П –ґ–µ–ї–µ–Ј–∞, –Є –і–ї—П –Я–Ю –Љ–Њ–і—Г–ї–Є –Ї–Њ–і–∞ —А–∞–Ј—А–∞–±–∞—В—Л–≤–∞—О—В—Б—П —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ —П–Ј—Л–Ї–Њ–≤ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П. –Ъ–∞–Ї –Т—Л –Ј–љ–∞–µ—В–µ, —П–Ј—Л–Ї C —П–≤–ї—П–µ—В—Б—П –Њ–±—Й–µ–њ—А–Є–љ—П—В—Л–Љ –≤ –Љ–Є—А–µ —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –≤—Б—В—А–∞–Є–≤–∞–µ–Љ–Њ–≥–Њ –Я–Ю (embedded software, –Є–ї–Є firmware). –Э–∞ —Б—В–Њ—А–Њ–љ–µ —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –ґ–µ–ї–µ–Ј–∞ Verilog —З–∞—Б—В–Њ —П–≤–ї—П–µ—В—Б—П –њ–Њ–њ—Г–ї—П—А–љ—Л–Љ –≤—Л–±–Њ—А–Њ–Љ (—Е–Њ—В—П VHDL –Є Verilog –Њ–±–∞ –Њ–і–Є–љ–∞–Ї–Њ–≤–Њ –њ–Њ–њ—Г–ї—П—А–љ—Л, –Є –Є–Љ–µ—О—В –Ї–∞–ґ–і—Л–є —Б–≤–Њ–Є—Е —Б—В–Њ—А–Њ–љ–љ–Є–Ї–Њ–≤). –°–Є–љ—В–∞–Ї—Б–Є—Б –Є —Б—В—А—Г–Ї—В—Г—А–∞ Verilog –њ–Њ–і–Њ–±–љ–∞ —П–Ј—Л–Ї—Г C, —З—В–Њ –љ–∞ –њ—А–Є–Љ–µ—А–∞—Е –±—Г–і–µ—В –њ–Њ–Ї–∞–Ј–∞–љ–Њ –≤ —Н—В–Њ–є —Б—В–∞—В—М–µ.

–Т —В–Њ –ґ–µ –≤—А–µ–Љ—П –ґ–µ–ї–µ–Ј–Њ —Б—В–∞–ї–Њ –і–Њ—Б—В—Г–њ–љ–Њ –і–ї—П –њ—А–Њ—Б—В–Њ–≥–Њ –Њ–±–љ–Њ–≤–ї–µ–љ–Є—П –Є –Є–Ј–Љ–µ–љ–µ–љ–Є—П. –Я—А–Њ—И–ї–Є –≤—А–µ–Љ–µ–љ–∞, –Ї–Њ–≥–і–∞ —В–Њ–ї—М–Ї–Њ –њ–Њ–≤–µ–і–µ–љ–Є–µ –Я–Ю –Љ–Њ–ґ–љ–Њ –±—Л–ї–Њ –ї–µ–≥–Ї–Њ –Є–Ј–Љ–µ–љ–Є—В—М –њ—Г—В–µ–Љ –≤–љ–µ—Б–µ–љ–Є—П –њ—А–∞–≤–Ї–Є –≤ –Ї–Њ–і, –њ–µ—А–µ–Ї–Њ–Љ–њ–Є–ї—П—Ж–Є–Є –Є –Ј–∞–≥—А—Г–Ј–Ї–Є –љ–Њ–≤–Њ–≥–Њ –Є—Б–њ–Њ–ї–љ—П–µ–Љ–Њ–≥–Њ –Њ–±—А–∞–Ј–∞ –≤ –њ–∞–Љ—П—В—М —Б–Є—Б—В–µ–Љ—Л. –Ґ–µ–њ–µ—А—М –њ—А–Є–Љ–µ—А–љ–Њ —В–Њ –ґ–µ —Б–∞–Љ–Њ–µ –Љ–Њ–ґ–љ–Њ –і–µ–ї–∞—В—М –Є –і–ї—П –∞–њ–њ–∞—А–∞—В–љ–Њ–≥–Њ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П - –Љ–Њ–ґ–љ–Њ –±—Л—Б—В—А–Њ –Є—Б–њ—А–∞–≤–Є—В—М –Є—Б—Е–Њ–і–љ—Л–є –Ї–Њ–і, –≤—Л–њ–Њ–ї–љ–Є—В—М –µ–≥–Њ –њ–Њ–≤—В–Њ—А–љ—Л–є —Б–Є–љ—В–µ–Ј, –Є –Ј–∞–≥—А—Г–Ј–Є—В—М —Б–≥–µ–љ–µ—А–Є—А–Њ–≤–∞–љ–љ—Л–є –њ–Њ—В–Њ–Ї –±–Є—В –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –≤ –њ–∞–Љ—П—В—М FPGA —Б–Є—Б—В–µ–Љ—Л. –Я—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–∞—П –ї–Њ–≥–Є–Ї–∞ –њ–Њ–Ј–≤–Њ–ї–Є–ї–∞ –≤ —А–∞–Ј—А–∞–±–Њ—В–Ї–µ –≤—Б—В—А–∞–Є–≤–∞–µ–Љ—Л—Е —Б–Є—Б—В–µ–Љ —В–∞–Ї –ґ–µ –±—Л—Б—В—А–Њ –Є –њ—А–Њ—Б—В–Њ –Љ–µ–љ—П—В—М –∞–њ–њ–∞—А–∞—В—Г—А—Г, –Ї–∞–Ї —Н—В–Њ –і–µ–ї–∞–ї–Њ—Б—М —Б –њ—А–Њ–≥—А–∞–Љ–Љ–љ—Л–Љ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ–Љ. –Ф—А—Г–≥–Є–Љ–Є —Б–ї–Њ–≤–∞–Љ–Є, —Н—В–Њ –і–Њ–±–∞–≤–ї—П–µ—В –≥–Є–±–Ї–Њ—Б—В–Є –Є —Н—Д—Д–µ–Ї—В–Є–≤–љ–Њ—Б—В–Є –≤ —А–∞–Ј—А–∞–±–Њ—В–Ї–µ - –њ–Њ—П–≤–Є–ї–Њ—Б—М –±–Њ–ї—М—И–µ –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В–µ–є –і–ї—П —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є —А–∞–Ј–ї–Є—З–љ—Л—Е –Ј–∞–і–∞—З. –Э–µ–Ї–Њ—В–Њ—А—Л–µ —Д—Г–љ–Ї—Ж–Є–Є –Љ–Њ–ґ–љ–Њ –њ–µ—А–µ–ї–Њ–ґ–Є—В—М –љ–∞ –∞–њ–њ–∞—А–∞—В—Г—А—Г, –∞ –љ–µ–Ї–Њ—В–Њ—А—Л–µ –љ–∞ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–µ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ.

–Ш–љ—Б—В—А—Г–Љ–µ–љ—В—Л —А–∞–Ј—А–∞–±–Њ—В–Ї–Є, –і–Њ—Б—В—Г–њ–љ—Л–µ –Њ—В –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї–µ–є FPGA, –њ—А–µ–і—К—П–≤–ї—П—О—В –Ї —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї—Г –Љ–Є–љ–Є–Љ—Г–Љ —В—А–µ–±–Њ–≤–∞–љ–Є–є –њ–Њ –Ј–љ–∞–љ–Є—О –∞–њ–њ–∞—А–∞—В–љ–Њ–≥–Њ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П, —З—В–Њ–±—Л –њ—А–Є–Љ–µ–љ—П—В—М –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Г—О –ї–Њ–≥–Є–Ї—Г, —В–∞–Ї—Г—О –Ї–∞–Ї FPGA, –≤ —А–∞–Ј—А–∞–±–Њ—В–Ї–µ –≤—Б—В—А–∞–Є–≤–∞–µ–Љ—Л—Е —Б–Є—Б—В–µ–Љ. –Э–∞–њ—А–Є–Љ–µ—А, SOPC Builder –Њ—В –Ї–Њ–Љ–њ–∞–љ–Є–Є Altera –њ–Њ–Ј–≤–Њ–ї—П–µ—В —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–∞–Љ —Б–Є—Б—В–µ–Љ –≤—Л–±—А–∞—В—М –Є —Б–Ї–Њ–љ—Д–Є–≥—Г—А–Є—А–Њ–≤–∞—В—М –њ–µ—А–Є—Д–µ—А–Є–є–љ—Л–µ —Г—Б—В—А–Њ–є—Б—В–≤–∞ –Є–Ј —Б—Г—Й–µ—Б—В–≤—Г—О—Й–µ–є –±–Є–±–ї–Є–Њ—В–µ–Ї–Є. –Ґ–∞–Ї–ґ–µ –Љ–Њ–ґ–љ–Њ –і–Њ–±–∞–≤–Є—В—М –ї–Њ–≥–Є–Ї—Г –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—П, —З—В–Њ–±—Л –њ–Њ–і–Ї–ї—О—З–Є—В—М –Ї –љ–µ–є –њ–µ—А–Є—Д–µ—А–Є–є–љ—Л–µ —Г—Б—В—А–Њ–є—Б—В–≤–∞. –° –њ–Њ–Љ–Њ—Й—М—О –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–Њ–є –ї–Њ–≥–Є–Ї–Є –Є –љ–µ–Ї–Њ—В–Њ—А—Л–Љ–Є –Ј–љ–∞–љ–Є—П–Љ–Є —Б–њ–µ—Ж–Є—Д–Є–Ї–Є –ґ–µ–ї–µ–Ј–∞ —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–Є –Я–Ю –Љ–Њ–≥—Г—В –≤ —Б–≤–Њ–Є—Е –Є–љ—В–µ—А–µ—Б–∞—Е –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –њ—А–µ–Є–Љ—Г—Й–µ—Б—В–≤–∞ –∞–њ–њ–∞—А–∞—В–љ—Л—Е —Б—А–µ–і—Б—В–≤, —З—В–Њ–±—Л —Г–ї—Г—З—И–Є—В—М –Є—Е –њ—А–Њ–µ–Ї—В–Є—А—Г–µ–Љ—Л–µ —Б–Є—Б—В–µ–Љ—Л.

[–Я—А–Њ–≥—А–∞–Љ–Љ–љ–∞—П —А–µ–∞–ї–Є–Ј–∞—Ж–Є—П PWM]

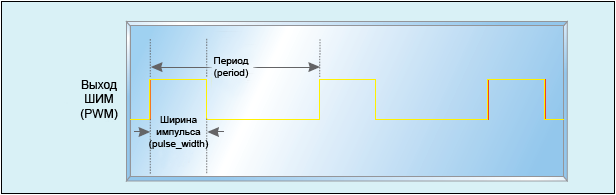

–Ъ–Њ–љ—В—А–Њ–ї–ї–µ—А PWM (–®–Ш–Ь) –≥–µ–љ–µ—А–Є—А—Г–µ—В –њ–Њ—В–Њ–Ї –Є–Љ–њ—Г–ї—М—Б–Њ–≤, –њ—А–Є–Љ–µ—А–љ–Њ —В–∞–Ї–Є—Е, –Ї–∞–Ї –њ–Њ–Ї–∞–Ј–∞–љ—Л –љ–∞ —А–Є—Б. 1. –®–Ш–Ь —Е–∞—А–∞–Ї—В–µ—А–Є–Ј—Г–µ—В—Б—П –њ–µ—А–Є–Њ–і–Њ–Љ –Є –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В—М—О –Є–Љ–њ—Г–ї—М—Б–∞ –Є–ї–Є —Б–Ї–≤–∞–ґ–љ–Њ—Б—В—М—О, —В. –µ. —Б–Њ–Њ—В–љ–Њ—И–µ–љ–Є–µ–Љ –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В–µ–є –ї–Њ–≥. 0 –Є –ї–Њ–≥. 1 –≤ –њ–µ—А–Є–Њ–і–µ. –°–Ї–≤–∞–ґ–љ–Њ—Б—В—М –Њ–њ—А–µ–і–µ–ї—П–µ—В —Г—А–Њ–≤–µ–љ—М –∞–љ–∞–ї–Њ–≥–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞, –Ї–Њ—В–Њ—А—Л–є –њ–Њ—П–≤–ї—П–µ—В—Б—П –љ–∞ –≤—Л—Е–Њ–і–µ –§–Э–І. –†–Є—Б. 1 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В —Д–Њ—А–Љ—Г —Б–Є–≥–љ–∞–ї–∞ –®–Ш–Ь —Б–Њ —Б–Ї–≤–∞–ґ–љ–Њ—Б—В—М—О 33%, —В. –µ. —В–∞–Ї–∞—П —Д–Њ—А–Љ–∞ —Б–Є–≥–љ–∞–ї–∞ –њ–Њ–Ј–≤–Њ–ї—П–µ—В —Б—Д–Њ—А–Љ–Є—А–Њ–≤–∞—В—М –∞–љ–∞–ї–Њ–≥–Њ–≤—Л–є —Б–Є–≥–љ–∞–ї —Б —Г—А–Њ–≤–љ–µ–Љ 33% –Њ—В –Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ–Њ–≥–Њ.

–†–Є—Б. 1. –§–Њ—А–Љ–∞ –≤—Л—Е–Њ–і–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –®–Ш–Ь.

–®–Ш–Ь –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –≤–Њ –Љ–љ–Њ–≥–Є—Е –њ—А–Є–ї–Њ–ґ–µ–љ–Є—П—Е, —З–∞—Й–µ –≤—Б–µ–≥–Њ –і–ї—П —Г–њ—А–∞–≤–ї–µ–љ–Є—П –∞–љ–∞–ї–Њ–≥–Њ–≤—Л–Љ–Є —Б—Е–µ–Љ–∞–Љ–Є. –Ш–Ј-–Ј–∞ —В–Њ–≥–Њ, —З—В–Њ —Ж–Є—Д—А–Њ–≤–Њ–є —Б–Є–≥–љ–∞–ї –®–Ш–Ь –њ–Њ—Б—В–Њ—П–љ–љ–Њ –Є –і–Њ—Б—В–∞—В–Њ—З–љ–Њ —З–∞—Б—В–Њ –Љ–µ–љ—П–µ—В —Б–≤–Њ–µ –Ј–љ–∞—З–µ–љ–Є–µ (–Ї–Њ–љ–µ—З–љ–Њ, –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В –њ–µ—А–Є–Њ–і–∞ –®–Ш–Ь), —В–Њ —А–µ–Ј—Г–ї—М—В–Є—А—Г—О—Й–Є–є —Б–Є–≥–љ–∞–ї –±—Г–і–µ—В –Є–Љ–µ—В—М –љ–µ–Ї–Њ–µ —Б—А–µ–і–љ–µ–µ –Ј–љ–∞—З–µ–љ–Є–µ, –Ј–∞–≤–Є—Б—П—Й–µ–µ –Њ—В —Б–Ї–≤–∞–ґ–љ–Њ—Б—В–Є, –Ї–Њ—В–Њ—А–Њ–µ –Љ–Њ–ґ–љ–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –і–ї—П —Г–њ—А–∞–≤–ї–µ–љ–Є—П –∞–љ–∞–ї–Њ–≥–Њ–≤—Л–Љ —Г—Б—В—А–Њ–є—Б—В–≤–Њ–Љ –Є–ї–Є –і–ї—П –≥–µ–љ–µ—А–∞—Ж–Є–Є –Ј–≤—Г–Ї–∞. –Э–∞–њ—А–Є–Љ–µ—А, –њ–Њ—В–Њ–Ї –Є–Љ–њ—Г–ї—М—Б–Њ–≤ –®–Ш–Ь –Љ–Њ–ґ–µ—В –±—Л—В—М –Њ—В–њ—А–∞–≤–ї–µ–љ –љ–∞ –Љ–Њ—В–Њ—А, –Є –µ–≥–Њ –≤—Л—Е–Њ–і–љ–∞—П –Љ–Њ—Й–љ–Њ—Б—В—М –љ–∞ –≤–∞–ї—Г –±—Г–і–µ—В –њ—А–Њ–њ–Њ—А—Ж–Є–Њ–љ–∞–ї—М–љ–∞ —Б–Ї–≤–∞–ґ–љ–Њ—Б—В–Є (–Њ—В 0% –і–Њ 100%). –Х—Б–ї–Є —Б–Ї–≤–∞–ґ–љ–Њ—Б—В—М —Г–≤–µ–ї–Є—З–Є–≤–∞–µ—В—Б—П, –Љ–Њ—В–Њ—А –Ї—А—Г—В–Є—В—Б—П –±—Л—Б—В—А–µ–µ, –Є –љ–∞–Њ–±–Њ—А–Њ—В, —Б –њ–Њ–љ–Є–ґ–µ–љ–Є–µ–Љ —Б–Ї–≤–∞–ґ–љ–Њ—Б—В–Є –Љ–Њ—В–Њ—А –Ј–∞–Љ–µ–і–ї—П–µ—В—Б—П.

–Ю–±—Л—З–љ–Њ –≤—Л—Б–Њ–Ї–Њ—З–∞—Б—В–Њ—В–љ—Л–є –®–Ш–Ь —Г–і–Њ–±–љ–µ–µ –≤—Б–µ–≥–Њ —А–µ–∞–ї–Є–Ј–Њ–≤–∞—В—М –∞–њ–њ–∞—А–∞—В–љ–Њ, –њ–Њ—В–Њ–Љ—Г —З—В–Њ –і–ї—П —Д–Њ—А–Љ–Є—А–Њ–≤–∞–љ–Є—П –Є–Љ–њ—Г–ї—М—Б–Њ–≤ –љ—Г–ґ–љ—Л –њ–Њ—Б—В–Њ—П–љ–љ–Њ (—Б –Ї–∞–ґ–і—Л–Љ –њ–µ—А–Є–Њ–і–Њ–Љ) –њ–Њ–≤—В–Њ—А—П—О—Й–Є–µ—Б—П –њ—А–Њ—Б—В—Л–µ –і–µ–є—Б—В–≤–Є—П. –С–Њ–ї—М—И–Є–љ—Б—В–≤–Њ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–≤ –Є–Љ–µ–µ—В –і–ї—П —Н—В–Њ–≥–Њ –љ–∞ –±–Њ—А—В—Г —Б–њ–µ—Ж–Є–∞–ї—М–љ—Л–µ —В–∞–є–Љ–µ—А—Л-—Б—З–µ—В—З–Є–Ї–Є. –Я—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–µ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ –њ—А–Њ—Б—В–Њ –≤—Л—З–Є—Б–ї—П–µ—В –Є–љ—В–µ—А–≤–∞–ї—Л –≤—А–µ–Љ–µ–љ–Є –ї–Њ–≥. 0 –Є–ї–Є –ї–Њ–≥. 1 —Д–Є–Ї—Б–Є—А–Њ–≤–∞–љ–љ–Њ–≥–Њ –њ–µ—А–Є–Њ–і–∞, –Є –њ–µ—А–µ–і–∞–µ—В –Є—Е –≤ –∞–њ–њ–∞—А–∞—В—Г—А—Г, —З—В–Њ –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Љ–µ–љ—П—В—М —Б–Ї–≤–∞–ґ–љ–Њ—Б—В—М –®–Ш–Ь –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ.

–Ю–і–љ–∞–Ї–Њ –љ–µ—В –љ–Є–Ї–∞–Ї–Є—Е –њ—А–Є—З–Є–љ –љ–µ —А–µ–∞–ї–Є–Ј–Њ–≤–∞—В—М –≤ –љ–µ–Ї–Њ—В–Њ—А—Л—Е —Б–ї—Г—З–∞—П—Е –®–Ш–Ь —З–Є—Б—В–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ, –љ–∞–њ—А–Є–Љ–µ—А –њ—А–Њ—Б—В—Л–Љ –њ–µ—А–µ–Ї–ї—О—З–µ–љ–Є–µ–Љ —Г—А–Њ–≤–љ—П –љ–∞ –љ–Њ–ґ–Ї–µ –њ–Њ—А—В–∞ –≤—Л–≤–Њ–і–∞. –Ч–∞–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞—В—М —В–∞–Ї–Њ–є –®–Ш–Ь-–Ї–Њ–љ—В—А–Њ–ї–µ—А –Њ—В–љ–Њ—Б–Є—В–µ–ї—М–љ–Њ –њ—А–Њ—Б—В–Њ, –Є —Н—В–Њ –њ–Њ–Љ–Њ–ґ–µ—В –љ–∞–Љ –≤ –±—Г–і—Г—Й–µ–Љ –њ—А–Є —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є —В–Њ–≥–Њ –ґ–µ –®–Ш–Ь –љ–∞ Verilog. –Ы–Є—Б—В–Є–љ–≥ 1 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –Ї–Њ–і –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–є —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є –®–Ш–Ь –љ–∞ —П–Ј—Л–Ї–µ C.

–Ы–Є—Б—В–Є–љ–≥ 1. PWM-–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А, —А–∞–±–Њ—В–∞—О—Й–Є–є –њ–Њ –њ—А–Є–љ—Ж–Є–њ—Г "bit-bang", —В. –µ. –і–µ—А–≥–∞–љ–Є–µ–Љ –ї–Њ–≥–Є—З–µ—Б–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П –љ–∞ –љ–Њ–ґ–Ї–µ –њ–Њ—А—В–∞ –≤—Л–≤–Њ–і–∞.

// pulse_width: —И–Є—А–Є–љ–∞ –Є–Љ–њ—Г–ї—М—Б–∞ –®–Ш–Ь

// period: –њ–µ—А–Є–Њ–і –®–Ш–Ь

void pwmTask(uint32_t pulse_width, uint32_t period)

{

uint32_t time_on = pulse_width;

uint32_t time_off = period - pulse_width;

while (1)

{

pwm_output = 1;

sleep(time_on);

pwm_output = 0;

sleep(time_off);

}

}

–Э–∞ –Њ—Б–љ–Њ–≤–µ –∞—А–≥—Г–Љ–µ–љ—В–Њ–≤ —Н—В–Њ–є —Д—Г–љ–Ї—Ж–Є–Є pulse_width –Є period –≤—Л—З–Є—Б–ї—П–µ—В—Б—П –Ї–Њ–ї–Є—З–µ—Б—В–≤–Њ –≤—А–µ–Љ–µ–љ–Є, –Ї–Њ–≥–і–∞ –≤—Л—Е–Њ–і pwm_output –љ–∞—Е–Њ–і–Є—В—Б—П –≤ —Б–Њ—Б—В–Њ—П–љ–Є–Є –ї–Њ–≥. 1 –Є –ї–Њ–≥. 0. –Т –±–µ—Б–Ї–Њ–љ–µ—З–љ–Њ–Љ —Ж–Є–Ї–ї–µ –≤—Л—Е–Њ–і pwm_output –њ–Њ—Б—В–Њ—П–љ–љ–Њ –њ–µ—А–µ–Ї–ї—О—З–∞–µ—В—Б—П, –Є –≤ —В–µ—З–µ–љ–Є–µ time_on –µ–і–Є–љ–Є—Ж –≤—А–µ–Љ–µ–љ–Є –љ–∞ –≤—Л—Е–Њ–і–µ –ї–Њ–≥. 1, –Є –≤ —В–µ—З–µ–љ–Є–µ time_off –µ–і–Є–љ–Є—Ж –≤—А–µ–Љ–µ–љ–Є –≤—Л—Е–Њ–і –љ–∞—Е–Њ–і–Є—В—Б—П –≤ —Б–Њ—Б—В–Њ—П–љ–Є–Є –ї–Њ–≥. 0, —З—В–Њ –Њ–њ—А–µ–і–µ–ї—П–µ—В —Б–Ї–≤–∞–ґ–љ–Њ—Б—В—М –®–Ш–Ь –љ–∞ –≤—Л—Е–Њ–і–µ –Є –≤ –Ї–Њ–љ–µ—З–љ–Њ–Љ –Є—В–Њ–≥–µ —Б—А–µ–і–љ–Є–є —Г—А–Њ–≤–µ–љ—М —Д–Њ—А–Љ–Є—А—Г–µ–Љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞.

[–†–µ–∞–ї–Є–Ј–∞—Ж–Є—П –®–Ш–Ь –љ–∞ Verilog]

–Ы–Є—Б—В–Є–љ–≥ 2 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –њ—А–Њ—Б—В–Њ–є –Љ–Њ–і—Г–ї—М Verilog, —А–µ–∞–ї–Є–Ј—Г—О—Й–Є–є 8-–±–Є—В–љ—Л–є —А–µ–≥–Є—Б—В—А —Б –∞—Б–Є–љ—Е—А–Њ–љ–љ—Л–Љ —Б–±—А–Њ—Б–Њ–Љ. –Т—Е–Њ–і —А–µ–≥–Є—Б—В—А–∞ in –њ—А–Є—Б–≤–∞–Є–≤–∞–µ—В—Б—П –≤—Л—Е–Њ–і—Г out –њ–Њ —Д—А–Њ–љ—В—Г –љ–∞—А–∞—Б—В–∞–љ–Є—П —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞, –Ї—А–Њ–Љ–µ —Б–ї—Г—З–∞–µ–≤ —Б–њ–∞–і–∞ —Б–Є–≥–љ–∞–ї–∞ —Б–±—А–Њ—Б–∞ clr_n reset, —В–Њ–≥–і–∞ –≤—Л—Е–Њ–і—Г –љ–∞–Ј–љ–∞—З–∞–µ—В—Б—П –Ј–љ–∞—З–µ–љ–Є–µ 0.

–Ы–Є—Б—В–Є–љ–≥ 2. –Ь–Њ–і—Г–ї—М Verilog –і–ї—П —А–µ–≥–Є—Б—В—А–∞ —Б –∞—Б–Є–љ—Е—А–Њ–љ–љ—Л–Љ —Б–±—А–Њ—Б–Њ–Љ.

module simple_register(in, out, clr_n, clk, a);

// –Ф–µ–Ї–ї–∞—А–∞—Ж–Є–Є –њ–Њ—А—В–Њ–≤.

input clr_n;

input clk;

input [7:0] in;

input a;

output [7:0] out;

// –Ф–µ–Ї–ї–∞—А–∞—Ж–Є–Є —Б–Є–≥–љ–∞–ї–Њ–≤.

reg [7:0] out;

wire a;

// –†–µ–∞–ї–Є–Ј–∞—Ж–Є—П —А–µ–≥–Є—Б—В—А–∞ —Б –∞—Б–Є–љ—Е—А–Њ–љ–љ—Л–Љ —Б–±—А–Њ—Б–Њ–Љ.

always @(posedge clk or negedge clr_n)

begin

if (clr_n == 0) // —В–Њ –ґ–µ —Б–∞–Љ–Њ–µ –Љ–Њ–ґ–љ–Њ –Ј–∞–њ–Є—Б–∞—В—М –Ї–∞–Ї if (!clr_n)

out < = 0;

else

out < = in;

end

end

// –Я–Њ—Б—В–Њ—П–љ–љ–Њ–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–µ.

assign a = !out[0];

endmodule

–Я—А–Є –±—Л—Б—В—А–Њ–Љ –≤–Ј–≥–ї—П–і–µ –љ–∞ –ї–Є—Б—В–Є–љ–≥ Verilog –Љ–Њ–ґ–љ–Њ –Ј–∞–Љ–µ—В–Є—В—М, —З—В–Њ –Њ–љ –њ–Њ—Е–Њ–ґ –љ–∞ —П–Ј—Л–Ї C. –Ґ–Њ—З–Ї–∞ —Б –Ј–∞–њ—П—В–Њ–є –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –≤ –Ї–Њ–љ—Ж–µ –Ї–∞–ґ–і–Њ–≥–Њ –Њ–њ–µ—А–∞—В–Њ—А–∞, –Є –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П —В–Њ—В –ґ–µ —Д–Њ—А–Љ–∞—В –і–ї—П –Њ—Д–Њ—А–Љ–ї–µ–љ–Є—П –Ї–Њ–Љ–Љ–µ–љ—В–∞—А–Є–µ–≤ (/* */ –Є //). –Ю–њ–µ—А–∞—В–Њ—А == —В–∞–Ї–ґ–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –і–ї—П –њ—А–Њ–≤–µ—А–Ї–Є —Н–Ї–≤–Є–≤–∞–ї–µ–љ—В–љ–Њ—Б—В–Є. –Ъ–Њ–љ—Б—В—А—Г–Ї—Ж–Є–Є if..then..else —П–Ј—Л–Ї–∞ Verilog –њ–Њ–і–Њ–±–љ—Л —П–Ј—Л–Ї—Г C, –Ї—А–Њ–Љ–µ –Ї–ї—О—З–µ–≤—Л—Е —Б–ї–Њ–≤ begin –Є end, –Ї–Њ—В–Њ—А—Л–µ –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П –≤–Љ–µ—Б—В–Њ —Д–Є–≥—Г—А–љ—Л—Е —Б–Ї–Њ–±–Њ–Ї. –§–∞–Ї—В–Є—З–µ—Б–Ї–Є –Ї–ї—О—З–µ–≤—Л–µ —Б–ї–Њ–≤–∞ begin –Є end –љ–µ –Њ–±—П–Ј–∞—В–µ–ї—М–љ—Л –і–ї—П –Њ–і–љ–Њ—Б—В—А–Њ—З–љ—Л—Е –±–ї–Њ–Ї–Њ–≤, —В–Њ –ґ–µ —Б–∞–Љ–Њ–µ –њ—А–∞–≤–Є–ї–Њ —А–∞–±–Њ—В–∞–µ—В –і–ї—П –Њ–і–љ–Њ—Б—В—А–Њ—З–љ—Л—Е –±–ї–Њ–Ї–Њ–≤ —П–Ј—Л–Ї–∞ C. –Ш Verilog, –Є C –Њ–±–∞ —З—Г–≤—Б—В–≤–Є—В–µ–ї—М–љ—Л –Ї —А–µ–≥–Є—Б—В—А—Г —В–µ–Ї—Б—В–∞ –Ї–Њ–і–∞.

–Ъ–Њ–љ–µ—З–љ–Њ, –Ї–ї—О—З–µ–≤–Њ–µ –Њ—В–ї–Є—З–Є–µ –Љ–µ–ґ–і—Г –∞–њ–њ–∞—А–∞—В—Г—А–Њ–є –Є –њ—А–Њ–≥—А–∞–Љ–Љ–љ—Л–Љ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ–Љ –≤ —В–Њ–Љ, –Ї–∞–Ї –Њ–љ–Є —А–∞–±–Њ—В–∞—О—В. –†–∞–Ј—А–∞–±–Њ—В–Ї–∞ –љ–∞ –Њ—Б–љ–Њ–≤–µ –ґ–µ–ї–µ–Ј–∞ —Б–Њ—Б—В–Њ–Є—В –Є–Ј –Љ–љ–Њ–ґ–µ—Б—В–≤–∞ —Н–ї–µ–Љ–µ–љ—В–Њ–≤, —А–∞–±–Њ—В–∞—О—Й–Є—Е –њ–∞—А–∞–ї–ї–µ–ї—М–љ–Њ. –Ъ–∞–Ї —В–Њ–ї—М–Ї–Њ —Г—Б—В—А–Њ–є—Б—В–≤–Њ –≤–Ї–ї—О—З–Є–ї–Њ—Б—М, –Ї–∞–ґ–і—Л–є —Н–ї–µ–Љ–µ–љ—В –∞–њ–њ–∞—А–∞—В—Г—А—Л –љ–∞—З–Є–љ–∞–µ—В —А–∞–±–Њ—В—Г –Є –њ–Њ—Б—В–Њ—П–љ–љ–Њ –≤—Л–њ–Њ–ї–љ—П–µ—В —Б–≤–Њ–Є —Д—Г–љ–Ї—Ж–Є–Є. –Ъ–Њ–љ–µ—З–љ–Њ, –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В –ї–Њ–≥–Є–Ї–Є —Г–њ—А–∞–≤–ї–µ–љ–Є—П –Є –і–∞–љ–љ—Л—Е –љ–∞ –≤—Е–Њ–і–µ –љ–µ–Ї–Њ—В–Њ—А—Л–µ —Н–ї–µ–Љ–µ–љ—В—Л —Г—Б—В—А–Њ–є—Б—В–≤–∞ –Љ–Њ–≥—Г—В –љ–µ –Љ–µ–љ—П—В—М –Ј–љ–∞—З–µ–љ–Є—П –љ–∞ —Б–≤–Њ–µ–Љ –≤—Л—Е–Њ–і–µ. –Ю–і–љ–∞–Ї–Њ –Њ–љ–Є –≤—Б–µ —А–∞–≤–љ–Њ –љ–µ–њ—А–µ—А—Л–≤–љ–Њ "—А–∞–±–Њ—В–∞—О—В".

–Т –Њ—В–ї–Є—З–Є–µ –Њ—В —Н—В–Њ–≥–Њ –њ–Њ–≤–µ–і–µ–љ–Є—П –∞–њ–њ–∞—А–∞—В—Г—А—Л —В–Њ–ї—М–Ї–Њ –Љ–∞–ї–∞—П —З–∞—Б—В—М –≤—Б–µ–≥–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–≥–Њ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П –∞–Ї—В–Є–≤–љ–∞ –≤ –Ї–∞–ґ–і—Л–є –њ—А–Њ–Є–Ј–≤–Њ–ї—М–љ—Л–є –Љ–Њ–Љ–µ–љ—В –≤—А–µ–Љ–µ–љ–Є (–і–∞–ґ–µ –µ—Б–ї–Є —Н—В–Њ –Љ–љ–Њ–≥–Њ–Ј–∞–і–∞—З–љ–∞—П —Б—А–µ–і–∞ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–і–∞). –Я—А–Є—З–Є–љ–∞ —Н—В–Њ–≥–Њ –≤ —В–Њ–Љ, —З—В–Њ –њ—А–Њ—Ж–µ—Б—Б–Њ—А, –≤—Л–њ–Њ–ї–љ—П—О—Й–Є–є –Ї–Њ–і, —В–Њ–ї—М–Ї–Њ –Њ–і–Є–љ, –Є –≤ –Ї–∞–ґ–і—Л–є –Љ–Њ–Љ–µ–љ—В –≤—А–µ–Љ–µ–љ–Є –Њ–љ –Љ–Њ–ґ–µ—В –≤—Л–њ–Њ–ї–љ—П—В—М —В–Њ–ї—М–Ї–Њ –Њ–і–љ—Г –Є–љ—Б—В—А—Г–Ї—Ж–Є—О. –Ю—Б—В–∞–ї—М–љ—Г—О —З–∞—Б—В—М –Я–Ю –Љ–Њ–ґ–љ–Њ —Б—З–Є—В–∞—В—М "–±–µ–Ј–і–µ–є—Б—В–≤—Г—О—Й–µ–є", —З—В–Њ –Ї–Њ—А–µ–љ–љ—Л–Љ –Њ–±—А–∞–Ј–Њ–Љ –Њ—В–ї–Є—З–∞–µ—В—Б—П –Њ—В "–Њ—Б—В–∞–ї—М–љ–Њ–є —З–∞—Б—В–Є" –∞–њ–њ–∞—А–∞—В—Г—А—Л. –Я–µ—А–µ–Љ–µ–љ–љ—Л–µ –Љ–Њ–≥—Г—В —Б—Г—Й–µ—Б—В–≤–Њ–≤–∞—В—М –Є —Е—А–∞–љ–Є—В—М —Б–≤–Њ–µ –Ј–љ–∞—З–µ–љ–Є—П, –Њ–і–љ–∞–Ї–Њ –±–Њ–ї—М—И–Є–љ—Б—В–≤–Њ –≤—А–µ–Љ–µ–љ–Є –Њ–љ–Є –љ–µ —Г—З–∞—Б—В–≤—Г—О—В –≤ –Ї–∞–Ї–Њ–є-–ї–Є–±–Њ –Њ–±—А–∞–±–Њ—В–Ї–µ. –≠—Д—Д–µ–Ї—В "–њ–∞—А–∞–ї–ї–µ–ї—М–љ–Њ—Б—В–Є" –≤ —А–∞–±–Њ—В–µ –Я–Ю, –Ї–Њ–≥–і–∞ –њ—А–Њ—Ж–µ—Б—Б–Њ—А —П–Ї–Њ–±—Л –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ –≤—Л–њ–Њ–ї–љ—П–µ—В –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ –Ј–∞–і–∞—З, –Ј–∞–Ї–ї—О—З–∞–µ—В—Б—П –≤ –њ–Њ—Б—В–Њ—П–љ–љ–Њ –њ–Њ–≤—В–Њ—А—П—О—Й–µ–Љ—Б—П, –±—Л—Б—В—А–Њ–Љ –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є —А–∞–Ј–љ—Л—Е —Г—З–∞—Б—В–Ї–Њ–≤ –Ї–Њ–і–∞.

–†–∞–Ј–ї–Є—З–Є—П –≤ –њ–Њ–≤–µ–і–µ–љ–Є–Є –∞–њ–њ–∞—А–∞—В—Г—А—Л –Є –Я–Ю –Њ—В—А–∞–ґ–∞–µ—В—Б—П –≤ –Љ–µ—В–Њ–і–∞—Е, –Ї–Њ—В–Њ—А—Л–Љ–Є –Љ—Л –Ї–Њ–і–Є—А—Г–µ–Љ –њ–Њ–≤–µ–і–µ–љ–Є–µ –∞–њ–њ–∞—А–∞—В—Г—А—Л –Є –њ–Њ–≤–µ–і–µ–љ–Є–µ –њ—А–Њ–≥—А–∞–Љ–Љ—Л. –Я—А–Њ–≥—А–∞–Љ–Љ–љ—Л–є –Ї–Њ–і –≤—Л–њ–Њ–ї–љ—П–µ—В—Б—П –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ, —В–∞–Ї —З—В–Њ –Ї–∞–ґ–і–∞—П —Б—В—А–Њ–Ї–∞ –Ї–Њ–і–∞ –≤—Л–њ–Њ–ї–љ—П–µ—В—Б—П —В–Њ–ї—М–Ї–Њ –њ–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї –±—Л–ї–∞ –≤—Л–њ–Њ–ї–љ–µ–љ–∞ –њ—А–µ–і—Л–і—Г—Й–∞—П —Б—В—А–Њ–Ї–∞ (–Ї–Њ–љ–µ—З–љ–Њ –Є—Б–Ї–ї—О—З–∞—П –љ–µ–ї–Є–љ–µ–є–љ–Њ—Б—В–Є, –≤–љ–Њ—Б–Є–Љ—Л–µ –њ—А–µ—А—Л–≤–∞–љ–Є—П–Љ–Є –Є–ї–Є –њ–ї–∞–љ–Є—А–Њ–≤—Й–Є–Ї–Њ–Љ –Ј–∞–і–∞—З –Њ–њ–µ—А–∞—Ж–Є–Њ–љ–љ–Њ–є —Б–Є—Б—В–µ–Љ—Л).

–Ь–Њ–і—Г–ї—М Verilog –љ–∞—З–Є–љ–∞–µ—В—Б—П —Б –Ї–ї—О—З–µ–≤–Њ–≥–Њ –Љ–Њ–і—Г–ї—П module, –Ј–∞ –Ї–Њ—В–Њ—А—Л–Љ –Є–і–µ—В –Є–Љ—П –Љ–Њ–і—Г–ї—П –Є —Б–њ–Є—Б–Њ–Ї –µ–≥–Њ –њ–Њ—А—В–Њ–≤. –°–њ–Є—Б–Њ–Ї –њ–Њ—А—В–Њ–≤ —Н—В–Њ —Б–њ–Є—Б–Њ–Ї –Є–Љ–µ–љ –≤—Б–µ—Е –≤—Е–Њ–і–Њ–≤ –Є –≤—Л—Е–Њ–і–Њ–≤ –Љ–Њ–і—Г–ї—П. –°–ї–µ–і—Г—О—Й–∞—П —Б–µ–Ї—Ж–Є—П –Ї–Њ–і–∞ —Б–Њ–і–µ—А–ґ–Є—В –і–µ–Ї–ї–∞—А–∞—Ж–Є–Є —Н—В–Є—Е –њ–Њ—А—В–Њ–≤. –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ –≤—Б–µ –≤—Е–Њ–і—Л –Є –≤—Л—Е–Њ–і—Л –њ–Њ—П–≤–ї—П—О—В—Б—П –Ї–∞–Ї –≤ –Ї—А—Г–≥–ї—Л—Е —Б–Ї–Њ–±–Ї–∞—Е –њ–Њ—Б–ї–µ –Є–Љ–µ–љ–Є –Љ–Њ–і—Г–ї—П, —В–∞–Ї –Є –≤ —В–µ–ї–µ –Љ–Њ–і—Г–ї—П, –љ–∞—З–Є–љ–∞—П —Б –µ–≥–Њ –њ–µ—А–≤–Њ–є —Б—В—А–Њ–Ї–Є, –≤ —Б–µ–Ї—Ж–Є–Є –і–µ–Ї–ї–∞—А–∞—Ж–Є–Є –њ–Њ—А—В–Њ–≤.

–Э–∞ —П–Ј—Л–Ї–µ Verilog –≤–љ—Г—В—А–Є –Љ–Њ–і—Г–ї—П —И–Є—А–Њ–Ї–Њ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –і–≤–∞ —В–Є–њ–∞ —Б–Є–≥–љ–∞–ї–Њ–≤: reg (—А–µ–≥–Є—Б—В—А) –Є wire (—Б–Є–≥–љ–∞–ї, –њ—А–Њ–≤–Њ–і). –≠—В–Є —В–Є–њ—Л –Њ—В–ї–Є—З–∞—О—В—Б—П –њ–Њ —Б–≤–Њ–µ–є —Д—Г–љ–Ї—Ж–Є–Є. –Т—Б–µ —З–∞—Б—В–Є –Ї–Њ–і–∞, –Є–Љ–µ—О—Й–Є–µ —Б–Є–≥–љ–∞–ї, –Є–Љ–µ—О—В –љ–µ—П–≤–љ–Њ –і–µ–Ї–ї–∞—А–Є—А–Њ–≤–∞–љ–љ—Л–є wire —Б —В–µ–Љ –ґ–µ –Є–Љ–µ–љ–µ–Љ. –Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, –љ–µ —В—А–µ–±—Г–µ—В—Б—П –і–µ–Ї–ї–∞—А–Є—А–Њ–≤–∞—В—М —В–∞–Ї–Є–µ —Б–Є–≥–љ–∞–ї—Л –Ї–∞–Ї wire. –Ґ–Є–њ reg –±—Г–і–µ—В —Е—А–∞–љ–Є—В—М –≤ —Б–µ–±–µ –њ–Њ—Б–ї–µ–і–љ–µ–µ –љ–∞–Ј–љ–∞—З–µ–љ–љ–Њ–µ –µ–Љ—Г –Ј–љ–∞—З–µ–љ–Є–µ, —В–∞–Ї —З—В–Њ –љ–µ—В –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ—Б—В–Є –≤—Б–µ–≥–і–∞ —Г–њ—А–∞–≤–ї—П—В—М –µ–≥–Њ –Ј–љ–∞—З–µ–љ–Є–µ–Љ. –°–Є–≥–љ–∞–ї—Л —В–Є–њ–∞ wire –Є—Б–њ–Њ–ї—М–Ј—Г—О—В –і–ї—П –∞—Б–Є–љ—Е—А–Њ–љ–љ–Њ–є –ї–Њ–≥–Є–Ї–Є, –Є –Є–љ–Њ–≥–і–∞ –њ–Њ–і–Ї–ї—О—З–∞—О—В—Б—П –Ї –≤–љ–µ—И–љ–Є–Љ —Б–Є–≥–љ–∞–ї–∞–Љ. –Ш–Ј-–Ј–∞ —В–Њ–≥–Њ, —З—В–Њ reg —Е—А–∞–љ–Є—В –њ–Њ—Б–ї–µ–і–љ–µ–µ —Б–≤–Њ–µ –Ј–љ–∞—З–µ–љ–Є–µ, –≤—Е–Њ–і—Л –љ–µ –Љ–Њ–≥—Г—В –і–µ–Ї–ї–∞—А–Є—А–Њ–≤–∞—В—М—Б—П –Ї–∞–Ї reg. –Т—Е–Њ–і –Љ–Њ–ґ–љ–Њ –њ–Њ–Љ–µ–љ—П—В—М –∞—Б–Є–љ—Е—А–Њ–љ–љ–Њ –≤ –Љ–Њ–Љ–µ–љ—В –ї—О–±–Њ–≥–Њ —Б–Њ–±—Л—В–Є—П –Љ–Њ–і—Г–ї—П Verilog. –Ю–і–љ–∞–Ї–Њ –Њ—Б–љ–Њ–≤–љ–Њ–µ –Њ—В–ї–Є—З–Є–µ wire –Њ—В reg –≤ —В–Њ–Љ, —З—В–Њ —Б–Є–≥–љ–∞–ї—Л —В–Є–њ–∞ reg –Љ–Њ–≥—Г—В –љ–∞–Ј–љ–∞—З–∞—В—М—Б—П —В–Њ–ї—М–Ї–Њ –≤ –њ—А–Њ—Ж–µ–і—Г—А–љ—Л—Е –±–ї–Њ–Ї–∞—Е (—З—В–Њ —Н—В–Њ —В–∞–Ї–Њ–µ, –Њ–±—Б—Г–і–Є–Љ –њ–Њ–Ј–ґ–µ) –≤ —В–Њ –≤—А–µ–Љ—П –Ї–∞–Ї —Б–Є–≥–љ–∞–ї—Л —В–Є–њ–∞ wire –Љ–Њ–≥—Г—В –±—Л—В—М –љ–∞–Ј–љ–∞—З–µ–љ—Л –Ј–љ–∞—З–µ–љ–Є—О —В–Њ–ї—М–Ї–Њ –≤–љ–µ –њ—А–Њ—Ж–µ–і—Г—А–љ—Л—Е –±–ї–Њ–Ї–Њ–≤. –Ю–±–∞ —Н—В–Є—Е —В–Є–њ–∞ —Б–Є–≥–љ–∞–ї–Њ–≤ –Љ–Њ–≥—Г—В –њ–Њ—П–≤–ї—П—В—М—Б—П –Ї–∞–Ї —Б–ї–µ–≤–∞, —В–∞–Ї –Є —Б–њ—А–∞–≤–∞ –≤ –≤—Л—А–∞–ґ–µ–љ–Є–Є –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П, –Є –Ї–∞–Ї –≤–љ—Г—В—А–Є, —В–∞–Ї –Є —Б–љ–∞—А—Г–ґ–Є –њ—А–Њ—Ж–µ–і—Г—А–љ—Л—Е –±–ї–Њ–Ї–Њ–≤.

–Т–∞–ґ–љ–Њ –њ–Њ–љ–Є–Љ–∞—В—М, —З—В–Њ –Ї–ї—О—З–µ–≤–Њ–µ —Б–ї–Њ–≤–Њ reg –љ–µ–Њ–±—П–Ј–∞—В–µ–ї—М–љ–Њ –Ј–∞—Б—В–∞–≤–Є—В –Ї–Њ–Љ–њ–Є–ї—П—В–Њ—А –Ј–∞—А–µ–Ј–µ—А–≤–Є—А–Њ–≤–∞—В—М –≤ —Н—В–Њ–Љ –Љ–µ—Б—В–µ —П—З–µ–є–Ї—Г –њ–∞–Љ—П—В–Є (—Б–Њ–Ј–і–∞—В—М –і–ї—П —Н—В–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ —В—А–Є–≥–≥–µ—А –Є–ї–Є —А–µ–≥–Є—Б—В—А). –Ъ–Њ–і –≤ –Ы–Є—Б—В–Є–љ–≥–µ 2 –Є–Љ–µ–µ—В –Њ–і–Є–љ –≤–љ—Г—В—А–µ–љ–љ–Є–є —Б–Є–≥–љ–∞–ї —В–Є–њ–∞ reg, –Ї–Њ—В–Њ—А—Л–є –Є–Љ–µ–µ—В —А–∞–Ј—А—П–і–љ–Њ—Б—В—М 8 –±–Є—В –Є –љ–∞–Ј—Л–≤–∞–µ—В—Б—П out. –≠—В–Њ—В –Љ–Њ–і—Г–ї—М –≤—Л–≤–Њ–і–Є—В reg –њ–Њ—В–Њ–Љ—Г, —З—В–Њ —В–∞–Ї–Є–Љ —Б–њ–Њ—Б–Њ–±–Њ–Љ –њ–Є—И–µ—В—Б—П –±–ї–Њ–Ї always (—Н—В–Њ –Њ–і–Є–љ –Є–Ј —В–Є–њ–Њ–≤ –њ—А–Њ—Ж–µ–і—Г—А–љ—Л—Е –±–ї–Њ–Ї–Њ–≤). –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ —Б–Є–≥–љ–∞–ї a —Н—В–Њ wire, —В–∞–Ї —З—В–Њ –µ–Љ—Г –Љ–Њ–ґ–љ–Њ –њ—А–Є—Б–≤–Њ–Є—В—М –Ј–љ–∞—З–µ–љ–Є–µ —В–Њ–ї—М–Ї–Њ –Њ–њ–µ—А–∞—В–Њ—А–Њ–Љ –њ–Њ—Б—В–Њ—П–љ–љ–Њ–≥–Њ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П, –≤ —В–Њ –≤—А–µ–Љ—П –Ї–∞–Ї –Ј–љ–∞—З–µ–љ–Є–µ –і–ї—П —В–Є–њ–∞ reg –љ–∞–Ј–љ–∞—З–∞–µ—В—Б—П –≤–µ–ї–Є—З–Є–љ–∞ —В–Њ–ї—М–Ї–Њ –≤ –±–ї–Њ–Ї–µ always.

–С–ї–Њ–Ї always —Н—В–Њ –±–ї–Њ–Ї –њ—А–Њ—Ж–µ–і—Г—А–љ–Њ–≥–Њ —В–Є–њ–∞, –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л–є –і–ї—П –Њ–±–љ–Њ–≤–ї–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤ —В–Њ–ї—М–Ї–Њ –њ—А–Є –≤–Њ–Ј–љ–Є–Ї–љ–Њ–≤–µ–љ–Є–Є –Ї–∞–Ї–Є—Е-–ї–Є–±–Њ —Б–Њ–±—Л—В–Є–є (–Ї–Њ–≥–і–∞ –Ї–∞–Ї–Њ–є-—В–Њ —Б–Є–≥–љ–∞–ї –њ–Њ–Љ–µ–љ—П–µ—В —Б–≤–Њ–µ –Ј–љ–∞—З–µ–љ–Є–µ). –У—А—Г–њ–њ–∞ –≤—Л—А–∞–ґ–µ–љ–Є–є –≤–љ—Г—В—А–Є –Ї—А—Г–≥–ї—Л—Е —Б–Ї–Њ–±–Њ–Ї –Њ–њ–µ—А–∞—В–Њ—А–∞ always –љ–∞–Ј—Л–≤–∞–µ—В—Б—П —Б–њ–Є—Б–Ї–Њ–Љ —З—Г–≤—Б—В–≤–Є—В–µ–ї—М–љ–Њ—Б—В–Є (sensitivity list). –Ю–љ –Њ–њ—А–µ–і–µ–ї—П–µ—В, –љ–∞ –Ї–∞–Ї–Є–µ —Б–Є–≥–љ–∞–ї—Л —Б—А–∞–±–∞—В—Л–≤–∞–µ—В –±–ї–Њ–Ї always, –Є –Њ–љ –Є–Љ–µ–µ—В —Д–Њ—А–Љ—Г:

(–≤—Л—А–∞–ґ–µ–љ–Є–µ1 or –≤—Л—А–∞–ґ–µ–љ–Є–µ2 ...)

–Ъ–Њ–і –≤–љ—Г—В—А–Є —В–∞–Ї–Њ–≥–Њ –±–ї–Њ–Ї–∞ always –≤—Л–њ–Њ–ї–љ—П–µ—В—Б—П –≤—Б—П–Ї–Є–є —А–∞–Ј, –Ї–Њ–≥–і–∞ –ї—О–±–Њ–µ –Є–Ј –≤—Л—А–∞–ґ–µ–љ–Є–є –≤ —Б–њ–Є—Б–Ї–µ —З—Г–≤—Б—В–≤–Є—В–µ–ї—М–љ–Њ—Б—В–Є –њ—А–Є–Љ–µ—В –Ј–љ–∞—З–µ–љ–Є–µ true (–≤–Љ–µ—Б—В–Њ or –Љ–Њ–ґ–µ—В –±—Л—В—М –Њ–њ–µ—А–∞—Ж–Є—П and, —В–Њ–≥–і–∞ –≤—Б–µ –≤—Л—А–∞–ґ–µ–љ–Є—П –і–Њ–ї–ґ–љ—Л –±—Л—В—М true). –Ъ–ї—О—З–µ–≤—Л–µ —Б–ї–Њ–≤–∞ Verilog –і–ї—П –Њ–±–Њ–Ј–љ–∞—З–µ–љ–Є—П —Б–Њ–±—Л—В–Є—П –љ–∞—А–∞—Б—В–∞–љ–Є—П —Б–Є–≥–љ–∞–ї–∞ (–Њ—В –ї–Њ–≥. 0 –Ї –ї–Њ–≥. 1) –Є –і–ї—П —Б–Њ–±—Л—В–Є—П —Б–њ–∞–і–∞ —Б–Є–≥–љ–∞–ї–∞ (–Њ—В –ї–Њ–≥. 1 –Ї –ї–Њ–≥. 0) —Н—В–Њ posedge –Є negedge —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–µ–љ–љ–Њ. –Ю–љ–Є —З–∞—Б—В–Њ –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П –≤ —Б–њ–Є—Б–Ї–∞—Е —З—Г–≤—Б—В–≤–Є—В–µ–ї—М–љ–Њ—Б—В–Є. –Т –њ–Њ–Ї–∞–Ј–∞–љ–љ–Њ–Љ –њ—А–Є–Љ–µ—А–µ –±–ї–Њ–Ї always —Б—А–∞–±–Њ—В–∞–µ—В (–≤—Л–њ–Њ–ї–љ—П—В—Б—П –Њ–њ–µ—А–∞—В–Њ—А—Л –≤ –µ–≥–Њ –±–ї–Њ–Ї–µ), –µ—Б–ї–Є –њ—А–Њ–Є–Ј–Њ–є–і–µ—В –њ–Њ–ї–Њ–ґ–Є—В–µ–ї—М–љ—Л–є –њ–µ—А–µ–њ–∞–і —Б–Є–≥–љ–∞–ї–∞ clk –Є–ї–Є –Њ—В—А–Є—Ж–∞—В–µ–ї—М–љ—Л–є –њ–µ—А–µ–њ–∞–і —Б–Є–≥–љ–∞–ї–∞ clr_n.

–І—В–Њ–±—Л –≤—Л–≤–µ—Б—В–Є —А–µ–≥–Є—Б—В—А, –≤—Л—Е–Њ–і –і–Њ–ї–ґ–µ–љ –±—Л—В—М –Њ–±–љ–Њ–≤–ї–µ–љ –њ–Њ —Д—А–Њ–љ—В—Г –љ–∞—А–∞—Б—В–∞–љ–Є—П —В–∞–Ї—В–Њ–≤ (—Б—А–µ–Ј —Б–њ–∞–і–∞ —В–∞–Ї–ґ–µ –±—Г–і–µ—В —А–∞–±–Њ—В–∞—В—М, –љ–Њ —З–∞—Й–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –Є–Љ–µ–љ–љ–Њ —Д—А–Њ–љ—В). –Ф–Њ–±–∞–≤–ї–µ–љ–Є–µ negedge clr_n –Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ—В —Б–±—А–Њ—Б —А–µ–≥–Є—Б—В—А–∞ –њ—А–Є —Б–њ–∞–і–µ —Г—А–Њ–≤–љ—П —Б–Є–≥–љ–∞–ї–∞ clr_n. –Э–µ –≤—Б–µ —Б–њ–Є—Б–Ї–Є —З—Г–≤—Б—В–≤–Є—В–µ–ї—М–љ–Њ—Б—В–Є –±—Г–і—Г—В —Б–Њ–і–µ—А–ґ–∞—В—М –≤ —Б–µ–±–µ –Ї–ї—О—З–µ–≤—Л–µ —Б–ї–Њ–≤–∞ posedge –Є–ї–Є negedge, —В–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ –љ–µ –≤—Б–µ–≥–і–∞ –≤ –њ–Њ–ї—Г—З–µ–љ–љ–Њ–є –∞–њ–њ–∞—А–∞—В—Г—А–µ –±—Г–і–µ—В —Б–Є–љ—В–µ–Ј–Є—А–Њ–≤–∞–љ –љ–∞—Б—В–Њ—П—Й–Є–є —А–µ–≥–Є—Б—В—А.

–Т–љ—Г—В—А–Є –±–ї–Њ–Ї–∞ always –њ–µ—А–≤—Л–є –Њ–њ–µ—А–∞—В–Њ—А –Њ–њ—А–∞—И–Є–≤–∞–µ—В, –њ—А–Њ–Є–Ј–Њ—И–µ–ї –ї–Є —Б–њ–∞–і —Б–Є–≥–љ–∞–ї–∞ clr_n. –Х—Б–ї–Є —Н—В–Њ —В–∞–Ї, —В–Њ —Б–ї–µ–і—Г—О—Й–∞—П —Б—В—А–Њ–Ї–∞ –Ї–Њ–і–∞ —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В out –≤ 0. –≠—В–Є —Б—В—А–Њ–Ї–Є –Ї–Њ–і–∞ —А–µ–∞–ї–Є–Ј—Г—О—В –∞—Б–Є–љ—Е—А–Њ–љ–љ—Л–є —Б–±—А–Њ—Б —А–µ–≥–Є—Б—В—А–∞ –њ–Њ —Б–њ–∞–і—Г —Б–Є–≥–љ–∞–ї–∞ clr_n. –Ю–њ–µ—А–∞—В–Њ—А —Г—Б–ї–Њ–≤–Є—П, –≥–і–µ:

if (negedge clr_n and clk == 1)

... –≤—Л–њ–Њ–ї–љ–Є—В —Г–ґ–µ —Б–Є–љ—Е—А–Њ–љ–љ—Л–є —Б–±—А–Њ—Б, –Ї–Њ—В–Њ—А—Л–є –Ј–∞–≤–Є—Б–Є—В —В–∞–Ї–ґ–µ –Є –Њ—В —Г—А–Њ–≤–љ—П —В–∞–Ї—В–Њ–≤.

–Т—Л –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ –Ј–∞–Љ–µ—В–Є–ї–Є, —З—В–Њ –Њ–њ–µ—А–∞—В–Њ—А –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П –≤–љ—Г—В—А–Є –±–ї–Њ–Ї–∞ always –Є –≤–љ–µ –±–ї–Њ–Ї–∞ always –Њ—Д–Њ—А–Љ–ї—П–µ—В—Б—П –њ–Њ-—А–∞–Ј–љ–Њ–Љ—Г. –Я–Њ—Б—В–Њ—П–љ–љ–Њ–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–µ (–≤–љ–µ –њ—А–Њ—Ж–µ–і—Г—А–љ–Њ–≥–Њ –±–ї–Њ–Ї–∞) –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В –Ї–ї—О—З–µ–≤–Њ–µ —Б–ї–Њ–≤–Њ assign, –∞ –≤–љ—Г—В—А–Є –њ—А–Њ—Ж–µ–і—Г—А–љ–Њ–≥–Њ –±–ї–Њ–Ї–∞ –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П –Њ–њ–µ—А–∞—В–Њ—А < = –і–ї—П –љ–µ –±–ї–Њ–Ї–Є—А—Г—О—Й–µ–≥–Њ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П –Є –Њ–њ–µ—А–∞—В–Њ—А = –і–ї—П –±–ї–Њ–Ї–Є—А—Г—О—Й–µ–≥–Њ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П.

–Т –≥—А—Г–њ–њ–µ –±–ї–Њ–Ї–Є—А—Г—О—Й–Є—Е –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–є —Б–љ–∞—З–∞–ї–∞ –Њ–±—А–∞–±–∞—В—Л–≤–∞–µ—В—Б—П –њ–µ—А–≤–Њ–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–µ, –Є —В–Њ–ї—М–Ї–Њ –њ–Њ –µ–≥–Њ –Ј–∞–≤–µ—А—И–µ–љ–Є–Є –≤—Л–њ–Њ–ї–љ—П–µ—В—Б—П —Б–ї–µ–і—Г—О—Й–µ–µ –±–ї–Њ–Ї–Є—А—Г—О—Й–µ–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–µ. –≠—В–Њ—В –њ—А–Њ—Ж–µ—Б—Б —А–∞–±–Њ—В–∞–µ—В –Ї–∞–Ї –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є–µ –Њ–њ–µ—А–∞—В–Њ—А–Њ–≤ –љ–∞ —П–Ј—Л–Ї–µ C. –° –љ–µ–±–ї–Њ–Ї–Є—А—Г—О—Й–Є–Љ–Є –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П–Љ–Є –њ—А–∞–≤–∞—П —Б—В–Њ—А–Њ–љ–∞ –≤—Б–µ—Е –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–є –≤—Л—З–Є—Б–ї—П–µ—В—Б—П –Є –њ—А–Є—Б–≤–∞–Є–≤–∞–µ—В—Б—П –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ. –Я–Њ—Б—В–Њ—П–љ–љ–Њ–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–µ –і–Њ–ї–ґ–љ–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –±–ї–Њ–Ї–Є—А—Г—О—Й–µ–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–µ (–Є–љ–∞—З–µ –Ї–Њ–Љ–њ–Є–ї—П—В–Њ—А –≤—Л–і–∞—Б—В –Њ—И–Є–±–Ї—Г).

–І—В–Њ–±—Л —Б–і–µ–ї–∞—В—М –Ї–Њ–і –Љ–µ–љ–µ–µ –њ–Њ–і–≤–µ—А–ґ–µ–љ–љ—Л–Љ –Њ—И–Є–±–Ї–∞–Љ, —А–µ–Ї–Њ–Љ–µ–љ–і—Г–µ—В—Б—П –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –љ–µ –±–ї–Њ–Ї–Є—А—Г—О—Й–Є–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П –і–ї—П –≤—Б–µ—Е –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є–є –≤ –±–ї–Њ–Ї–µ always —Б –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ–є –ї–Њ–≥–Є–Ї–Њ–є (–љ–∞–њ—А–Є–Љ–µ—А –і–ї—П –ї–Њ–≥–Є–Ї–Є, –Ї–Њ—В–Њ—А—Г—О –Т—Л —Е–Њ—В–Є—В–µ —А–µ–∞–ї–Є–Ј–Њ–≤–∞—В—М –Ї–∞–Ї —А–µ–≥–Є—Б—В—А—Л). –С–Њ–ї—М—И–Є–љ—Б—В–≤–Њ –±–ї–Њ–Ї–Њ–≤ always –і–Њ–ї–ґ–љ–Њ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –љ–µ –±–ї–Њ–Ї–Є—А—Г—О—Й–Є–µ –Њ–њ–µ—А–∞—В–Њ—А—Л –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П. –Х—Б–ї–Є –±–ї–Њ–Ї always –Є–Љ–µ–µ—В –њ–Њ–ї–љ–Њ—Б—В—М—О –Ї–Њ–Љ–±–Є–љ–∞—В–Њ—А–љ—Г—О –ї–Њ–≥–Є–Ї—Г, —В–Њ–≥–і–∞ –Т—Л –Ј–∞—Е–Њ—В–Є—В–µ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –±–ї–Њ–Ї–Є—А—Г—О—Й–Є–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П.

[–Р–њ–њ–∞—А–∞—В–љ—Л–є –®–Ш–Ь]

–І–∞—Б—В–Њ –њ–µ—А–≤–∞—П –Ј–∞–і–∞—З–∞, –Ї–Њ—В–Њ—А—Г—О –љ–∞–і–Њ —А–µ—И–Є—В—М –њ—А–Є —Б–Њ–Ј–і–∞–љ–Є–Є –∞–њ–њ–∞—А–∞—В–љ–Њ–≥–Њ –Љ–Њ–і—Г–ї—П —Б –њ—А–Є–≤—П–Ј–Ї–Њ–є –Ї –Ї–∞—А—В–µ –њ–∞–Љ—П—В–Є, —Н—В–Њ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ—Б—В—М —Б–њ—А–Њ–µ–Ї—В–Є—А–Њ–≤–∞—В—М –Ї–∞—А—В—Г —А–µ–≥–Є—Б—В—А–Њ–≤, –Ї –Ї–Њ—В–Њ—А—Л–Љ –±—Г–і–µ—В –Њ–±—А–∞—Й–∞—В—М—Б—П –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–µ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ –њ—А–Є —Г–њ—А–∞–≤–ї–µ–љ–Є–Є –∞–њ–њ–∞—А–∞—В—Г—А–Њ–є. –Т —Б–ї—Г—З–∞–µ –®–Ш–Ь –љ—Г–ґ–љ–Њ –Є–Љ–µ—В—М –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ —Г—Б—В–∞–љ–Њ–≤–Є—В—М –њ–µ—А–Є–Њ–і –Є —И–Є—А–Є–љ—Г –Є–Љ–њ—Г–ї—М—Б–∞ –®–Ш–Ь. –Т –∞–њ–њ–∞—А–∞—В—Г—А–µ –љ—Г–ґ–љ–Њ —А–µ–∞–ї–Є–Ј–Њ–≤–∞—В—М —Б—З–µ—В—З–Є–Ї, –Ї–Њ—В–Њ—А—Л–є –±—Г–і–µ—В –њ—А–Њ—Б—В–Њ —Б—З–Є—В–∞—В—М —В–∞–Ї—В—Л —Б–Є—Б—В–µ–Љ–љ–Њ–є —З–∞—Б—В–Њ—В—Л. –Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, —Н—В–Њ –±—Г–і—Г—В 2 —А–µ–≥–Є—Б—В—А–∞ pulse_width –Є period, –≤ –Њ–±–Њ–Є—Е –±—Г–і—Г—В –Ј–∞–њ–Є—Б—Л–≤–∞—В—М—Б—П –µ–і–Є–љ–Є—Ж—Л –Є–Ј–Љ–µ—А–µ–љ–Є—П –≤—А–µ–Љ–µ–љ–Є –≤ —В–∞–Ї—В–∞—Е —Б–Є—Б—В–µ–Љ—Л. –Ґ–∞–±–ї–Є—Ж–∞ 1 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –Ї–∞—А—В—Г –њ–∞–Љ—П—В–Є –і–ї—П —А–µ–≥–Є—Б—В—А–Њ–≤ –Љ–Њ–і—Г–ї—П –®–Ш–Ь.

–Ґ–∞–±–ї–Є—Ж–∞ 1. Register map –і–ї—П –±–ї–Њ–Ї–∞ PWM.

| –Р–і—А–µ—Б |

–Ш–Љ—П |

–†–∞–Ј—А—П–і–љ–Њ—Б—В—М |

–Ю–њ–Є—Б–∞–љ–Є–µ |

| 0 |

period |

32 –±–Є—В–∞ |

–Ъ–Њ–ї–Є—З–µ—Б—В–≤–Њ —В–∞–Ї—В–Њ–≤ –Ј–∞ –њ–µ—А–Є–Њ–і —Б–Є–≥–љ–∞–ї–∞ –®–Ш–Ь |

| 1 |

pulse_width |

32 –±–Є—В–∞ |

–Ъ–Њ–ї–Є—З–µ—Б—В–≤–Њ —В–∞–Ї—В–Њ–≤ –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В–Є –ї–Њ–≥. 1 —Б–Є–≥–љ–∞–ї–∞ –®–Ш–Ь |

–І—В–Њ–±—Л –Њ–њ—А–µ–і–µ–ї–Є—В—М —Г—А–Њ–≤–µ–љ—М –≤—Л—Е–Њ–і–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –®–Ш–Ь, –∞–њ–њ–∞—А–∞—В—Г—А–∞ –Љ–Њ–ґ–µ—В –њ—А–Њ—Б—В–Њ —Б—А–∞–≤–љ–Є—В—М —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ —А–µ–≥–Є—Б—В—А–Њ–≤ period –Є pulse_width —Б –њ–Њ—Б—В–Њ—П–љ–љ–Њ —А–∞–±–Њ—В–∞—О—Й–Є–Љ —Б—З–µ—В—З–Є–Ї–Њ–Љ.

–Ч–∞—В–µ–Љ –≤—Л–±–µ—А–Є—В–µ –њ–Њ—А—В—Л –і–ї—П PWM, —З—В–Њ –≤ –±–Њ–ї—М—И–Є–љ—Б—В–≤–µ —Б–ї—Г—З–∞–µ–≤ –і–µ–ї–∞–µ—В—Б—П –љ–∞ –Њ—Б–љ–Њ–≤–µ —И–Є–љ–љ–Њ–є –∞—А—Е–Є—В–µ–Ї—В—Г—А—Л. –Ґ–∞–±–ї–Є—Ж–∞ 2 –і–∞–µ—В –Ї—А–∞—В–Ї–Њ–µ –Њ–њ–Є—Б–∞–љ–Є–µ —Б–Є–≥–љ–∞–ї–Њ–≤ –і–ї—П –њ—А–Њ—Б—В–Њ–є –Њ—В–Њ–±—А–∞–ґ–µ–љ–љ–Њ–є –љ–∞ –њ–∞–Љ—П—В—М —Б—Е–µ–Љ—Л PWM. –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –њ–Њ–њ—Г–ї—П—А–љ–Њ–µ —Б–Њ–≥–ї–∞—И–µ–љ–Є–µ –Њ–± –Є–Љ–µ–љ–Њ–≤–∞–љ–Є–Є, –Ї–Њ–≥–і–∞ –Є–Љ–µ–љ–∞ —Б–Є–≥–љ–∞–ї–Њ–≤ —Б –∞–Ї—В–Є–≤–љ—Л–Љ –љ—Г–ї–µ–≤—Л–Љ —Г—А–Њ–≤–љ–µ–Љ –њ–Њ–ї—Г—З–∞—О—В —Б—Г—Д—Д–Є–Ї—Б "_n", —З—В–Њ —З–∞—Б—В–Њ –њ—А–Є–Љ–µ–љ—П–µ—В—Б—П –і–ї—П —Б–Є–≥–љ–∞–ї–Њ–≤ —Г–њ—А–∞–≤–ї–µ–љ–Є—П (—В–∞–Ї–Є—Е –Ї–∞–Ї —Б–±—А–Њ—Б –Є–ї–Є —Б–Є–≥–љ–∞–ї –≤—Л–±–Њ—А–Ї–Є). –°–Є–≥–љ–∞–ї—Л write_n –Є clr_n –Є–Ј —В–∞–±–ї–Є—Ж—Л 2 –Є–Љ–µ—О—В —Г—А–Њ–≤–µ–љ—М –∞–Ї—В–Є–≤–љ–Њ–≥–Њ –ї–Њ–≥. 0 (—В. –µ. –Њ–љ–Є —Б—А–∞–±–∞—В—Л–≤–∞—О—В –њ–Њ —Б–њ–∞–і—Г —Г—А–Њ–≤–љ—П).

–Ґ–∞–±–ї–Є—Ж–∞ 2. –Я–Њ—А—В—Л –і–ї—П –±–ї–Њ–Ї–∞ PWM.

| –Ш–Љ—П —Б–Є–≥–љ–∞–ї–∞ |

–Э–∞–њ—А–∞–≤–ї–µ–љ–Є–µ |

–Ю–њ–Є—Б–∞–љ–Є–µ |

| clk |

–Т—Е–Њ–і |

–°–Є—Б—В–µ–Љ–љ—Л–µ —В–∞–Ї—В—Л |

| write_data[31:0] |

–Т—Е–Њ–і |

–®–Є–љ–∞ –і–∞–љ–љ—Л—Е –і–ї—П –Ј–∞–њ–Є—Б–Є (–≤ —А–µ–≥–Є—Б—В—А—Л –љ–∞ –Ї–∞—А—В–µ –њ–∞–Љ—П—В–Є) |

| cs |

–Т—Е–Њ–і |

Chip Select (–≤—Л–±–Њ—А–Ї–∞, —Б–Є–≥–љ–∞–ї —А–∞–Ј—А–µ—И–µ–љ–Є—П —А–∞–±–Њ—В—Л —И–Є–љ—Л) |

| write_n |

–Т—Е–Њ–і |

–†–∞–Ј—А–µ—И–µ–љ–Є–µ –Ј–∞–њ–Є—Б–Є, –∞–Ї—В–Є–≤–љ—Л–є —Г—А–Њ–≤–µ–љ—М –ї–Њ–≥. 0 |

| addr |

–Т—Е–Њ–і |

–Р–і—А–µ—Б (–і–ї—П –≤—Л–±–Њ—А–∞ –љ—Г–ґ–љ–Њ–≥–Њ —А–µ–≥–Є—Б—В—А–∞ –љ–∞ –Ї–∞—А—В–µ –њ–∞–Љ—П—В–Є) |

| clr_n |

–Т—Е–Њ–і |

–°–±—А–Њ—Б, –∞–Ї—В–Є–≤–љ—Л–є —Г—А–Њ–≤–µ–љ—М –ї–Њ–≥. 0 |

| read_data[31:0] |

–Т—Л—Е–Њ–і |

–І–Є—В–∞–µ–Љ—Л–µ –і–∞–љ–љ—Л–µ |

| pwm_out |

–Т—Л—Е–Њ–і |

–У–µ–љ–µ—А–Є—А—Г–µ–Љ—Л–є —Б–Є–≥–љ–∞–ї –®–Ш–Ь |

–Ґ–µ–њ–µ—А—М, –Ї–Њ–≥–і–∞ –Љ—Л –њ–Њ–ї–љ–Њ—Б—В—М—О –Њ–њ—А–µ–і–µ–ї–Є–ї–Є –≤–љ–µ—И–љ–Є–є –Є–љ—В–µ—А—Д–µ–є—Б –і–ї—П –Љ–Њ–і—Г–ї—П –∞–њ–њ–∞—А–∞—В—Г—А—Л PWM, –Љ–Њ–ґ–љ–Њ –љ–∞—З–∞—В—М –њ–Є—Б–∞—В—М –Ї–Њ–і Verilog. –Я—А–Є–Љ–µ—А —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є –∞–њ–њ–∞—А–∞—В–љ–Њ–≥–Њ –Љ–Њ–і—Г–ї—П –®–Ш–Ь –њ–Њ–Ї–∞–Ј–∞–љ –≤ –Ы–Є—Б—В–Є–љ–≥–µ 3.

–Ы–Є—Б—В–Є–љ–≥ 3. –Р–њ–њ–∞—А–∞—В–љ–∞—П —А–µ–∞–ї–Є–Ј–∞—Ж–Є—П PWM –љ–∞ Verilog.

module pwm (clk, write_data, cs, write_n, read_data, pwm_out);

// –Ф–µ–Ї–ї–∞—А–∞—Ж–Є–Є –њ–Њ—А—В–Њ–≤:

input clk;

input [31:0] write_data

input cs;

input write_n;

input addr,

input clr_n;

output [31:0] read_data;

output pwm_out;

// –Ф–µ–Ї–ї–∞—А–∞—Ж–Є–Є —Б–Є–≥–љ–∞–ї–Њ–≤:

reg [31:0] period;

reg [31:0] pulse_width

reg [31:0] counter;

reg off;

reg [31:0] read_data;

wire period_en, pulse_width_en; // write enables

// –Ю–њ—А–µ–і–µ–ї–µ–љ–Є–µ —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–≥–Њ —А–µ–≥–Є—Б—В—А–Њ–≤ period –Є pulse_width,

// –≤–Ї–ї—О—З–∞—П –і–Њ—Б—В—Г–њ –љ–∞ –Ј–∞–њ–Є—Б—М –≤ —Н—В–Є —А–µ–≥–Є—Б—В—А—Л:

always @(posedge clk or negedge clr_n)

begin

if (clr_n=0)

begin

period < = 32h000000000;

pulse_width < = 32h00000000;

end

else

begin

if(period_en)

period < = write_data [31:0];

else

period < = period;

if (pulse_width_en)

pulse_width < = write_data[31;0];

else

pulse_width < = pulse_width;

end

end

// –Ф–Њ—Б—В—Г–њ –љ–∞ —З—В–µ–љ–Є–µ –і–ї—П —А–µ–≥–Є—Б—В—А–Њ–≤ period –Є pulse_width:

always @(addr or period or pulse_width)

if (addr == 0)

read_data = period;

else

read_data = pulse_width;

// –°—З–µ—В—З–Є–Ї, –Ї–Њ—В–Њ—А—Л–є –њ–Њ—Б—В–Њ—П–љ–љ–Њ —Б—З–Є—В–∞–µ—В –≤ —В–µ—З–µ–љ–Є–µ –њ–µ—А–Є–Њ–і–∞ –®–Ш–Ь:

always @(posedge clk or negedge clr_n)

begin

if (clr_n == 0)

counter < = 0;

else

if (counter >= period - 1) // —Б—З–µ—В –Њ—В 0 –і–Њ (period-1)

counter < = 0;

else

counter < = counter += 1;

end

// –Т–Ї–ї—О—З–µ–љ–Є–µ –≤—Л—Е–Њ–і–∞, –Ї–Њ–≥–і–∞ —Б—З–µ—В—З–Є–Ї –Љ–µ–љ—М—И–µ, —З–µ–Љ pulse_width; –Є–љ–∞—З–µ

// –≤—Л–Ї–ї—О—З–µ–љ–Є–µ –≤—Л—Е–Њ–і–∞. !off –њ–Њ–і–Ї–ї—О—З–µ–љ –Ї –≤—Л—Е–Њ–і—Г –®–Ш–Ь.

always @(posedge clk or negedge clr_n)

begin

if (clr_n == 0)

off < = 0;

else

if (counter >= pulse_width)

off < = 1;

else

if (counter == 0)

off < = 0;

else

off < = off;

end

// –°–Є–≥–љ–∞–ї—Л —А–∞–Ј—А–µ—И–µ–љ–Є—П –Ј–∞–њ–Є—Б–Є –і–ї—П –Ј–∞–њ–Є—Б–Є –≤ —А–µ–≥–Є—Б—В—А—Л period –Є pulse_width:

assign period_en = cs & !write_n & !addr;

assign pulse_width_en = cs & !write_n & addr;

// –Т—Л–≤–Њ–і —Б–Є–≥–љ–∞–ї–∞ –®–Ш–Ь:

assign pwm_out = !off;

endmodule

–Я–µ—А–≤—Л–µ —Б–Є–≥–љ–∞–ї—Л —Н—В–Њ –і–µ–Ї–ї–∞—А–∞—Ж–Є–Є –њ–Њ—А—В–Њ–≤, –Њ–њ–Є—Б–∞–љ–љ—Л–µ –≤ —В–∞–±–ї–Є—Ж–µ 2. –Я–Њ—Б–ї–µ –і–µ–Ї–ї–∞—А–∞—Ж–Є–Є –њ–Њ—А—В–Њ–≤ –Є–і—Г—В –і–µ–Ї–ї–∞—А–∞—Ж–Є–Є –≤–љ—Г—В—А–µ–љ–љ–Є—Е —Б–Є–≥–љ–∞–ї–Њ–≤. –†–µ–≥–Є—Б—В—А—Л, –Њ—В–Њ–±—А–∞–ґ–µ–љ–љ—Л–µ –љ–∞ –њ–∞–Љ—П—В—М (memory-mapped), —Б–Њ—Б—В–∞–≤–ї—П—О—В –Є–љ—В–µ—А—Д–µ–є—Б –і–ї—П –і–Њ—Б—В—Г–њ–∞ —Б–Њ —Б—В–Њ—А–Њ–љ—Л –≤–љ–µ—И–љ–µ–≥–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–≥–Њ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П (–Ї–Њ—В–Њ—А–Њ–µ –Њ–±—Л—З–љ–Њ —А–∞–±–Њ—В–∞–µ—В –љ–∞ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–µ). –Ю–љ–Є —Б–ї—Г–ґ–∞—В –і–ї—П –Є–Ј–Љ–µ–љ–µ–љ–Є—П –њ–∞—А–∞–Љ–µ—В—А–Њ–≤ –®–Ш–Ь, –Є –і–µ–Ї–ї–∞—А–Є—А–Њ–≤–∞–љ—Л –Ї–∞–Ї reg. –Ъ–Њ–і —А–∞–Ј—А–µ—И–∞–µ—В —В–Њ–ї—М–Ї–Њ 32-–±–Є—В–љ—Л–є –і–Њ—Б—В—Г–њ –Ї —Н—В–Є–Љ memory-mapped —А–µ–≥–Є—Б—В—А–∞–Љ. –Х—Б–ї–Є –Т–∞–Љ –љ—Г–ґ–љ–Њ —А–µ–∞–ї–Є–Ј–Њ–≤–∞—В—М 8-–±–Є—В–љ—Л–є –Є–ї–Є 16-–±–Є—В–љ—Л–є –і–Њ—Б—В—Г–њ, —В–Њ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ –њ–Њ–і–µ–ї–Є—В—М —А–µ–≥–Є—Б—В—А—Л –љ–∞ —З–∞—Б—В–Є (–љ–∞–њ—А–Є–Љ–µ—А, –љ–∞ —З–µ—В—Л—А–µ 8-–±–Є—В–љ—Л—Е —А–µ–≥–Є—Б—В—А–∞), –Є –і–Њ–±–∞–≤–Є—В—М –ї–Њ–≥–Є–Ї—Г –і–ї—П —Б–Є–≥–љ–∞–ї–Њ–≤ –∞–і—А–µ—Б–∞—Ж–Є–Є —Н—В–Є—Е —А–µ–≥–Є—Б—В—А–Њ–≤ –Є–ї–Є –і–ї—П —Б–Є–≥–љ–∞–ї–Њ–≤ –Є—Е –≤—Л–±–Њ—А–Ї–Є. –Ъ–Њ–і Verilog, –љ–µ–Њ–±—Е–Њ–і–Є–Љ—Л–є –і–ї—П —В–∞–Ї–Њ–є —А–µ–∞–ї–Є–Ј–∞—Ж–Є–Є, –њ–Њ–ї—Г—З–Є—В—Б—П –Њ—З–µ–љ—М –њ—А–Њ—Б—В–Њ–є. –Т—Б–µ —Б–Є–≥–љ–∞–ї—Л, –Ї–Њ—В–Њ—А—Л–Љ –њ—А–Є—Б–≤–∞–Є–≤–∞—О—В—Б—П –Ј–љ–∞—З–µ–љ–Є—П –≤ –±–ї–Њ–Ї–∞—Е always, —В–∞–Ї–ґ–µ –і–µ–Ї–ї–∞—А–Є—А—Г—О—В—Б—П –Ї–∞–Ї reg. –°–Є–≥–љ–∞–ї—Л, –і–µ–Ї–ї–∞—А–Є—А–Њ–≤–∞–љ–љ—Л–µ –Ї–∞–Ї wire, –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П –Ї–∞–Ї —Б–Є–≥–љ–∞–ї—Л —А–∞–Ј—А–µ—И–µ–љ–Є—П –Ј–∞–њ–Є—Б–Є –і–ї—П —А–µ–≥–Є—Б—В—А–Њ–≤ registers –Є pulse_width. –≠—В–Є–Љ —Б–Є–≥–љ–∞–ї–∞–Љ –њ—А–Є—Б–≤–∞–Є–≤–∞—О—В—Б—П –Ј–љ–∞—З–µ–љ–Є—П —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ –Њ–њ–µ—А–∞—В–Њ—А–Њ–≤ –њ–Њ—Б—В–Њ—П–љ–љ–Њ–≥–Њ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П.

–Ю—Б—В–∞–ї—М–љ–∞—П —З–∞—Б—В—М –ї–Є—Б—В–Є–љ–≥–∞ —Б–Њ–і–µ—А–ґ–Є—В –∞–Ї—В—Г–∞–ї—М–љ—Л–є –Ї–Њ–і. –Ч–і–µ—Б—М —З–µ—В—Л—А–µ –±–ї–Њ–Ї–∞ always –Є –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ –Њ–њ–µ—А–∞—В–Њ—А–Њ–≤ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П –≤ –Ї–Њ–љ—Ж–µ. –Ъ–∞–ґ–і—Л–є –±–ї–Њ–Ї always –Њ–њ–Є—Б—Л–≤–∞–µ—В –њ–Њ–≤–µ–і–µ–љ–Є–µ –і–ї—П –Њ–і–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –Є–ї–Є –≥—А—Г–њ–њ—Л —Б–Є–≥–љ–∞–ї–Њ–≤, –Ї–Њ—В–Њ—А—Л–µ –Є–Љ–µ—О—В –Њ–і–Є–љ–∞–Ї–Њ–≤–Њ–µ –±–∞–Ј–Њ–≤–Њ–µ –њ–Њ–≤–µ–і–µ–љ–Є–µ (–і—А—Г–≥–Є–Љ–Є —Б–ї–Њ–≤–∞–Љ–Є, –Є—Б–њ–Њ–ї—М–Ј—Г—О—В —В—Г –ґ–µ —Б–∞–Љ—Г—О –ї–Њ–≥–Є–Ї—Г —Г–њ—А–∞–≤–ї–µ–љ–Є—П). –≠—В–Њ —З–Є—Б—В—Л–є –Љ–µ—В–Њ–і –љ–∞–њ–Є—Б–∞–љ–Є—П –Ї–Њ–і–∞ Verilog, –Ї–Њ—В–Њ—А—Л–є –њ–Њ–Ј–≤–Њ–ї—П–µ—В —Б–Њ—Е—А–∞–љ–Є—В—М –Ї–Њ–і —Г–і–Њ–±–Њ—З–Є—В–∞–µ–Љ—Л–Љ –Є –Љ–µ–љ–µ–µ –њ–Њ–і–≤–µ—А–ґ–µ–љ–љ—Л–Љ –Њ—И–Є–±–Ї–∞–Љ. –Т—Б–µ –±–ї–Њ–Ї–Є always –Є–Љ–µ—О—В –ї–Њ–≥–Є–Ї—Г —Б–±—А–Њ—Б–∞, –Ї–Њ—В–Њ—А–∞—П —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В —Б–Є–≥–љ–∞–ї (—Б–Є–≥–љ–∞–ї—Л) –≤ 0, –Ї–Њ–≥–і–∞ –∞–Ї—В–Є–≤–Є—А—Г–µ—В—Б—П (–њ–µ—А–µ—Е–Њ–і–Є—В –≤ –ї–Њ–≥. 0) —Б–Є–≥–љ–∞–ї clr_n. –•–Њ—В—П —Н—В–Њ –љ–µ —Б—В—А–Њ–≥–Њ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ, –Њ–і–љ–∞–Ї–Њ —П–≤–ї—П–µ—В—Б—П —Е–Њ—А–Њ—И–µ–є –њ—А–∞–Ї—В–Є–Ї–Њ–є —А–∞–Ј—А–∞–±–Њ—В–Ї–Є, –≥–∞—А–∞–љ—В–Є—А—Г—О—Й–µ–є –љ–∞–ї–Є—З–Є–µ –Њ–і–Є–љ–∞–Ї–Њ–≤—Л—Е –Є–Ј–≤–µ—Б—В–љ—Л—Е –љ–∞—З–∞–ї—М–љ—Л—Е —Б–Њ—Б—В–Њ—П–љ–Є–є —Б–Є–≥–љ–∞–ї–Њ–≤ –њ—А–Є —Б–±—А–Њ—Б–µ.

–Я–µ—А–≤—Л–є –±–ї–Њ–Ї always –Њ–њ–Є—Б—Л–≤–∞–µ—В –њ–Њ–≤–µ–і–µ–љ–Є–µ —А–µ–≥–Є—Б—В—А–Њ–≤ –љ–∞ –Ї–∞—А—В–µ —А–µ–≥–Є—Б—В—А–Њ–≤ (register map). –Ч–љ–∞—З–µ–љ–Є–µ —А–µ–≥–Є—Б—В—А–∞ write_data –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В—Б—П –≤ —А–µ–≥–Є—Б—В—А period –Є–ї–Є —А–µ–≥–Є—Б—В—А pulse_width, –µ—Б–ї–Є –≤—Л—Б—В–∞–≤–ї–µ–љ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–Є–є —Б–Є–≥–љ–∞–ї —А–∞–Ј—А–µ—И–µ–љ–Є—П –Ј–∞–њ–Є—Б–Є. –≠—В–Њ –µ–і–Є–љ—Б—В–≤–µ–љ–љ—Л–є —Б–њ–Њ—Б–Њ–± –Є–Ј–Љ–µ–љ–Є—В—М –Ј–љ–∞—З–µ–љ–Є—П –ї—О–±–Њ–≥–Њ –Є–Ј —Н—В–Є—Е —А–µ–≥–Є—Б—В—А–Њ–≤. –°–Є–≥–љ–∞–ї—Л —А–∞–Ј—А–µ—И–µ–љ–Є—П –Ј–∞–њ–Є—Б–Є –Њ–њ—А–µ–і–µ–ї–µ–љ—Л –≤ –Њ–њ–µ—А–∞—В–Њ—А–∞—Е –њ–Њ—Б—В–Њ—П–љ–љ–Њ–≥–Њ –њ—А–Є—Б–≤–∞–Є–≤–∞–љ–Є—П, –љ–∞—Е–Њ–і—П—Й–Є—Е—Б—П –≤ –Ї–Њ–љ—Ж–µ —Д–∞–є–ї–∞. –°–Є–≥–љ–∞–ї—Л —А–∞–Ј—А–µ—И–µ–љ–Є—П –Ј–∞–њ–Є—Б–Є –і–ї—П —А–µ–≥–Є—Б—В—А–Њ–≤ period –Є pulse_width –≤—Л—Б—В–∞–≤–ї—П—О—В—Б—П, –Ї–Њ–≥–і–∞ –≤—Л—Б—В–∞–≤–ї–µ–љ—Л –≥–ї–∞–≤–љ—Л–є —Б–Є–≥–љ–∞–ї —А–∞–Ј—А–µ—И–µ–љ–Є—П –Ј–∞–њ–Є—Б–Є –Є —Б–Є–≥–љ–∞–ї –≤—Л–±–Њ—А–Ї–Є –Ї—А–Є—Б—В–∞–ї–ї–∞ (chip select); –±–Є—В addr –і–Њ–ї–ґ–µ–љ –±—Л—В—М —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ –≤ 0 –і–ї—П —А–µ–≥–Є—Б—В—А–∞ period –Є –≤ 1 –і–ї—П —А–µ–≥–Є—Б—В—А–∞ pulse_width.

–Т—В–Њ—А–Њ–є –±–ї–Њ–Ї always –Њ–њ—А–µ–і–µ–ї—П–µ—В —З—В–µ–љ–Є–µ —А–µ–≥–Є—Б—В—А–Њ–≤ –љ–∞ –Ї–∞—А—В–µ –њ–∞–Љ—П—В–Є. –†–µ–≥–Є—Б—В—А period –±—Г–і–µ—В –љ–∞—Е–Њ–і–Є—В—М—Б—П –њ–Њ –±–∞–Ј–Њ–≤–Њ–Љ—Г –∞–і—А–µ—Б—Г –њ–µ—А–Є—Д–µ—А–Є–є–љ–Њ–≥–Њ —Г—Б—В—А–Њ–є—Б—В–≤–∞, –Є —А–µ–≥–Є—Б—В—А pulse_width –±—Г–і–µ—В –љ–∞—Е–Њ–і–Є—В—М—Б—П –љ–∞ —Б–ї–µ–і—Г—О—Й–µ–Љ 32-–±–Є—В–љ–Њ–Љ —Б–ї–Њ–≤–µ.

–Ґ—А–µ—В–Є–є –Є —З–µ—В–≤–µ—А—В—Л–є –±–ї–Њ–Ї–Є always —А–∞–±–Њ—В–∞—О—В –≤–Љ–µ—Б—В–µ, —З—В–Њ–±—Л —Б—Д–Њ—А–Љ–Є—А–Њ–≤–∞—В—М –≤—Л—Е–Њ–і–љ–Њ–є —Б–Є–≥–љ–∞–ї –®–Ш–Ь. –Ґ—А–µ—В–Є–є –±–ї–Њ–Ї always —А–µ–∞–ї–Є–Ј—Г–µ—В –Є–љ–Ї—А–µ–Љ–µ–љ—В —Б—З–µ—В—З–Є–Ї–∞, –Ї–Њ—В–Њ—А—Л–є –њ–Њ—Б—В–Њ—П–љ–љ–Њ —Б—З–Є—В–∞–µ—В –≤–≤–µ—А—Е –і–Њ –Ј–љ–∞—З–µ–љ–Є—П –≤ —А–µ–≥–Є—Б—В—А–µ period, –њ–Њ—Б–ї–µ —З–µ–≥–Њ —Б–±—А–∞—Б—Л–≤–∞–µ—В—Б—П –≤ 0, –Є —Б–љ–Њ–≤–∞ –љ–∞—З–Є–љ–∞–µ—В —Б—З–Є—В–∞—В—М –≤–≤–µ—А—Е –Њ—В –љ—Г–ї—П. –І–µ—В–≤–µ—А—В—Л–є –±–ї–Њ–Ї always —Б—А–∞–≤–љ–Є–≤–∞–µ—В –Ј–љ–∞—З–µ–љ–Є–µ —Б—З–µ—В—З–Є–Ї–∞ —Б —А–µ–≥–Є—Б—В—А–Њ–Љ pulse_width. –Ъ–Њ–≥–і–∞ –Ј–љ–∞—З–µ–љ–Є–µ —Б—З–µ—В—З–Є–Ї–∞ –Љ–µ–љ—М—И–µ –Ј–љ–∞—З–µ–љ–Є—П –≤ pulse_width, –≤—Л—Е–Њ–і –®–Ш–Ь —Г–і–µ—А–ґ–Є–≤–∞–µ—В—Б—П –≤ –ї–Њ–≥. 1, –Є–љ–∞—З–µ –Њ–љ —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В—Б—П –≤ –ї–Њ–≥. 0.

–Ю–і–љ–∞ –≤–µ—Й—М, –Ї–Њ—В–Њ—А—Г—О —Б–ї–µ–і—Г–µ—В –Є–Љ–µ—В—М –≤ –≤–Є–і—Г - –ї—О–±–Њ–є —Б–Є–≥–љ–∞–ї –Њ–±—П–Ј–∞—В–µ–ї—М–љ–Њ –і–Њ–ї–ґ–µ–љ –Є–Љ–µ—В—М –Њ–њ—А–µ–і–µ–ї–µ–љ–љ–Њ–µ –Ј–љ–∞—З–µ–љ–Є–µ –њ—А–Є –≤—Б–µ—Е –≤–Њ–Ј–Љ–Њ–ґ–љ—Л—Е —Г—Б–ї–Њ–≤–Є—П—Е. –≠—В–Њ –≤–Њ—Б—Е–Њ–і–Є—В –Ї —Д—Г–љ–і–∞–Љ–µ–љ—В–∞–ї—М–љ–Њ–Љ—Г —Б–≤–Њ–є—Б—В–≤—Г –њ–Њ–≤–µ–і–µ–љ–Є—П –∞–њ–њ–∞—А–∞—В—Г—А—Л - –Њ–љ–∞ –≤—Б–µ–≥–і–∞ —А–∞–±–Њ—В–∞–µ—В. –Э–∞–њ—А–Є–Љ–µ—А, –≤ –њ–Њ—Б–ї–µ–і–љ–µ–Љ –±–ї–Њ–Ї–µ always (—В–∞ —З–∞—Б—В—М, –Ї–Њ—В–Њ—А–∞—П –Њ–њ–Є—Б—Л–≤–∞–µ—В —Б–Є–≥–љ–∞–ї off) –њ–Њ—Б–ї–µ–і–љ—П—П —Б—В—А–Њ–Ї–∞ –Ї–Њ–і–∞ –њ—А–Є—Б–≤–∞–Є–≤–∞–µ—В off —Б–∞–Љ–Њ–Љ—Г —Б–µ–±–µ. –≠—В–Њ –Љ–Њ–ґ–µ—В –≤—Л–≥–ї—П–і–µ—В—М –Ї–∞–Ї –Љ–Є–љ–Є–Љ—Г–Љ —Б—В—А–∞–љ–љ—Л–Љ, –љ–Њ –±–µ–Ј —Н—В–Њ–є —Б—В—А–Њ–Ї–Є –Ј–љ–∞—З–µ–љ–Є–µ off —Б—В–∞–ї–Њ –±—Л –љ–µ–Њ–њ—А–µ–і–µ–ї–µ–љ–љ—Л–Љ –і–ї—П —В–∞–Ї–Њ–≥–Њ —Б–ї—Г—З–∞—П. –°–∞–Љ—Л–є –њ—А–Њ—Б—В–Њ–є —Б–њ–Њ—Б–Њ–± –Њ—В—Б–ї–µ–і–Є—В—М –њ–Њ–і–Њ–±–љ—Л–µ —Б–Є—В—Г–∞—Ж–Є–Є - —Г–±–µ–і–Є—В—М—Б—П, —З—В–Њ –≤ –ї—О–±–Њ–є –Љ–Њ–Љ–µ–љ—В –≤—А–µ–Љ–µ–љ–Є —Б–Є–≥–љ–∞–ї, –Ї–Њ—В–Њ—А—Л–є –њ—А–Є—Б–≤–∞–Є–≤–∞–µ—В—Б—П –≤ –≤–µ—В–Ї–µ –Њ–њ–µ—А–∞—В–Њ—А–∞ if, —В–∞–Ї–ґ–µ –њ—А–Є—Б–≤–∞–Є–≤–∞–µ—В—Б—П –Є –≤ –≤–µ—В–Ї–µ –Њ–њ–µ—А–∞—В–Њ—А–∞ else.

[–Ф–Њ—Б—В—Г–њ –Ї –∞–њ–њ–∞—А–∞—В—Г—А–µ –®–Ш–Ь —Б–Њ —Б—В–Њ—А–Њ–љ—Л –Я–Ю]

–Ґ–µ–њ–µ—А—М, –Ї–Њ–≥–і–∞ —А–µ–∞–ї–Є–Ј–∞—Ж–Є—П –∞–њ–њ–∞—А–∞—В—Г—А—Л –љ–∞ Verilog –Ј–∞–≤–µ—А—И–µ–љ–∞, –љ—Г–ґ–љ–Њ –Њ—А–≥–∞–љ–Є–Ј–Њ–≤–∞—В—М —Г–њ—А–∞–≤–ї–µ–љ–Є–µ –®–Ш–Ь —З–µ—А–µ–Ј –Я–Ю, –Ї–Њ—В–Њ—А–Њ–µ –і–Њ–ї–ґ–љ–Њ –Ј–∞–њ–Є—Б—Л–≤–∞—В—М —А–µ–≥–Є—Б—В—А—Л —З–µ—А–µ–Ј –Ї–∞—А—В—Г –њ–∞–Љ—П—В–Є (register map). –Т—Л –Љ–Њ–ґ–µ—В–µ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –њ—А–Њ—Б—В—Г—О —Б—В—А—Г–Ї—В—Г—А—Г –і–∞–љ–љ—Л—Е —Б —Г–Ї–∞–Ј–∞—В–µ–ї–µ–Љ, —З—В–Њ–±—Л –њ–Њ–і–Ї–ї—О—З–Є—В—М—Б—П –Ї —А–µ–≥–Є—Б—В—А–∞–Љ –≤ –±–ї–Њ–Ї–µ –®–Ш–Ь.

typedef volatile struct

{

uint32_t period;

uint32_t pulse_width;

} PWM;

–Э–∞–њ—А–Є–Љ–µ—А, —А–∞–±–Њ—В—Г –®–Ш–Ь –Љ–Њ–ґ–љ–Њ –Њ—В—Б–ї–µ–і–Є—В—М —Б –њ–Њ–Љ–Њ—Й—М—О —П—А–Ї–Њ—Б—В–Є –њ–Њ–і–Ї–ї—О—З–µ–љ–љ–Њ–≥–Њ –Ї –≤—Л—Е–Њ–і—Г –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –®–Ш–Ь —Б–≤–µ—В–Њ–і–Є–Њ–і–∞ (LED). –Я–µ—А–µ–Љ–µ–љ–љ–∞—П, –Ї–Њ—В–Њ—А–∞—П –љ–∞–Ј–≤–∞–љ–∞ pLED, –Є–Љ–µ—О—Й–∞—П —В–Є–њ PWM*, –і–Њ–ї–ґ–љ–∞ –±—Л—В—М –Є–љ–Є—Ж–Є–∞–ї–Є–Ј–Є—А–Њ–≤–∞–љ–∞ –±–∞–Ј–Њ–≤—Л–Љ –∞–і—А–µ—Б–Њ–Љ –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –®–Ш–Ь. –≠—В–Њ –∞–±—Б—В—А–∞–≥–Є—А—Г–µ—В –∞–њ–њ–∞—А–∞—В—Г—А—Г –®–Ш–Ь –љ–∞ —Б—В—А—Г–Ї—В—Г—А—Г –і–∞–љ–љ—Л—Е PWM. –Ч–∞–њ–Є—Б—М –≤ pLED->period —Г—Б—В–∞–љ–Њ–≤–Є—В –Є–ї–Є –Є–Ј–Љ–µ–љ–Є—В period. –Ч–∞–њ–Є—Б—М –≤ pLED->pulse_width –њ–Њ–Љ–µ–љ—П–µ—В —Б–Ї–≤–∞–ґ–љ–Њ—Б—В—М, –≤ —А–µ–Ј—Г–ї—М—В–∞—В–µ —З–µ–≥–Њ —П—А–Ї–Њ—Б—В—М —Б–≤–µ—В–Њ–і–Є–Њ–і–∞ —Г–Љ–µ–љ—М—И–Є—В—Б—П –Є–ї–Є —Г–≤–µ–ї–Є—З–Є—В—Б—П (–Ї—Б—В–∞—В–Є, –Ј–∞–њ–Є—Б—М –≤ pLED->period —В–∞–Ї–ґ–µ –њ–Њ–Љ–µ–љ—П–µ—В —П—А–Ї–Њ—Б—В—М, —В–∞–Ї –Ї–∞–Ї —Б—А–µ–і–љ–µ–µ –Ј–љ–∞—З–µ–љ–Є–µ –љ–∞ –≤—Л—Е–Њ–і–µ —И–Є–Љ –Ј–∞–≤–Є—Б–Є—В –Њ—В —Б–Ї–≤–∞–ґ–љ–Њ—Б—В–Є, —В. –µ. –Њ—В —Б–Њ–Њ—В–љ–Њ—И–µ–љ–Є—П period/pulse_width). –Х—Б–ї–Є –љ—Г–ґ–љ–Њ –њ–Њ–ї—Г—З–Є—В—М –Љ–Є–≥–∞–љ–Є–µ —Б–≤–µ—В–Њ–і–Є–Њ–і–∞, —В–Њ –Љ–Њ–ґ–љ–Њ –ї–Є–±–Њ –њ–µ—А–Є–Њ–і–Є—З–µ—Б–Ї–Є –њ–µ—А–µ–Ј–∞–њ–Є—Б—Л–≤–∞—В—М –Ј–љ–∞—З–µ–љ–Є–µ period, —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞—П –µ–≥–Њ —В–Њ –≤ 0, —В–Њ –≤ –љ—Г–ґ–љ–Њ–µ –Ј–љ–∞—З–µ–љ–Є–µ, –±–ї–Є–Ј–Ї–Њ–µ –Ї pulse_width, –ї–Є–±–Њ –Љ–Њ–ґ–љ–Њ —Б–і–µ–ї–∞—В—М –њ–µ—А–Є–Њ–і pulse_width –і–Њ—Б—В–∞—В–Њ—З–љ–Њ –±–Њ–ї—М—И–Є–Љ, —З—В–Њ–±—Л –≥–ї–∞–Ј —З–µ–ї–Њ–≤–µ–Ї–∞ —Г—Б–њ–µ–≤–∞–ї –Ј–∞–Љ–µ—З–∞—В—М –Љ–µ—А—Ж–∞–љ–Є–µ —Б–≤–µ—В–Њ–і–Є–Њ–і–∞, –∞ –Ј–љ–∞—З–µ–љ–Є–µ period —Г—Б—В–∞–љ–Њ–≤–Є—В—М —А–∞–≤–љ—Л–Љ –њ–Њ–ї–Њ–≤–Є–љ–µ –Ј–љ–∞—З–µ–љ–Є—П pulse_width.

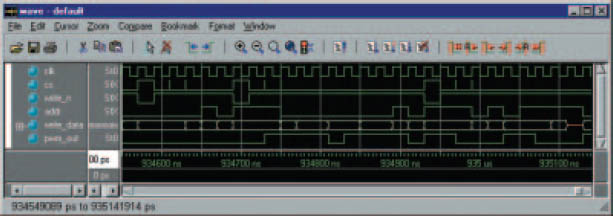

–†–µ–∞–ї–Є–Ј–∞—Ж–Є—П –љ–∞ Verilog –∞–њ–њ–∞—А–∞—В—Г—А—Л –®–Ш–Ь, –њ–Њ–Ї–∞–Ј–∞–љ–љ–∞—П –≤ –Ы–Є—Б—В–Є–љ–≥–µ 3, –±—Л–ї–∞ –њ—А–Њ–≤–µ—А–µ–љ–∞ –љ–∞ –њ—А–Њ—Ж–µ—Б—Б–Њ—А–љ–Њ–є —Б–Є—Б—В–µ–Љ–µ Altera Nios —Б –њ—А–Њ–≥—А–∞–Љ–Љ–Њ–є, –љ–∞–њ–Є—Б–∞–љ–љ–Њ–є –љ–∞ C, –њ—А–Є–Љ–µ—А–љ–Њ —В–∞–Ї, –Ї–∞–Ї –±—Л–ї–Њ –Њ–њ–Є—Б–∞–љ–Њ –≤—Л—И–µ. Altera SOPC Builder —Б–Њ–Ј–і–∞–µ—В –Љ–∞–Ї—А–Њ—Б, –Ї–Њ—В–Њ—А—Л–є —Г–њ—А–Њ—Й–∞–µ—В —Б–Њ–≤–Љ–µ—Б—В–љ—Г—О —Б–Є–Љ—Г–ї—П—Ж–Є—О –њ—А–Њ–µ–Ї—В–∞ –≤ ModelSim, —Б–Є–Љ—Г–ї—П—В–Њ—А–µ –∞–њ–њ–∞—А–∞—В—Г—А—Л –Њ—В Mentor Graphics. –Ш—Б–њ–Њ–ї—М–Ј—Г—П —Б–Є–Љ—Г–ї—П—В–Њ—А ModelSim, –Љ–Њ–ґ–љ–Њ —Г–≤–Є–і–µ—В—М –і–Є–∞–≥—А–∞–Љ–Љ—Л –Є–Ј–Љ–µ–љ–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤ –®–Ш–Ь –≤–Љ–µ—Б—В–µ —Б —А–∞–±–Њ—В–Њ–є —Б–Є—Б—В–µ–Љ—Л –њ—А–Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є –Ї–Њ–і–∞ C.

–Ы–Є—Б—В–Є–љ–≥ 4 –њ–Њ–Ї–∞–Ј—Л–≤–∞–µ—В –Ї–Њ–і C, –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л–є –і–ї—П –≥–µ–љ–µ—А–∞—Ж–Є–Є —Д–Њ—А–Љ—Л —Б–Є–≥–љ–∞–ї–∞ –љ–∞ —А–Є—Б. 2. –Ю—Б—Ж–Є–ї–ї–Њ–≥—А–∞–Љ–Љ—Л —Б–Є–Љ—Г–ї—П—В–Њ—А–∞ –њ–Њ–Ї–∞–Ј—Л–≤–∞—О—В –њ–Њ–≤–µ–і–µ–љ–Є–µ –њ–Њ–і—Е–Њ–і—П—Й–Є—Е —Б–Є–≥–љ–∞–ї–Њ–≤ –®–Ш–Ь. –Ъ–Њ–і C –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В —А–µ–≥–Є—Б—В—А—Л PWM, —З—В–Њ–±—Л —Б–Њ–Ј–і–∞—В—М –≤—Л—Е–Њ–і–љ–Њ–є —Б–Є–≥–љ–∞–ї –®–Ш–Ь —Б —И–Є—А–Є–љ–Њ–є –Є–Љ–њ—Г–ї—М—Б–∞ 4. –Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ –љ–∞ –љ–∞—З–∞–ї–Њ –Њ—Б—Ж–Є–ї–ї–Њ–≥—А–∞–Љ–Љ—Л, –≥–і–µ —Б–Є–≥–љ–∞–ї—Л cs –Є wr_n —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞—О—В—Б—П –і–≤–∞–ґ–і—Л - –Ј–і–µ—Б—М –Љ—Л –Ј–∞–њ–Є—Б—Л–≤–∞–µ–Љ —А–µ–≥–Є—Б—В—А—Л period –Є pulse_width (—Б–Є–≥–љ–∞–ї –∞–і—А–µ—Б–∞ –љ–∞—Е–Њ–і–Є—В—Б—П –≤ –ї–Њ–≥. 0 –њ—А–Є –Ј–∞–њ–Є—Б–Є —А–µ–≥–Є—Б—В—А–∞ period, –Є –≤ –ї–Њ–≥. 1 –њ—А–Є –Ј–∞–њ–Є—Б–Є —А–µ–≥–Є—Б—В—А–∞ pulse_width).

–Ы–Є—Б—В–Є–љ–≥ 4. –Ґ–µ—Б—В–Њ–≤–Њ–µ –Я–Ю, –Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ–Њ–µ –і–ї—П –≥–µ–љ–µ—А–∞—Ж–Є–Є –Њ—Б—Ж–Є–ї–ї–Њ–≥—А–∞–Љ–Љ —Б–Є–Љ—Г–ї—П—В–Њ—А–∞ –љ–∞ —А–Є—Б. 2.

void main(void)

{

PWM* const pLED = BASE_PWM_ADDRESS;

pLED->period = 5;

pLED->pulse_width = 4;

asm("nop");

asm("nop");

asm("nop");

pLED->pulse_width = 2;

}

–†–Є—Б. 2. –Ф–Є–∞–≥—А–∞–Љ–Љ—Л –∞–њ–њ–∞—А–∞—В—Г—А—Л PWM, —Г–њ—А–∞–≤–ї—П–µ–Љ–Њ–є –њ—А–Њ–≥—А–∞–Љ–Љ–љ—Л–Љ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ–Љ.

–Я–Њ—Б–ї–µ —В–Њ–≥–Њ, –Ї–∞–Ї –љ–Њ–≤—Л–µ –Ј–љ–∞—З–µ–љ–Є—П –±—Л–ї–Є –Ј–∞–њ–Є—Б–∞–љ—Л –≤ —А–µ–≥–Є—Б—В—А—Л, —Б–Є–≥–љ–∞–ї pwm_output –љ–∞—З–љ–µ—В –Њ—В—А–∞–ґ–∞—В—М —Н—В–Њ –Є–Ј–Љ–µ–љ–µ–љ–Є–µ. –Ч–∞—В–µ–Љ –≤ –њ—А–Њ–≥—А–∞–Љ–Љ–µ –љ–∞ C –±—Л–ї–∞ –і–Њ–±–∞–≤–ї–µ–љ–∞ –љ–µ–Ї–Њ—В–Њ—А–∞—П –Ј–∞–і–µ—А–ґ–Ї–∞ (–Є–љ—Б—В—А—Г–Ї—Ж–Є—П–Љ–Є –∞—Б—Б–µ–Љ–±–ї–µ—А–∞ NOP), —З—В–Њ–±—Л –Љ–Њ–ґ–љ–Њ –±—Л–ї–Њ —Г–≤–Є–і–µ—В—М –≤ —Б–Є–Љ—Г–ї—П—В–Њ—А–µ —А–µ–Ј—Г–ї—М—В–∞—В—Л –Є–Ј–Љ–µ–љ–µ–љ–Є—П. –Т –Ї–Њ–љ—Ж–µ —И–Є—А–Є–љ–∞ –Є–Љ–њ—Г–ї—М—Б–∞ –±—Л–ї–∞ –Є–Ј–Љ–µ–љ–µ–љ–∞ –љ–∞ 2 —В–∞–Ї—В–∞, –Є —Д–Њ—А–Љ–∞ —Б–Є–≥–љ–∞–ї–∞ –®–Ш–Ь –њ–Њ–Љ–µ–љ—П–µ—В—Б—П –≤ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–Є–Є —Б –њ–µ—А–Є–Њ–і–Њ–Љ –Є–Ј 5 —В–∞–Ї—В–Њ–≤.

[–С–µ—А–µ–Љ –ї—Г—З—И–µ–µ –Є–Ј –Ї–∞–ґ–і–Њ–≥–Њ –Љ–Є—А–∞]

–І–∞—Б—В—М —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –≤—Б—В—А–∞–Є–≤–∞–µ–Љ–Њ–є —Б–Є—Б—В–µ–Љ—Л - —А–∞—Ж–Є–Њ–љ–∞–ї—М–љ–Њ —А–∞–Ј–і–µ–ї–Є—В—М –µ—С –љ–∞ –∞–њ–њ–∞—А–∞—В–љ—Г—О –Є –њ—А–Њ–≥—А–∞–Љ–Љ–љ—Г—О —З–∞—Б—В–Є, —З—В–Њ–±—Л –њ–Њ–ї—Г—З–Є—В—М –Љ–∞–Ї—Б–Є–Љ—Г–Љ –≤—Л–≥–Њ–і—Л –Њ—В –Ї–∞–ґ–і–Њ–є. –Я–Њ –Љ–µ—А–µ —А–∞–Ј–≤–Є—В–Є—П —Б—А–µ–і—Б—В–≤ —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –Ј–∞–Љ–µ–љ–∞ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–≥–Њ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П –љ–∞ –∞–њ–њ–∞—А–∞—В–љ–Њ–µ –Є –љ–∞–Њ–±–Њ—А–Њ—В —Б—В–∞–љ–Њ–≤–Є—В—Б—П –і–ї—П —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–∞ –≤—Б–µ –±–Њ–ї–µ–µ –њ—А–Њ–Ј—А–∞—З–љ–Њ–є.

–Х—Б–ї–Є –Т—Л –њ–Њ–љ—П–ї–Є –Ї–Њ–љ—Ж–µ–њ—Ж–Є–Є, –Њ–њ–Є—Б–∞–љ–љ—Л–µ –≤ —Н—В–Њ–є —Б—В–∞—В—М–µ, —В–Њ –Є–Љ–µ–µ—В–µ –љ–∞—З–∞–ї—М–љ—Л–µ –Ј–љ–∞–љ–Є—П –і–ї—П —Б—В–∞—А—В–∞ —А–∞–Ј—А–∞–±–Њ—В–Ї–Є –∞–њ–њ–∞—А–∞—В—Г—А—Л –≤ FPGA, –Ї–Њ—В–Њ—А—Г—О –Љ–Њ–ґ–љ–Њ –њ–Њ–і–Ї–ї—О—З–Є—В—М –Ї –Љ–Є–Ї—А–Њ–њ—А–Њ—Ж–µ—Б—Б–Њ—А–љ–Њ–є —Б–Є—Б—В–µ–Љ–µ –≤ –Ї–∞—З–µ—Б—В–≤–µ –≤–љ–µ—И–љ–µ–є –∞–њ–њ–∞—А–∞—В—Г—А—Л, –њ–Њ—Б–ї–µ —З–µ–≥–Њ –Љ–Њ–ґ–љ–Њ –њ—А–Њ—Б—В–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ –Ј–∞–њ–Є—Б—Л–≤–∞—В—М –≤ –љ–µ—С (–Є–ї–Є —Б—З–Є—В—Л–≤–∞—В—М) —Г–њ—А–∞–≤–ї—П—О—Й–Є–µ –њ–∞—А–∞–Љ–µ—В—А—Л (–Є–ї–Є –і–∞–љ–љ—Л–µ). –Я–Њ—Б–Ї–Њ–ї—М–Ї—Г –љ–µ–Ї–Њ—В–Њ—А—Л–µ –∞–ї–≥–Њ—А–Є—В–Љ—Л —А–∞–±–Њ—В–∞—О—В –љ–∞–Љ–љ–Њ–≥–Њ –±—Л—Б—В—А–µ–µ –љ–∞ –∞–њ–њ–∞—А–∞—В—Г—А–µ, —З–µ–Љ –≤ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–Љ –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–Є, –њ–µ—А–µ–≤–Њ–і –∞–ї–≥–Њ—А–Є—В–Љ–∞ –Є–Ј –њ—А–Њ–≥—А–∞–Љ–Љ—Л –љ–∞ –∞–њ–њ–∞—А–∞—В—Г—А—Г –Љ–Њ–ґ–µ—В –Ј–љ–∞—З–Є—В–µ–ї—М–љ–Њ —Г—Б–Ї–Њ—А–Є—В—М –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В—М —Б–Є—Б—В–µ–Љ—Л –Є —А–∞–Ј–≥—А—Г–Ј–Є—В—М –њ—А–Њ—Ж–µ—Б—Б–Њ—А, –Є —З–∞—Б—В–Њ –њ–Њ–Ј–≤–Њ–ї—П–µ—В —Б–љ–Є–Ј–Є—В—М —Н–љ–µ—А–≥–Њ–њ–Њ—В—А–µ–±–ї–µ–љ–Є–µ –њ—А–Є–±–Њ—А–∞. –Ґ–∞–Ї–∞—П –Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П —Б–Є—Б—В–µ–Љ—Л –Є–Ј–≤–µ—Б—В–љ–∞ –Ї–∞–Ї –∞–њ–њ–∞—А–∞—В–љ–Њ–µ —Г—Б–Ї–Њ—А–µ–љ–Є–µ. –≠—В–Њ –Ї–ї—О—З–µ–≤–∞—П —Д—Г–љ–Ї—Ж–Є—П –і–ї—П –њ—А–Њ—Ж–µ—Б—Б–Њ—А–Њ–≤, —Н—Д—Д–µ–Ї—В–Є–≤–љ–Њ —А–µ–∞–ї–Є–Ј—Г–µ–Љ—Л—Е –≤ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–Њ–є –ї–Њ–≥–Є–Ї–µ. –Т –Ї–Њ–љ—Ж–µ –Ї–Њ–љ—Ж–Њ–≤ –і–∞–ґ–µ —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї –Я–Ю –Є–Љ–µ–µ—В –њ—А–∞–≤–Њ —Г–ї—Г—З—И–Є—В—М –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В—М –Є —Н—Д—Д–µ–Ї—В–Є–≤–љ–Њ—Б—В—М —Б–Є—Б—В–µ–Љ—Л —Б –њ–Њ–Љ–Њ—Й—М—О –∞–њ–њ–∞—А–∞—В–љ–Њ–≥–Њ —Г—Б–Ї–Њ—А–µ–љ–Є—П.

[–°—Б—Л–ї–Ї–Є]

1. The C Programmers Guide to Verilog site:eetasia.com.

2. –Я—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є–µ XC2C64A –≤ —Б—А–µ–і–µ Xilinx ISE WebPack.

3. –Т–≤–µ–і–µ–љ–Є–µ –≤ Verilog. |