|

ą£ąĖą║čĆąŠčüčģąĄą╝čŗ FT2232H ąĖ FT4232H čŹč鹊 ą┐ąĄčĆą▓čŗąĄ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ UART/FIFO ą║ąŠą╝ą┐ą░ąĮąĖąĖ FTDI, čĆąĄą░ą╗ąĖąĘčāčÄčēąĖąĄ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ USB (USB 2.0 Hi-Speed) ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ 480 ą╝ąĄą│ą░ą▒ąĖčé/čüąĄą║). ąŁčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ čüąĖčüč鹥ą╝čŗ MPSSE (Multi-Protocol Synchronous Serial Engine). ąŻ FT2232H [2] ąĖą╝ąĄąĄčéčüčÅ 2 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą┐ąŠčĆčéą░, ąĖ ąŠąĮąĖ ąŠą▒ą░ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ MPSSE. ąŻ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FT4232H ąĖą╝ąĄąĄčéčüčÅ 4 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą┐ąŠčĆčéą░, ąŠą┤ąĮą░ą║ąŠ č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ A ąĖ ą║ą░ąĮą░ą╗ B čŹč鹊ą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ MPSSE.

ą£ąĖą║čĆąŠčüčģąĄą╝ą░ FT232H, ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĮą░čÅ ą▓ 2011 ą│ąŠą┤čā, ą┐ąŠčüčéčĆąŠąĄąĮą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ čüąĄą╝ąĄą╣čüčéą▓ą░ FTDI Hi-Speed USB. ąŻ FT232H ąĄčüčéčī ąŠą┤ąĖąĮ ą┐ąŠčĆčé UART/FIFO IC ąĖ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ąĖąĮč鹥čĆč乥ą╣čü MPSSE, ą║ą░ą║ ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąĮąŠą▓čŗčģ čĆąĄąČąĖą╝ąŠą▓.

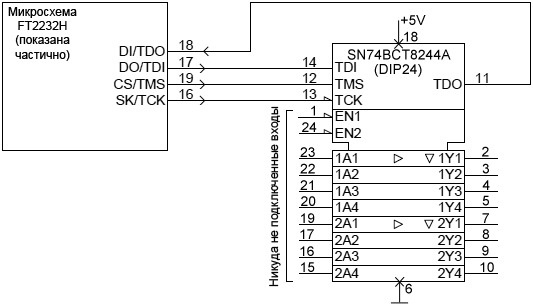

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ MPSSE ą╝ąŠąČąĄčé čāą┐čĆąŠčüčéąĖčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓ (ą┤ą╗čÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ ą▓ čĆą░ąĘčĆą░ą▒ąŠčéą║ąĄ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ USB ą▓ SPI, I2C, JTAG, ąĖ čé. ą┐.). ąÆ čŹč鹊ą╝ ą░ą┐ąĮąŠčāč鹥 (ą┐ąĄčĆąĄą▓ąŠą┤ [1]) čĆą░čüčüą╝ą░čéčĆąĖą▓ą░ąĄčéčüčÅ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠąĄ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖąĄ, čéčĆąĄą▒čāąĄą╝ą░čÅ ą┤ą╗čÅ čŹą╝čāą╗čÅčåąĖąĖ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą║ čåąĄą┐ąŠčćą║ąĄ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ JTAG TAP ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ SN74BCT8244A (8-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą▒čāč乥čĆ) čü ą┐ąŠą╝ąŠčēčīčÄ FT2232H. ą¤ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĖ ą╝ąŠą│čāčé ą▓ąĘčÅčéčī ą┐ąŠą║ą░ąĘą░ąĮąĮčŗą╣ ą┐čĆąĖą╝ąĄčĆ čüčģąĄą╝čŗ ąĖ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ, čćč鹊ą▒čŗ ąĮą░čćą░čéčī ąĮą░ čŹč鹊ą╣ ąŠčüąĮąŠą▓ąĄ čüą▓ąŠčÄ čüąŠą▒čüčéą▓ąĄąĮąĮčāčÄ čĆą░ąĘčĆą░ą▒ąŠčéą║čā. ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮčŗą╣ ą╗ąĖčüčéąĖąĮą│ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ ą║ąŠą┤ą░ ą┤ą░ąĮ č鹊ą╗čīą║ąŠ ą║ą░ą║ ąĖą╗ą╗čÄčüčéčĆą░čåąĖčÅ ą┐čĆąĖąĮčåąĖą┐ą░ čĆą░ą▒ąŠčéčŗ čü JTAG ą┤ą╗čÅ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ (Boundary Scan), ąĖ čŹč鹊čé ą║ąŠą┤ ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą║ąŠą╝ą┐ą░ąĮąĖąĄą╣ FTDI. FT232H ąĖ FT4232H čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮčŗ ą▓ą╝ąĄčüč鹥 čü ą┐čĆąĖą╝ąĄčĆąŠą╝, ą┐ąŠą║ą░ąĘą░ąĮąĮąŠą╝ ą▓ čŹč鹊ą╝ ą░ą┐ąĮąŠčāč鹥, čģąŠčéčÅ čĆą░ąĘą▓ąŠą┤ą║ą░ ą▓čŗą▓ąŠą┤ąŠą▓ ąĖ ą▓čŗą▒ąŠčĆ ą┐ąŠčĆčéą░ ą┤ąŠą╗ąČąĄąĮ ą┐ąŠą┤čģąŠą┤ąĖčéčī ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ.

ąÆ čŹč鹊ą╝ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ čéą░ą║ąČąĄ čāą┤ą▓ąŠąĄąĮčŗ ąŠąČąĖą┤ą░ąĄą╝čŗąĄ ą┤ą╗čÅ SN74BCT8244A ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ JTAG, čćč鹊ą▒čŗ ą┤ąŠą║ą░ąĘą░čéčī čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĖą╝ąĄčĆą░.

[ąÆą▓ąĄą┤ąĄąĮąĖąĄ ą▓ FTDI MPSSE]

Multi-Protocol Synchronous Serial Engine (MPSSE) čŹč鹊 čäčāąĮą║čåąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą║ą╗ąĖąĄąĮčéčüą║ąĖčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ FTDI, ą║ąŠč鹊čĆą░čÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé 菹╝čāą╗ąĖčĆąŠą▓ą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓, ą▓ą║ą╗čÄčćą░čÅ SPI, I2C ąĖ JTAG.

ą×ą┤ąĖąĮ ą▒ą╗ąŠą║ MPSSE ą┤ąŠčüčéčāą┐ąĄąĮ ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ FT2232D, ą║ą╗ąĖąĄąĮčéčüą║ąŠą╝ čāčüčéčĆąŠą╣čüčéą▓ąĄ Full-Speed USB 2.0. FT2232D ą╝ąŠąČąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ ą┤ąŠ 6 Mbps (6 ą╝ąĄą│ą░ą▒ąŠą┤).

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ą▓ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ FT2232H ąĖ FT4232H ąĖą╝ąĄąĄčéčüčÅ ą┐ąŠ 2 ą▒ą╗ąŠą║ą░ MPSSE, ąĖ ąŠą▒ąĄ čŹčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ čÅą▓ą╗čÅčÄčéčüčÅ ą║ą╗ąĖąĄąĮčéčüą║ąĖą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ Hi-Speed USB 2.0. ąÜą░ąČą┤čŗą╣ ąĖąĘ ą▒ą╗ąŠą║ąŠą▓ MPSSE ą╝ąŠąČąĄčé ąŠčüčāčēąĄčüčéą▓ą╗čÅčéčī čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ąĮą░ čüą║ąŠčĆąŠčüčéąĖ ą┤ąŠ 30 Mbps (30 ą╝ąĄą│ą░ą▒ąŠą┤). MPSSE ą▓ FT2232H ąĖ FT4232H ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąĮąŠą▓čŗąĄ ą║ąŠą╝ą░ąĮą┤čŗ ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čĆąĄąČąĖą╝ąŠą▓ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, čćč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ąĖąĮč鹥čĆč乥ą╣čüą░ CPU ąĖ čüąĖąĮčģčĆąŠąĮąĮąŠą╝ čĆąĄąČąĖą╝ąĄ FIFO (ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮą░čÅ čłąĖąĮą░). FT232H čüąŠą┤ąĄčƹȹĖčé ąŠą┤ąĖąĮ ą▒ą╗ąŠą║ MPSSE, čüąĖąĮčģčĆąŠąĮąĮčŗą╣ CPU FIFO ąĖ ąĮąŠą▓čŗąĄ čĆąĄąČąĖą╝čŗ čćąĖą┐ą░ FT1248. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐čĆąŠ čŹčéąĖ ąĮąŠą▓čŗąĄ čĆąĄąČąĖą╝čŗ čüą╝. ą▓ ą░ą┐ąĮąŠčāč鹥 AN_135 (ą▒ą░ąĘąŠą▓ą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐čĆąŠ MPSSE) ąĖ AN_167 (ą▒ą░ąĘąŠą▓ą░čÅ ąĖąĮč乊čĆą╝ą░čåąĖčÅ ą┐čĆąŠ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąĖą╣ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣/ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü čćąĖą┐ą░ FT1248).

ąÆ čŹč鹊ą╝ ą░ą┐ąĮąŠčāč鹥 ąŠą┐ąĖčüą░ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ MPSSE ą┤ą╗čÅ čŹą╝čāą╗čÅčåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ JTAG. ąŚą┤ąĄčüčī ąĄčüčéčī ą╝ąĮąŠą│ąŠ čüčüčŗą╗ąŠą║ ąĮą░ ą░ą┐ąĮąŠčāčé AN_108 (ąŠą┐ąĖčüą░ąĮąĖąĄ ą║ąŠą╝ą░ąĮą┤ąĮąŠą│ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▒ą╗ąŠą║ą░ MPSSE ąĖ čĆąĄąČąĖą╝ąŠą▓ 菹╝čāą╗čÅčåąĖąĖ čłąĖąĮčŗ čģąŠčüčéą░ MCU), ą║ąŠč鹊čĆčŗą╣ čéą░ą║ąČąĄ ą┤ąŠčüčéčāą┐ąĄąĮ ąĮą░ čüą░ą╣č鹥 FTDI.

[ą¦č鹊 čéą░ą║ąŠąĄ JTAG]

ąĪąŠą▓čĆąĄą╝ąĄąĮąĮčŗąĄ 菹╗ąĄą║čéčĆąŠąĮąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čüąŠčüč鹊čÅčé ąĖąĘ ą▒ąŠą╗čīčłąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čüą╗ąŠąČąĮčŗčģ ąĖąĮč鹥ą│čĆą░ą╗čīąĮčŗčģ čüčģąĄą╝. ą×ą▒čŗčćąĮą░čÅ ą▓čüčéčĆą░ąĖą▓ą░ąĄą╝ą░čÅ čüąĖčüč鹥ą╝ą░ ą╝ąŠąČąĄčé čüąŠą┤ąĄčƹȹ░čéčī ą▓ čüąĄą▒ąĄ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą┐čĆąŠčåąĄčüčüąŠčĆąŠą▓ (CPU), ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ą░ą╝čÅčéąĖ ąĖ čé. ą┐. ą¤čĆąĖ čéą░ą║ąŠą╣ čüą╗ąŠąČąĮąŠčüčéąĖ čćą░čüčéčī ąĮąĄą▓ąŠąĘą╝ąŠąČąĮąŠ ą┐čĆąŠą▓ąĄčĆčÅčéčī ąĖ č鹥čüčéąĖčĆąŠą▓ą░čéčī čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī ąĖą╝ąĄčÄčēąĄą│ąŠčüčÅ ą┤ąĖąĘą░ą╣ąĮą░.

ąÆ 1990 ą│ąŠą┤čā ąĖąĮčüčéąĖčéčāčé ąĖąĮąČąĄąĮąĄčĆąŠą▓ 菹╗ąĄą║čéčĆąĖč湥čüčéą▓ą░ ąĖ 菹╗ąĄą║čéčĆąŠąĮąĖą║ąĖ (Institute of Electrical and Electronics Engineers, IEEE) čĆą░čéąĖčäąĖčåąĖčĆąŠą▓ą░ą╗ą░ čüčéą░ąĮą┤ą░čĆčé 1149.1, ą║ąŠč鹊čĆčŗą╣ ą▒čŗą╗ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĄą╣ Joint Test Action Group (JTAG). ąŁč鹊čé čüčéą░ąĮą┤ą░čĆčé ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ąŠčüąĮąŠą▓ąĮąŠą╣ čüą╝čŗčüą╗ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ č鹥čģąĮąŠą╗ąŠą│ąĖąĖ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ (boundary-scan), ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠą╣ ą┤ą╗čÅ ą┐čĆąŠą▓ąĄčĆą║ąĖ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéąĖ ąĖąĮč鹥ą│čĆą░ą╗čīąĮčŗčģ čüčģąĄą╝. ąóąĄčģąĮąŠą╗ąŠą│ąĖčÅ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ąŠčé čĆą░ąĘąĮčŗčģ ą▓ąĄąĮą┤ąŠčĆąŠą▓ ą▒čŗčéčī ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĮčŗą╝ąĖ ą▓ ąŠą┤ąĮąŠą╣ čåąĄą┐ąŠčćą║ąĄ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą┤ąŠčüčéčāą┐ ą║ąŠ ą▓čüąĄą╝ ąĖčģ ą▓čŗą▓ąŠą┤ą░ą╝ ą▓čģąŠą┤ąŠą▓ ąĖ ą▓čŗčģąŠą┤ąŠą▓ (I/O). ąÆą╝ąĄčüč鹥 čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą│ąŠ ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮąĖčÅ, čéą░ą║ąŠą│ąŠ ą║ą░ą║ ą╝ą░čéčĆąĖčåčŗ čēčāą┐ąŠą▓, čüčéą░ą╗ąŠ ą▓ąŠąĘą╝ąŠąČąĮčŗą╝ ą┤ąĄą╗ą░čéčī ą┐ąŠą╗ąĮčāčÄ ą┐čĆąŠą▓ąĄčĆą║čā ą▓čüąĄą╣ čüčģąĄą╝čŗ 菹╗ąĄą║čéčĆąŠąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░. ąóąĄčģąĮąŠą╗ąŠą│ąĖčÄ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ IEEE 1149.1 čćą░čüč鹊 ąĮą░ąĘčŗą▓ą░čÄčé "čüčéą░ąĮą┤ą░čĆč鹊ą╝ JTAG". ą£ąĮąŠą│ąĖąĄ ąŠą┐čāą▒ą╗ąĖą║ąŠą▓ą░ąĮąĮčŗąĄ ą┤ąŠą║čāą╝ąĄąĮčéčŗ ąĖ čüčéą░čéčīąĖ ą▓ąĘą░ąĖą╝ąŠąĘą░ą╝ąĄąĮčÅąĄą╝ąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčé čŹčéąĖ č鹥čĆą╝ąĖąĮčŗ.

IEEE 1149.1 ą▓ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ čĆą░ąĘ ą▒čŗą╗ ąŠą▒ąĮąŠą▓ą╗ąĄąĮ ą▓ 2001 ą│ąŠą┤čā. ąöąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ čüčéą░ąĮą┤ą░čĆč鹊ą▓ IEEE 1149.1 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čéą░ą║ąĖąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ, ą║ą░ą║ ą┐čĆąŠą▓ąĄčĆą║čā ą░ąĮą░ą╗ąŠą│ąŠą▓čŗčģ čüčģąĄą╝ ą▓ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ č鹥čüčéčā čåąĖčäčĆąŠą▓čŗčģ čüčģąĄą╝. ąÆąŠčé čŹčéąĖ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗąĄ čüčéą░ąĮą┤ą░čĆčéčŗ: 1149.4 - Analog Boundary Scan (ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠąĄ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠąĄ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖąĄ), 1149.6 - Advanced I/O (čāčüąŠą▓ąĄčĆčłąĄąĮčüčéą▓ąŠą▓ą░ąĮąĮčŗą╣ ą▓ą▓ąŠą┤/ą▓čŗą▓ąŠą┤) ąĖ 1532 - In System Configuration (ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓ąĮčāčéčĆąĖ čüąĖčüč鹥ą╝čŗ). ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čüčéą░ąĮą┤ą░čĆčé ąŠą▒čŗčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą┐ą░ą╝čÅčéąĖ ąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ąŠą╣ ą╗ąŠą│ąĖą║ąĖ, čéą░ą║ąŠą╣ ą║ą░ą║ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FPGA ąĖ CPLD.

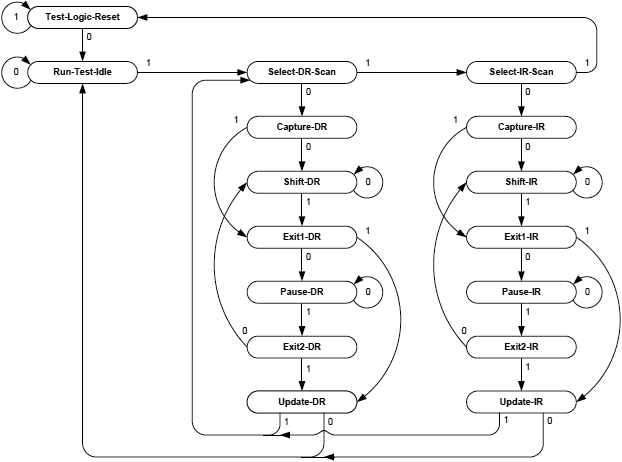

JTAG (IEEE 1149.1) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé čüąĖąĮčģčĆąŠąĮąĮčāčÄ ą╝ą░čłąĖąĮčā čüąŠčüč鹊čÅąĮąĖą╣, ą▓ ą║ąŠč鹊čĆąŠą╣ 16 čüąŠčüč鹊čÅąĮąĖą╣, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 1.1.

ąĀąĖčü. 1.1. IEEE 1149.1 (JTAG) state machine.

ąÜ čüčģąĄą╝ąĄ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ TAP (čüąŠą║čĆą░čēąĄąĮąĖąĄ ąŠčé Test Access Port, ą┐ąŠčĆčé ą┤ąŠčüčéčāą┐ą░ ą║ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÄ) čüąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝ąĖ, ąŠą▒čÅąĘą░č鹥ą╗čīąĮčŗą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░: Test Clock (TCK) - ą▓čģąŠą┤ ą┤ą╗čÅ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĄ čéą░ą║č鹊ą▓ ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣, Test Mode Select (TMS) - ą▓čģąŠą┤, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą┤ą╗čÅ ąĮą░ą▓ąĖą│ą░čåąĖąĖ ą┐ąŠ čüąŠčüč鹊čÅąĮąĖčÅą╝ ą╝ą░čłąĖąĮčŗ, Test Data In (TDI) - ą▓čģąŠą┤, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą┐ąŠčüčéčāą┐ą░čÄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖą╗ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖ Test Data Out (TDO) - ą▓čŗčģąŠą┤, čüąŠą┤ąĄčƹȹ░čēąĖą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖą╗ąĖ ąĖąĮčüčéčĆčāą║čåąĖąĖ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ TAP ą╝ąŠąČąĄčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčéčī ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╣ (ąĮąĄ ąŠą▒čÅąĘą░č鹥ą╗čīąĮčŗą╣) ą┐čÅčéčŗą╣ čüąĖą│ąĮą░ą╗ Test Reset (TRST#) - čŹč鹊 ą▓čģąŠą┤, ąĮą░ ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą┤ą░ąĄčéčüčÅ ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ čüą▒čĆąŠčü (ąĖą╝ą┐čāą╗čīčüąŠą╝ ą╗ąŠą│. 0), ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą╝ą░čłąĖąĮčā ą▓ čüąŠčüč鹊čÅąĮąĖąĄ Test-Logic-Reset. ąÆą░ąČąĮąŠ ąĘą░ą╝ąĄčéąĖčéčī, čćč鹊 ą┤ą░ąČąĄ ą▒ąĄąĘ čüąĖą│ąĮą░ą╗ą░ TRST# ą╝ą░čłąĖąĮčā čüąŠčüč鹊čÅąĮąĖą╣ ą▓čüąĄą│ą┤ą░ ą╝ąŠąČąĮąŠ ą┐ąĄčĆąĄą▓ąĄčüčéąĖ ą▓ Test-Logic-Reset ąĖąĘ ą╗čÄą▒ąŠą│ąŠ ą┤čĆčāą│ąŠą│ąŠ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čāč鹥ą╝ čāą┤ąĄčƹȹĖą▓ą░ąĮąĖčÅ TMS ą▓ ą╗ąŠą│. 1 ą┤ą╗čÅ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĖąĘ 5 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓.

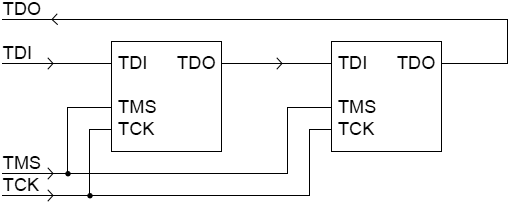

ąĀąĖčü. 1.2. ą”ąĄą┐ąŠčćą║ą░ TAP IEEE 1149.1 (JTAG).

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 1.2, čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ čåąĄą┐ąŠčćą║ąĄ JTAG ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēąĖąĄ čüąĖą│ąĮą░ą╗čŗ TCK ąĖ TMS. ąŁč鹊 ą┐čĆąĖąĮčāą┤ąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą╝ą░čłąĖąĮčŗ čüąŠčüč鹊čÅąĮąĖą╣ ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ ą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ. ą£ą░čüč鹥čĆ-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ JTAG ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé čüą▓ąŠą╣ ą▓čŗčģąŠą┤ ą┤ą░ąĮąĮčŗčģ ą║ čüąĖą│ąĮą░ą╗čā TDI. ąÜą░ąČą┤ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čåąĄą┐ąŠčćą║ąĄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé čüą▓ąŠą╣ ą▓čģąŠą┤ TDI ą║ čüąĖą│ąĮą░ą╗čā TDO ą┐čĆąĄą┤čŗą┤čāčēąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąś ąĮą░ą║ąŠąĮąĄčå, ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čåąĄą┐ąŠčćą║ąĄ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé čüą▓ąŠą╣ ą▓čŗčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ TDO ą║ąŠ ą▓čģąŠą┤čā ą┤ą░ąĮąĮčŗčģ ą╝ą░čüč鹥čĆ-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąóą░ą║ąČąĄ ą▓ąŠąĘą╝ąŠąČąĮčŗ ąĖ ą┤čĆčāą│ąĖąĄ čüčģąĄą╝čŗ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ, čćč鹊 ą▓čŗčģąŠą┤ąĖčé ąĘą░ čĆą░ą╝ą║ąĖ čĆą░čüčüą╝ąŠčéčĆąĄąĮąĖčÅ čŹč鹊ą│ąŠ ą░ą┐ąĮąŠčāčéą░.

IEEE 1149.1 ąĖą┤ąĄąĮčéąĖčäąĖčåąĖčĆčāąĄčé ą┐ąĄčĆąĄčģąŠą┤čŗ ą╝ąĄąČą┤čā čüąŠčüč鹊čÅąĮąĖčÅą╝ąĖ ą┐ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ TMS ą▓ ą╝ąŠą╝ąĄąĮčéčŗ čäčĆąŠąĮčéą░ čüąĖą│ąĮą░ą╗ą░ čéą░ą║č鹊ą▓ TCK. ąŚą░ą│čĆčāąĘą║ą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĖ ą┤ą░ąĮąĮčŗčģ ą▓ TAP, ą║ą░ą║ ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą▓ą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ ą▓ TDI ąĖ ą▓čŗą▓ąŠą┤ ąĖąĘ TDO, ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąŠ čäčĆąŠąĮčéčā ąĮą░čĆą░čüčéą░ąĮąĖčÅ čāčĆąŠą▓ąĮčÅ ąĮą░ čüąĖą│ąĮą░ą╗ąĄ čéą░ą║č鹊ą▓ TCK. ąĪą┐ą░ą┤ čāčĆąŠą▓ąĮčÅ TCK ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąĘą░čēąĄą╗ą║ąĖą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąŠčéą▓ąĄč鹊ą▓ ą▓ ą┤ąŠčüčéčāą┐ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čāčüčéčĆąŠą╣čüčéą▓ą░ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ. ąĀąĄą│ąĖčüčéčĆčŗ ą▓ ą║ą░ąČą┤ąŠą╝ JTAG TAP ąĖą╝ąĄčÄčé čĆą░ąĘąĮčāčÄ čłąĖčĆąĖąĮčā. ąÆą░ąČąĮąŠ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čāčĆąŠą▓ąĄąĮčī TMS, ą┐ąŠą║ą░ ą┤ą░ąĮąĮčŗąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆčŗ ąĖ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĖąĘ ąĮąĖčģ.

SN74BCT8244A čüąŠą┤ąĄčƹȹĖčé čüą╗ąĄą┤čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ JTAG TAP:

ąóą░ą▒ą╗ąĖčåą░ 1.1. ąĀąĄą│ąĖčüčéčĆčŗ JTAG TAP ą▒čāč乥čĆą░ SN74BCT8244.

| ąĀąĄą│ąĖčüčéčĆ |

ąĀą░ąĘą╝ąĄčĆ |

| Instruction |

8 ą▒ąĖčé |

| Boundary-Scan |

18 ą▒ąĖčé |

| Boundary-Scan Control |

2 ą▒ąĖčéą░ |

| Bypass |

1 ą▒ąĖčé |

ąĢčüą╗ąĖ ą▓ čåąĄą┐ąŠčćą║ąĄ TAP ąĖą╝ąĄąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ čāčüčéčĆąŠą╣čüčéą▓, č鹊 ą║ą░ąČą┤čŗą╣ čéąĖą┐ čĆąĄą│ąĖčüčéčĆą░ ą▓ ąĮąĖčģ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘąĮąŠą╣ ą┤ą╗ąĖąĮčŗ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░. ąŁč鹊 ą┤ąŠą╗ąČąĮą░ čāčćąĖčéčŗą▓ą░čéčī čāą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą╝ą░čüč鹥čĆą░ JTAG. ąÆčüąĄą│ąŠ ąĄčüčéčī 6 čüąŠčüč鹊čÅąĮąĖą╣ ą┐ąŠ ą▓čüąĄą╣ ą┤ąĖą░ą│čĆą░ą╝ą╝ąĄ čüąŠčüč鹊čÅąĮąĖą╣ JTAG, ą║ąŠč鹊čĆčŗąĄ čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮčŗ, čćč鹊ą▒čŗ čüąĮą░ą▒ą┤ąĖčéčī čĆą░ąĘą╗ąĖčćąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čĆą░ąĘąĮčŗą╝ąĖ ą┤ą╗ąĖąĮą░ą╝ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓. ąĪąŠą│ą╗ą░čüąĮąŠ čĆąĖčü. 1.1 čŹč鹊 čüąŠčüč鹊čÅąĮąĖčÅ Test-Logic-Reset, Run-Test-Idle, Shift-DR, Pause-DR, Shift-IR ąĖ Pause-IR. ąŻą┤ąĄčƹȹ░ąĮąĖąĄ TMS ą▓ ą┐ąŠą┤čģąŠą┤čÅčēąĄą╝ čāčĆąŠą▓ąĮąĄ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą╝ą░čłąĖąĮčā ą▓ ąĮčāąČąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ, ą┐ąŠą║ą░ čéčĆąĄą▒čāąĄą╝čŗąĄ ą▒ąĖčéčŗ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ąŠ ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ ą▓čüąĄčģ čāčüčéčĆąŠą╣čüčéą▓ čåąĄą┐ąŠčćą║ąĖ TAP.

[ą¤čĆąĖą╝ąĄčĆ čüčģąĄą╝čŗ JTAG]

ąŚą┤ąĄčüčī ą┐ąŠą║ą░ąĘą░ąĮą░ ą┐čĆąŠčüčéą░čÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ SN74BCT8244A čü ą▒ą╗ąŠą║ąŠą╝ JTAG TAP ą║ąŠą╝ą┐ą░ąĮąĖąĖ Texas Instruments (www.ti.com). ąŁč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ čüąŠą┤ąĄčƹȹĖčé 8-ą▒ąĖčéąĮčŗą╣ ą▒čāč乥čĆ čü ą┤ą▓čāą╝čÅ ą▓čŗą▓ąŠą┤ą░ą╝ąĖ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖ JTAG TAP ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ą╝ąĄč鹊ą┤čā ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ. ąöą╗čÅ čŹč鹊ą│ąŠ ą┐čĆąĖą╝ąĄčĆą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ FT2232H Mini Module, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą┐ąŠ čüčģąĄą╝ąĄ ąĮą░ čĆąĖčü. 2.1. ą¤ąŠą┤čĆąŠą▒ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ ą┐čĆąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ USB ąĖ ą┐ąĖčéą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ ąĮą░ą╣čéąĖ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čā FT2232H [2], ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą┐ą╗ą░čéčā FT2232H Mini-Module ąĖą╗ąĖ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą╝ąŠą┤čāą╗čī DLP-USB1232H. ąóą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┐ą╗ą░čéčā FT2232H Board [4].

ąĀąĖčü. 2.1. ą¤čĆąĖą╝ąĄčĆ č鹥čüč鹊ą▓ąŠą╣ čüčģąĄą╝čŗ, ą│ą┤ąĄ ą┤ą╗čÅ JTAG ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ FT2232H.

ą¤čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ MPSSE č湥čéčŗčĆąĄ ą▓čŗą▓ąŠą┤ą░ FT2232H ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĮąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░. ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čüą░ą╝ąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝ąĄ FT2232H, ą▓ čéą░ą▒ą╗ąĖčåąĄ ąĮąĖąČąĄ ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čŗą▓ąŠą┤čŗ ą┤ą▓čāčģ ą╝ąŠą┤čāą╗ąĄą╣, ą│ą┤ąĄ ą┐čĆąĖą╝ąĄąĮąĄąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ FT2232H.

ąóą░ą▒ą╗ąĖčåą░ 2.1. ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ FT2232H ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ JTAG.

| ążčāąĮą║čåąĖčÅ JTAG |

FT2232H, Port A, ąĮąŠą╝ąĄčĆ ą▓čŗą▓ąŠą┤ą░ |

FT2232H Mini Module, ąĮąŠą╝ąĄčĆ ą▓čŗą▓ąŠą┤ą░ |

DLP-USB1232H, ąĮąŠą╝ąĄčĆ ą▓čŗą▓ąŠą┤ą░ |

| TCK (ą▓čŗčģąŠą┤) |

16 (ADBUS0) |

CN2-7 (ADBUS0) |

18 (ADBUS0) |

| TDI (ą▓čŗčģąŠą┤) |

17 (ADBUS1) |

CN2-10 (ADBUS1) |

16 (ADBUS1) |

| TDO (ą▓čģąŠą┤) |

18 (ADBUS2) |

CN2-9 (ADBUS2) |

2 (ADBUS2) |

| TMS (ą▓čŗčģąŠą┤) |

19 (ADBUS3) |

CN2-12 (ADBUS3) |

5 (ADBUS3) |

ąśą╝ąĄąĮą░ TDI ąĖ TDO ą┤ą╗čÅ ą╝ą░čüč鹥čĆ-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą▓čŗą│ą╗čÅą┤čÅčé, ą║ą░ą║ ąĮąĄ ą┐ąŠą┤čģąŠą┤čÅčēąĖąĄ ąĄą│ąŠ ą▓čģąŠą┤čā ąĖ ą▓čŗčģąŠą┤čā; ąŠą┤ąĮą░ą║ąŠ, čŹč鹊 ą║ąŠčĆčĆąĄą║čéąĮčŗąĄ ąĖą╝ąĄąĮą░ čüąĖą│ąĮą░ą╗ąŠą▓, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▓čģąŠą┤čā ąĖ ą▓čŗčģąŠą┤čā JTAG TAP. ąÆčģąŠą┤ąĮčŗąĄ ą▓čŗą▓ąŠą┤čŗ SN74BCT8244A ą▓ąĮčāčéčĆąĖ čŹč鹊ą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ąŠą┤čéčÅąĮčāčéčŗ ą║ ą╗ąŠą│. 1. ąöą╗čÅ čŹč鹊ą╣ čüčģąĄą╝čŗ ą┐čĆąĖą╝ąĄčĆą░ ąŠąĮąĖ ąŠčüčéą░čÄčéčüčÅ ąĮąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ąĖ, čćč鹊 čäąĖą║čüąĖčĆčāąĄčé ą▓čģąŠą┤ąĮąŠą╣ čāčĆąŠą▓ąĄąĮčī ą║ą░ą║ ą╗ąŠą│. 1, ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ąĖčé ą▓čŗčģąŠą┤čŗ ą▓ čéčĆąĄčéčīąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ąöą╗čÅ čŹč鹊ą│ąŠ ą░ą┐ąĮąŠčāčéą░ ą║ SN74BCT8244A ą┐ąŠą┤ą║ą╗čÄč湥ąĮ Port A ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FT2232H. ąĪ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ FT2232H ąĖ FT4232H ą▓ą╝ąĄčüč鹊 Port A ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ Port B. ąĪąŠą▓ą╝ąĄčüčéąĮąŠ čü ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖąĄą╣ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗą▓ąŠą┤ąŠą▓ Port B, čāą┐čĆą░ą▓ą╗čÅčÄčēą░čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ (čüą╝. ąĮąĖąČąĄ) čéą░ą║ąČąĄ ą┐ąŠčéčĆąĄą▒čāąĄčé ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÄ, čćč鹊ą▒čŗ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ą╗čüčÅ ą▒ą╗ąŠą║ MPSSE ą┐ąŠčĆčéą░ B.

ąĪąĖą│ąĮą░ą╗ TRST# ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčéčüčÅ ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ SN74BCT8244A; ąŠą┤ąĮą░ą║ąŠ ąŠąĮ čéčĆąĄą▒čāąĄčé ą▓čģąŠą┤ąĮąŠą│ąŠ čāčĆąŠą▓ąĮčÅ 10V ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TMS. ąöą╗čÅ čāą┐čĆąŠčēąĄąĮąĖčÅ čüčģąĄą╝čŗ ą▓ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ TRST# ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ TAP čüąŠ čüčéą░ąĮą┤ą░čĆčéąĮčŗą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ I/O ą┤ą╗čÅ čŹč鹊ą╣ čäčāąĮą║čåąĖąĖ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┤ąĖąĮ ąĖąĘ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĮčŗčģ ą▓čŗą▓ąŠą┤ąŠą▓ GPIO ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FT2232H.

FT2232H čéčĆąĄą▒čāąĄčé VCCIO = 3.3V, čģąŠčéčÅ ąĄčæ ą▓čģąŠą┤čŗ ą┤ąŠą┐čāčüą║ą░čÄčé čāčĆąŠą▓ąĮąĖ ą╗ąŠą│ąĖą║ąĖ 5V (5V tolerant). ą¤ąŠčŹč鹊ą╝čā ą┤ąŠą┐čāčüčéąĖą╝ąŠ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī FT2232H ą║ SN74BCT8244A, ą║ąŠč鹊čĆą░čÅ ą┐ąŠą╗čāčćą░ąĄčé ą┐ąĖčéą░ąĮąĖąĄ 5V. ąśąĘčāč湥ąĮąĖąĄ ąŠą▒ąŠąĖčģ ą┤ą░čéą░čłąĖč鹊ą▓ ąĮą░ čŹčéąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąŠčĆąŠą│ąĖ čāčĆąŠą▓ąĮąĄą╣ ą╗ąŠą│. 1 ąĖ ą╗ąŠą│. 0 čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆčÅčÄčéčüčÅ, ą║ą░ą║ ąĖ ąĮąĄ ą▒čāą┤čāčé ą┐čĆąĄą▓čŗčłąĄąĮčŗ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ.

[ą¤čĆąĖą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ JTAG ąĮą░ FT2232H]

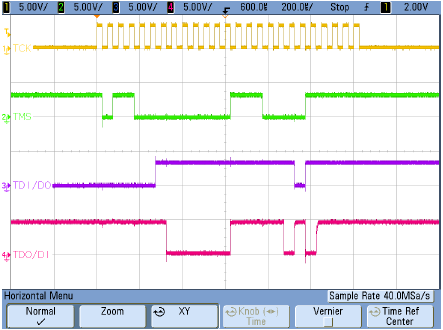

ąÆ čŹč鹊ą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ą▓ 2 čĆą░ąĘą░ čāą▓ąĄą╗ąĖč湥ąĮčŗ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▓čĆąĄą╝ąĄąĮąĖ, ą║ąŠč鹊čĆčŗąĄ ą▒čŗą╗ąĖ ą┤ą░ąĮčŗ ą▓ ą┐čĆąĖą╝ąĄčĆąĄ ąĮą░ čüčéčĆą░ąĮąĖčåąĄ Page 14 ą┤ą░čéą░čłąĖčéą░ Texas Instruments ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝čā SN74BCT8244A, ąĖ ąĮą░ą▒ą╗čÄą┤ą░ą╗ąĖčüčī ą┐ąŠą╗čāč湥ąĮąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ. ąŁč鹊čé ą┐čĆąĖą╝ąĄčĆ čüąŠčüč鹊ąĖčé ąĖąĘ 25 čéą░ą║č鹊ą▓ TCK. ąæčŗą╗ąĖ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮčŗ ą▓čüąĄ čüąŠčüč鹊čÅąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ JTAG TAP, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ Pause-IR, Exit2-IR, Pause-DR ąĖ Exit2-DR. ąŁčéąĖ ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čüąŠčüč鹊čÅąĮąĖčÅ ąŠą▒čŗčćąĮąŠ ąĮčāąČąĮčŗ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ čāčüčéčĆąŠą╣čüčéą▓ąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą▒ąŠą╗ąĄąĄ ą┤ą╗ąĖąĮąĮąŠą╣ čåąĄą┐ąŠčćą║ąĄ JTAG, ąĖą╗ąĖ ą║ąŠą│ą┤ą░ ąĖą╝ąĄčÄčéčüčÅ ąŠč湥ąĮčī ą┤ą╗ąĖąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ą┐ąŠą│čĆą░ąĮąĖčćąĮąŠą│ąŠ čüą║ą░ąĮąĖčĆąŠą▓ą░ąĮąĖčÅ.

ą¤čĆąĖą╝ąĄčĆ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╣ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤čĆą░ą╣ą▓ąĄčĆ čāčüčéčĆąŠą╣čüčéą▓ą░ FTDI D2XX. ą×ąĮą░ ąĮą░ą┐ąĖčüą░ąĮą░ ą▓ ą╗ąĖąĮąĄą╣ąĮąŠą╝ čüčéąĖą╗ąĄ, čćč鹊ą▒čŗ ą┐čĆąŠą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆąŠą▓ą░čéčī čĆąĄą░ą╗čīąĮčŗąĄ ą▒ą░ą╣čéčŗ, ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ ą▓ ą▒ą╗ąŠą║ MPSSE, ąĖ čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ąĖąĘ MPSSE. ąŚą┤ąĄčüčī čüąĄą║čåąĖąĖ, ą║ąŠč鹊čĆčŗąĄ čćąĖčéą░čÄčé ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčé ą▓čŗą▓ąŠą┤čŗ ą┤ą░ąĮąĮčŗčģ (TDI ąĖ TDO), ą┤ąŠą╗ąČąĮčŗ ą║ąŠą╝ą▒ąĖąĮąĖčĆąŠą▓ą░čéčīčüčÅ čü ą╝ą░ąĮąĖą┐čāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ą▓čŗą▓ąŠą┤ąŠą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (TMS), čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖą╣. ąĀąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĖąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠą╗ąČąĮčŗ čéčēą░č鹥ą╗čīąĮąŠ ąĮą░ą▒ą╗čÄą┤ą░čéčīčüčÅ, ąĖ ąĮą░ ąĮąĖčģ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ čĆąĄą░ą║čåąĖčÅ. ąÆąŠąĘą╝ąŠąČąĮąŠ, čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą╝ąŠą│čāčé ą┐ąŠčéčĆąĄą▒ąŠą▓ą░čéčī čéą░ą║ąŠą│ąŠ čüą┤ą▓ąĖą│ą░, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī č乊čĆą╝ą░čé, ą║ąŠč鹊čĆčŗą╣ ą▒ąŠą╗ąĄąĄ čāą┤ąŠą▒ąĄąĮ ą┤ą╗čÅ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčüčéą░.

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ą┤čāą▒ą╗ąĖčĆąŠą▓ą░ąĮąĖčÄ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĖą╝ąĄčĆą░, ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗąĄ (Hi-Speed) ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ FTDI (FT2232H ąĖ FT4232H) ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ TCK ą▒ąĄąĘ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ą║ąĖčģ-ą╗ąĖą▒ąŠ ą┤ą░ąĮąĮčŗčģ ąĮą░ ąĖčģ ą▓čŗčģąŠą┤ ąĖąĘ MPSSE. ąŁč鹊 ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāąĄčéčüčÅ ą▓ ą║ąŠąĮčåąĄ ą╗ąĖčüčéąĖąĮą│ą░ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ą¤ąŠčüą╗ąĄ ą╗ąĖčüčéąĖąĮą│ą░ ą║ąŠą┤ą░ ą┐ąŠą║ą░ąĘą░ąĮčŗ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝čŗ ąŠąČąĖą┤ą░ąĄą╝ąŠą│ąŠ ą▓ąĖą┤ą░ ąĖ čü ąŠąČąĖą┤ą░ąĄą╝čŗą╝ąĖ ąĖąĮč鹥čĆą▓ą░ą╗ą░ą╝ąĖ ą▓čĆąĄą╝ąĄąĮąĖ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: FT2232H ąĖ FT4232H čéčĆąĄą▒čāčÄčé ą┤čĆą░ą╣ą▓ąĄčĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ąĄčĆčüąĖąĖ 2.06.00 ąĖą╗ąĖ ą▒ąŠą╗ąĄąĄ čüą▓ąĄąČąĄą╣. FT232H čéčĆąĄą▒čāąĄčé ą┤čĆą░ą╣ą▓ąĄčĆą░ čāčüčéčĆąŠą╣čüčéą▓ą░ ą▓ąĄčĆčüąĖąĖ 2.08.14 ąĖą╗ąĖ ą▒ąŠą╗ąĄąĄ čüą▓ąĄąČąĄą╣. ą×ą▒čŗčćąĮąŠ čģąŠčĆąŠčłąĄą╣ ąĖą┤ąĄąĄą╣ ą▒čāą┤ąĄčé ąĘą░ą│čĆčāąĘąĖčéčī čü čüą░ą╣čéą░ FTDI ą┐ąŠčüą╗ąĄą┤ąĮčÄčÄ ą▓ąĄčĆčüąĖčÄ ą┤čĆą░ą╣ą▓ąĄčĆą░ ą┤ą╗čÅ ą▓čüąĄčģ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ FTDI.

ą¤čĆąĖą╝ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĮą░ą┐ąĖčüą░ąĮ ąĮą░ C++, ąĖ ą▒čŗą╗ čüą║ąŠą╝ą┐ąĖą╗ąĖčĆąŠą▓ą░ąĮ ą▓ ą║ąŠąĮčüąŠą╗čīąĮąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ ą▓ čüčĆąĄą┤ąĄ Microsoft┬« Visual Studio 2008.

// AN_129_Hi-Speed_JTAG_with_MPSSE.cpp []: ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé č鹊čćą║čā ą▓čģąŠą┤ą░

// ą▓ ą║ąŠąĮčüąŠą╗čīąĮąŠąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĄ.

#include "stdafx.h"

#include < windows.h >

#include < stdio.h >

#include "ftd2xx.h"

int _tmain(int argc, _TCHAR* argv[])

{

FT_HANDLE ftHandle; // čģąĄąĮą┤ą╗ ą┤ą╗čÅ čāčüčéčĆąŠą╣čüčéą▓ą░ FTDI

FT_STATUS ftStatus; // čĆąĄąĘčāą╗čīčéą░čé ą║ą░ąČą┤ąŠą│ąŠ ą▓čŗąĘąŠą▓ą░ D2XX

DWORD dwNumDevs; // ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čāčüčéčĆąŠą╣čüčéą▓

unsigned int uiDevIndex = 0xF; // čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▓ čüą┐ąĖčüą║ąĄ, ą║ąŠč鹊čĆąŠąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ

BYTE byOutputBuffer[1024]; // ą▒čāč乥čĆ, ą║ąŠč鹊čĆčŗą╣ čüąŠą┤ąĄčƹȹĖčé ą║ąŠą╝ą░ąĮą┤čŗ MPSSE, ąĖ ą┤ą░ąĮąĮčŗąĄ

// ą┤ą╗čÅ ąŠčéą┐čĆą░ą▓ą║ąĖ ą▓ FT2232H

BYTE byInputBuffer[1024]; // ą▒čāč乥čĆ ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ, ą┐čĆąŠčćąĖčéą░ąĮąĮčŗčģ ąĖąĘ FT2232H

DWORD dwCount = 0; // ą│ą╗ą░ą▓ąĮčŗą╣ ąĖąĮą┤ąĄą║čü čåąĖą║ą╗ą░

DWORD dwNumBytesToSend = 0; // ąĖąĮą┤ąĄą║čü ą▓čŗčģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░

DWORD dwNumBytesSent = 0; // čüč湥čéčćąĖą║ čĆąĄą░ą╗čīąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąĮčŗčģ ą▒ą░ą╣čé -

// ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ FT_Write

DWORD dwNumBytesToRead = 0; // ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé, ą┤ąŠčüčéčāą┐ąĮčŗčģ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╝

// ą▒čāč乥čĆąĄ ą┤čĆą░ą╣ą▓ąĄčĆą░

DWORD dwNumBytesRead = 0; // ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čĆąĄą░ą╗čīąĮąŠ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ -

// ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ FT_Read

DWORD dwClockDivisor = 0x05DB; // ąĘąĮą░č湥ąĮąĖąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓, čćą░čüč鹊čéą░ SCL =

// 60/((1+0x05DB)*2) (ą£ąōčå) = 20 ą║ąōčå

// ą¤čĆąŠą▓ąĄčĆą║ą░ - ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ą╗ąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ FTDI?

printf("Checking for FTDI devices...\n");

ftStatus = FT_CreateDeviceInfoList(&dwNumDevs);

// ą¤ąŠą╗čāč湥ąĮąĖąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čāčüčéčĆąŠą╣čüčéą▓ FTDI

if (ftStatus != FT_OK) // ą║ąŠą╝ą░ąĮą┤ą░ ą▓čŗą┐ąŠą╗ąĮąĖą╗ą░čüčī čāčüą┐ąĄčłąĮąŠ?

{

printf("Error in getting the number of devices\n");

return 1; // ąÆčŗčģąŠą┤ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ

}

if (dwNumDevs < 1) // ąÆčŗčģąŠą┤, ąĄčüą╗ąĖ ąĮąĄ ą▓ąĖą┤ąĖčéčüčÅ ąĮąĖ ąŠą┤ąĮąŠ čāčüčéčĆąŠą╣čüčéą▓ąŠ

{

printf("There are no FTDI devices installed\n");

return 1; // ąÆčŗčģąŠą┤ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ

}

printf("%d FTDI devices found - count includes individual ports on a single chip\n",

dwNumDevs);

// ą×čéą║čĆčŗčéąĖąĄ ą┐ąŠčĆčéą░ - čćč鹊ą▒čŗ čāą┐čĆąŠčüčéąĖčéčī ą║ąŠą┤, ą┤ą╗čÅ čŹč鹊ą│ąŠ ą░ą┐ąĮąŠčāčéą░ ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░ąĄčéčüčÅ, čćč鹊

// ą┐ąĄčĆą▓ąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą▒čāą┤ąĄčé ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ FT2232H ąĖą╗ąĖ FT4232H. ąæąŠą╗ąĄąĄ čéčēą░č鹥ą╗čīąĮčŗąĄ

// ą┐čĆąŠą▓ąĄčĆą║ąĖ ą┐ąĄčĆąĄą┤ ąŠčéą║čĆčŗčéąĖąĄą╝ ą┐ąŠčĆčéą░ ą╝ąŠą│čāčé ą▒čŗčéčī čüą┤ąĄą╗ą░ąĮčŗ ąĮą░ ąŠčüąĮąŠą▓ąĄ čćč鹥ąĮąĖčÅ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓

// čāčüčéčĆąŠą╣čüčéą▓ą░, ą╝ąĄčüčéą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ, čüąĄčĆąĖą╣ąĮąŠą│ąŠ ąĮąŠą╝ąĄčĆą░ ąĖ čé. ą┤.

printf("\nAssume first device has the MPSSE and open it...\n");

ftStatus = FT_Open(0, &ftHandle);

if (ftStatus != FT_OK)

{

printf("Open Failed with error %d\n", ftStatus);

return 1; // ąÆčŗčģąŠą┤ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ

}

// ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┐ąŠčĆčéą░

printf("\nConfiguring port for MPSSE use...\n");

ftStatus |= FT_ResetDevice(ftHandle);

// ąĪą▒čĆąŠčü čāčüčéčĆąŠą╣čüčéą▓ą░ USB

// ąĪąĮą░čćą░ą╗ą░ ąŠčćąĖčēą░ąĄčéčüčÅ ą▒čāč乥čĆ ą┐čĆąĖąĄą╝ą░ USB, ą┤ą╗čÅ č湥ą│ąŠ čüčćąĖčéčŗą▓ą░čÄčéčüčÅ ą▓čüąĄ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ

// ąĖąĘ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ FT2232H. ą¤ąŠą╗čāč湥ąĮąĖąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé ą▓ ą▒čāč乥čĆąĄ ą┐čĆąĖąĄą╝ą░ FT2232H:

ftStatus |= FT_GetQueueStatus(ftHandle, &dwNumBytesToRead);

// ą¦č鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▒čāč乥čĆą░ ą┐čĆąĖąĄą╝ą░ FT2232H:

if ((ftStatus == FT_OK) && (dwNumBytesToRead > 0))

FT_Read(ftHandle, &byInputBuffer, dwNumBytesToRead, &dwNumBytesRead);

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆą░ąĘą╝ąĄčĆąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą┐čĆąŠčüą░ USB ą▓ 64K:

ftStatus |= FT_SetUSBParameters(ftHandle, 65536, 65535);

// ąŚą░ą┐čĆąĄčé čüąĖą╝ą▓ąŠą╗ąŠą▓ čüąŠą▒čŗčéąĖčÅ ąĖ ąŠčłąĖą▒ą║ąĖ (event, error characters):

ftStatus |= FT_SetChars(ftHandle, false, 0, false, 0);

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čéą░ą╣ą╝ą░čāčéą░ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ ą▓ ą╝ąĖą╗ą╗ąĖčüąĄą║čāąĮą┤ą░čģ:

ftStatus |= FT_SetTimeouts(ftHandle, 0, 5000);

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čéą░ą╣ą╝ąĄčĆą░ ą╗ą░č鹥ąĮčéąĮąŠčüčéąĖ (ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 16 ą╝čü):

ftStatus |= FT_SetLatencyTimer(ftHandle, 16);

// ąĪą▒čĆąŠčü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░:

ftStatus |= FT_SetBitMode(ftHandle, 0x0, 0x00);

// ąĀą░ąĘčĆąĄčłąĖčéčī čĆąĄąČąĖą╝ MPSSE:

ftStatus |= FT_SetBitMode(ftHandle, 0x0, 0x02);

if (ftStatus != FT_OK)

{

printf("Error in initializing the MPSSE %d\n", ftStatus);

FT_Close(ftHandle);

return 1; // ąÆčŗčģąŠą┤ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ

}

Sleep(50); // ąŠąČąĖą┤ą░ąĮąĖąĄ, čćč鹊ą▒čŗ ą▓čüąĄ, čüą▓čÅąĘą░ąĮąĮąŠąĄ čü USB, ąĘą░ą┐čāčüčéąĖą╗ąŠčüčī

// ąĖ ąĮą░čćą░ą╗ąŠ čĆą░ą▒ąŠčéą░čéčī

// -----------------------------------------------------------

// ąÆ čŹč鹊ą╣ č鹊čćą║ąĄ MPSSE ą│ąŠč鹊ą▓ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą║ąŠą╝ą░ąĮą┤

// -----------------------------------------------------------

// -----------------------------------------------------------

// ąĪąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ MPSSE ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠčéą┐čĆą░ą▓ą║ąŠą╣ ąĮąĄ čüčāčēąĄčüčéą▓čāčÄčēąĄą│ąŠ

// ą║ąŠą┤ą░ ąŠą┐ąĄčĆą░čåąĖąĖ (0xAA), ąĮą░ čćč鹊 MPSSE ąŠčéą▓ąĄčéąĖčéčī ą║ąŠą┤ąŠą╝ "Bad

// Command" (0xFA, ąŠčłąĖą▒ąŠčćąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░), ąĘą░ ą║ąŠč鹊čĆčŗą╝ ą▒čāą┤ąĄčé ąĖą┤čéąĖ

// čüą░ą╝ą░ čŹčéą░ ąŠčłąĖą▒ąŠčćąĮą░čÅ ą║ąŠą╝ą░ąĮą┤ą░ (0xAA).

// -----------------------------------------------------------

// ąöąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ ą║ ąŠč湥čĆąĄą┤ąĖ ąŠčłąĖą▒ąŠčćąĮąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ xAA:

byOutputBuffer[dwNumBytesToSend++] = 0xAA; //'\xAA';

// ą×čéą┐čĆą░ą▓ą║ą░ ą┐ą╗ąŠčģąŠą╣ ą║ąŠą╝ą░ąĮą┤čŗ:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

do

{

// ą¤ąŠą╗čāč湥ąĮąĖąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╝ ą▒čāč乥čĆąĄ čāčüčéčĆąŠą╣čüčéą▓ą░:

ftStatus = FT_GetQueueStatus(ftHandle, &dwNumBytesToRead);

} while ((dwNumBytesToRead == 0) && (ftStatus == FT_OK));

// ą”ąĖą║ą╗ ąĘą░ą▓ąĄčĆčłąĖčéčüčÅ, ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ą░ ąŠčłąĖą▒ą║ą░, ąĖą╗ąĖ ą┐ąŠ čéą░ą╣ą╝ą░čāčéčā

bool bCommandEchod = false;

// ą¦č鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░:

ftStatus = FT_Read(ftHandle, &byInputBuffer, dwNumBytesToRead, &dwNumBytesRead);

// ą¤čĆąŠą▓ąĄčĆą║ą░: ą▒čŗą╗ ą╗ąĖ ą┐ąŠą╗čāč湥ąĮ ąŠčéą▓ąĄčé "Bad command" ąĖ čŹčģąŠ ą║ąŠą╝ą░ąĮą┤čŗ:

for (dwCount = 0; dwCount < dwNumBytesRead - 1; dwCount++)

{

if ((byInputBuffer[dwCount] == 0xFA) && (byInputBuffer[dwCount+1] == 0xAA))

{

bCommandEchod = true;

break;

}

}

if (bCommandEchod == false)

{

printf("Error in synchronizing the MPSSE\n");

FT_Close(ftHandle);

return 1; // ąÆčŗčģąŠą┤ ą┐ąŠ ąŠčłąĖą▒ą║ąĄ

}

// -----------------------------------------------------------

// ąÜąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮą░čüčéčĆąŠąĄą║ MPSSE ą┤ą╗čÅ JTAG. ąÆ ą▒ą╗ąŠą║ MPSSE

// ą╝ąŠąČąĮąŠ ą┐ąŠčüą╗ą░čéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą║ąŠą╝ą░ąĮą┤ ąŠą┤ąĮąĖą╝ ą▓čŗąĘąŠą▓ąŠą╝ FT_Write.

// -----------------------------------------------------------

dwNumBytesToSend = 0; // ąĮą░čćą░ą╗ąŠ čü čćąĖčüč鹊ą│ąŠ ąĖąĮą┤ąĄą║čüą░

// ąØą░čüčéčĆąŠą╣ą║ą░ ą║ąŠą╝ą░ąĮą┤, ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ Hi-Speed ą┤ą╗čÅ FTx232H.

// ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą│ą╗ą░ą▓ąĮąŠą╣ čćą░čüč鹊čéčŗ 60 ą£ąōčå (ąĘą░ą┐čĆąĄčé ą┤ąĄą╗ąĖč鹥ą╗čÅ ąĮą░ 5):

byOutputBuffer[dwNumBytesToSend++] = 0x8A;

// ąÆčŗą║ą╗čÄč湥ąĮąĖąĄ ą░ą┤ą░ą┐čéąĖą▓ąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (ąŠąĮąŠ ą╝ąŠąČąĄčé čéčĆąĄą▒ąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ARM):

byOutputBuffer[dwNumBytesToSend++] = 0x97;

// ąŚą░ą┐čĆąĄčé čéčĆąĄčģčäą░ąĘąĮąŠą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ:

byOutputBuffer[dwNumBytesToSend++] = 0x8D;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤, ąŠčéąĮąŠčüčÅčēąĖčģčüčÅ ą║ Hi-Speed:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąŻčüčéą░ąĮąŠą▓ą║ą░ ąĮą░čćą░ą╗čīąĮčŗčģ čüąŠčüč鹊čÅąĮąĖą╣ ąĖąĮč鹥čĆč乥ą╣čüą░ MPSSE - ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, ąŠą▒ą░ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ

// ąĮąŠąČąĄą║ ąĖ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ.

// ąśą╝čÅ ą▓čŗą▓ąŠą┤ą░ ąĪąĖą│ąĮą░ą╗ ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąØą░čć. čüąŠčüč鹊čÅąĮąĖąĄ ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ

// ADBUS0 TCK output 1 ą╗ąŠą│. 0 0

// ADBUS1 TDI output 1 ą╗ąŠą│. 0 0

// ADBUS2 TDO input 0 0

// ADBUS3 TMS output 1 ą╗ąŠą│. 1 1

// ADBUS4 GPIOL0 input 0 0

// ADBUS5 GPIOL1 input 0 0

// ADBUS6 GPIOL2 input 0 0

// ADBUS7 GPIOL3 input 0 0

// ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čéą░ ą┐ąŠčĆčéą░ MPSSE:

byOutputBuffer[dwNumBytesToSend++] = 0x80;

// ąØą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓ ą▓čŗčłąĄčāą║ą░ąĘą░ąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ:

byOutputBuffer[dwNumBytesToSend++] = 0x08;

// ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ąŠą▓, ą║ą░ą║ ą▓ ą▓čŗčłąĄčāą║ą░ąĘą░ąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ:

byOutputBuffer[dwNumBytesToSend++] = 0x0B;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┤ą╗čÅ ą╝ą╗ą░ą┤čłąĄą│ąŠ GPIO:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąŻčüčéą░ąĮąŠą▓ą║ą░ ąĮą░čćą░ą╗čīąĮčŗčģ čüąŠčüč鹊čÅąĮąĖą╣ ąĖąĮč鹥čĆč乥ą╣čüą░ MPSSE - ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé, ąŠą▒ą░ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ

// ąĮąŠąČąĄą║ ąĖ ą▓čŗčģąŠą┤ąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ.

// ąśą╝čÅ ą▓čŗą▓ąŠą┤ą░ ąĪąĖą│ąĮą░ą╗ ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ ąØą░čć. čüąŠčüč鹊čÅąĮąĖąĄ ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ

// ACBUS0 GPIOH0 input 0 0

// ACBUS1 GPIOH1 input 0 0

// ACBUS2 GPIOH2 input 0 0

// ACBUS3 GPIOH3 input 0 0

// ACBUS4 GPIOH4 input 0 0

// ACBUS5 GPIOH5 input 0 0

// ACBUS6 GPIOH6 input 0 0

// ACBUS7 GPIOH7 input 0 0

// ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčé ą┤ą░ąĮąĮčŗčģ ą╝ą╗ą░ą┤čłąĄą│ąŠ ą▒ą░ą╣čéą░ ą┐ąŠčĆčéą░ MPSSE:

byOutputBuffer[dwNumBytesToSend++] = 0x82;

// ąØą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą▓ ą▓čŗčłąĄčāą║ą░ąĘą░ąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ:

byOutputBuffer[dwNumBytesToSend++] = 0x00;

// ąØą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čĆą░ą▒ąŠčéčŗ ą▓čŗą▓ąŠą┤ąŠą▓, ą║ą░ą║ ą▓ ą▓čŗčłąĄčāą║ą░ąĘą░ąĮąĮąŠą╣ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ:

byOutputBuffer[dwNumBytesToSend++] = 0x00;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą┤ą╗čÅ čüčéą░čĆčłąĄą│ąŠ GPIO:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąŻčüčéą░ąĮąŠą▓ą║ą░ čćą░čüč鹊čéčŗ TCK (0xValueH čüčéą░čĆčłąĖą╣ ą▒ą░ą╣čé ąĘąĮą░č湥ąĮąĖčÅ,

// 0xValueL ą╝ą╗ą░ą┤čłąĖą╣ ą▒ą░ą╣čé ąĘąĮą░č湥ąĮąĖčÅ):

// TCK = 60MHz /((1 + [(1 +0xValueH*256) OR 0xValueL])*2)

// ąÜąŠą╝ą░ąĮą┤ą░ ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓:

byOutputBuffer[dwNumBytesToSend++] = '\x86';

// ąŻčüčéą░ąĮąŠą▓ą║ą░ 0xValueL ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓:

byOutputBuffer[dwNumBytesToSend++] = dwClockDivisor & 0xFF;

// ąŻčüčéą░ąĮąŠą▓ą║ą░ 0xValueH ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓:

byOutputBuffer[dwNumBytesToSend++] = (dwClockDivisor >> 8) & 0xFF;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤ ą┤ą╗čÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąŚą░ą┐čĆąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą┐ąĄčéą╗ąĖ ąĘą░ą╝čŗą║ą░ąĮąĖčÅ ą▓čģąŠą┤ą░ ąĮą░ ą▓čŗčģąŠą┤ (internal loop-back,

// čŹčéą░ ą┐ąĄčéą╗čÅ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ čüą░ą╝ąŠą┐čĆąŠą▓ąĄčĆą║ąĖ):

byOutputBuffer[dwNumBytesToSend++] = 0x85;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ ąĘą░ą┐čĆąĄčéą░ loop-back:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąØą░ą▓ąĖą│ą░čåąĖčÅ TMS ą┐ąŠ čüąŠčüč鹊čÅąĮąĖčÅą╝ Test-Logic-Reset -> Run-Test-Idle ->

// Select-DR-Scan -> Select-IR-Scan: TMS=1 TMS=0 TMS=1 TMS=1

// ąØąĄ čćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ čüąŠčüč鹊čÅąĮąĖčÅčģ Test-Logic-Reset, Run-Test-Idle, Select-DR-Scan,

// Select-IR-Scan:

byOutputBuffer[dwNumBytesToSend++] = 0x4B;

// ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ = ą┤ą╗ąĖąĮą░ + 1 (ąĘą┤ąĄčüčī 6 čéą░ą║č鹊ą▓):

byOutputBuffer[dwNumBytesToSend++] = 0x05;

// ąöą░ąĮąĮčŗąĄ čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ (LSB) ą▓ą┐ąĄčĆąĄą┤, ą┐ąŠčŹč鹊ą╝čā ą┤ą╗čÅ TMS

// ą▒čāą┤ąĄčé čłą░ą▒ą╗ąŠąĮ 101100:

byOutputBuffer[dwNumBytesToSend++] = 0x0D;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ TMS:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąÆ ąĮą░čüč鹊čÅčēąĖą╣ TMS = ą╗ąŠą│. 0. ą£ą░čłąĖąĮą░ TAP ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ Shift-IR,

// čéą░ą║ čćč鹊 č鹥ą┐ąĄčĆčī ą▒čāą┤ąĄą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ąŠą╝ą░ąĮą┤čā TDI/TDO, čćč鹊ą▒čŗ ą▓čŗą┤ą▓ąĖąĮčāčéčī ąĄą┤ąĖąĮąĖčćą║ąĖ

// č湥čĆąĄąĘ ą▓čŗčģąŠą┤ TDI ą┐čĆąĖ čćč鹥ąĮąĖąĖ ą▓čģąŠą┤ą░ TDO. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 ąĮčāąČąĮąŠ ą▓ą┤ą▓ąĖąĮčāčéčī 8 ą▒ąĖčé,

// ąĘą┤ąĄčüčī čéą░ą║čéąĖčĆčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ 7. 8-ą╣ ą▒čāą┤ąĄčé ą▓ą┤ą▓ąĖąĮčāčé čüąŠą▓ą╝ąĄčüčéąĮąŠ čüąŠ čüą╗ąĄą┤čāčÄčēąĄą╣

// ą║ąŠą╝ą░ąĮą┤ąŠą╣ TMS. ąöą░ąĮąĮčŗąĄ čéą░ą║čéąĖčĆčāąĄą╝ ąĮą░ ą▓čŗčģąŠą┤ č湥čĆąĄąĘ čüąŠčüč鹊čÅąĮąĖčÅ Capture-IR, Shift-IR

// ąĖ Exit-IR, čćąĖčéą░čÅ ą┐čĆąĖ čŹč鹊ą╝ ą▓ąŠąĘą▓čĆą░čēą░ąĄą╝čŗą╣ čĆąĄąĘčāą╗čīčéą░čé:

byOutputBuffer[dwNumBytesToSend++] = 0x3B;

// ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ = ą┤ą╗ąĖąĮą░ + 1 (ąĘą┤ąĄčüčī 7 čéą░ą║č鹊ą▓):

byOutputBuffer[dwNumBytesToSend++] = 0x06;

// ąÆčŗą┤ą▓ąĖą│ą░ąĄą╝ 1111111 (ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ):

byOutputBuffer[dwNumBytesToSend++] = 0xFF;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ TMS:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ TMS:

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąŚą┤ąĄčüčī ą║ąŠą╝ą░ąĮą┤ą░ TMS, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ą░čÅ čü 1 čéą░ą║č鹊ą╝. ą¤čĆąĖ čŹč鹊ą╝ ą┤ą░ąĮąĮčŗąĄ čéą░ą║ąČąĄ ą▓ą┤ą▓ąĖą│ą░čÄčéčüčÅ.

// ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ TMS, čćč鹥ąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ ą▒ąĖčéą░:

byOutputBuffer[dwNumBytesToSend++] = 0x6B;

// ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ = ą┤ą╗ąĖąĮą░ + 1 (ąĘą┤ąĄčüčī 1 čéą░ą║čé):

byOutputBuffer[dwNumBytesToSend++] = 0x00;

// ąöą░ąĮąĮčŗąĄ čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤, čéą░ą║ čćč鹊 TMS čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą╗ąŠą│. 1. ąóą░ą║ąČąĄ

// ą▒ąĖčé 7 ą┐ąŠą┐ą░ą┤ą░ąĄčé ąĮą░ ą▓čŗčģąŠą┤ TDI, ąĖ čéą░ą║ąČąĄ 1 ą▒ąĖčé ą╗ąŠą│. 1 ąŠčüčéą░ą▓ąĖčé TMS ą▓ čüąŠčüč鹊čÅąĮąĖąĖ

// ą╗ąŠą│. 1 ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ ą║ąŠą╝ą░ąĮą┤:

byOutputBuffer[dwNumBytesToSend++] = 0x83;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ TMS:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąØą░ą▓ąĖą│ą░čåąĖčÅ TMS ąŠčé Exit-IR č湥čĆąĄąĘ Update-IR -> Select-DR-Scan -> Capture-DR:

// TMS=1 TMS=1 TMS=0

// ąØąĄ čćąĖčéą░ąĄą╝ ą┤ą░ąĮąĮčŗąĄ ą▓ čüąŠčüč鹊čÅąĮąĖčÅčģ Update-IR -> Select-DR-Scan -> Capture-DR

byOutputBuffer[dwNumBytesToSend++] = 0x4B;

// ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ = ą┤ą╗ąĖąĮą░ + 1 (ąĘą┤ąĄčüčī 4 čéą░ą║čéą░):

byOutputBuffer[dwNumBytesToSend++] = 0x03;

// ąöą░ąĮąĮčŗąĄ čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤, čéą░ą║ čćč鹊 ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ TMS ą▒čāą┤čāčé 110:

byOutputBuffer[dwNumBytesToSend++] = 0x83;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ TMS:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąĪąĄą╣čćą░čü TMS = ą╗ąŠą│. 0. ą£ą░čłąĖąĮą░ TAP ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ Shift-DR, čéą░ą║ čćč鹊 č鹥ą┐ąĄčĆčī

// ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ ą║ąŠą╝ą░ąĮą┤čā TDI/TDO ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ą▓čŗą┤ą▓ąĖąĮčāčéčī 101 ąĮą░ ą▓čŗčģąŠą┤ TDI, čćąĖčéą░čÅ

// ą┐čĆąĖ čŹč鹊ą╝ ą▓čģąŠą┤ TDO. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊, čćč鹊 ąĮčāąČąĮąŠ ą▓ą┤ą▓ąĖąĮčāčéčī 3 ą▒ąĖčéą░, ąĘą┤ąĄčüčī ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ

// č鹊ą╗čīą║ąŠ 2 čéą░ą║čéą░. ąóčĆąĄčéąĖą╣ ą▒čāą┤ąĄčé ą▓čŗą┤ą░ą▓ą░čéčīčüčÅ ą▓ą╝ąĄčüč鹥 čüąŠ čüą╗ąĄą┤čāčÄčēąĄą╣ ą║ąŠą╝ą░ąĮą┤ąŠą╣ TMS.

// ąÆčŗą┤ą▓ąĖą│ą░ąĄą╝ ą┤ą░ąĮąĮčŗąĄ ąĮą░čĆčāąČčā č湥čĆąĄąĘ čüąŠčüč鹊čÅąĮąĖčÅ Shift-DR ąĖ Exit-DR:

byOutputBuffer[dwNumBytesToSend++] = 0x3B;

// ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ = ą┤ą╗ąĖąĮą░ + 1 (ąĘą┤ąĄčüčī 2 čéą░ą║čéą░):

byOutputBuffer[dwNumBytesToSend++] = 0x01;

// ąÆčŗą┤ą▓ąĖą│ą░ąĄą╝ 101 (ą┐ąŠčüą╗ąĄą┤ąĮąĖą╣ ą▒ąĖčé ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ):

byOutputBuffer[dwNumBytesToSend++] = 0x01;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ TMS:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąŚą┤ąĄčüčī ą▓čŗą┤ą░ąĄčéčüčÅ ą║ąŠą╝ą░ąĮą┤ą░ TMS čü ąŠą┤ąĮąĖą╝ čéą░ą║č鹊ą╝. ąöą░ąĮąĮčŗąĄ ą┐čĆąŠą┤ąŠą╗ąČą░čÄčé ą▓ą┤ą▓ąĖą│ą░čéčīčüčÅ.

// ąÆčŗą┤ą▓ąĖą│ą░ąĄą╝ TMS, čćąĖčéą░ąĄą╝ 1 ą▒ąĖčé:

byOutputBuffer[dwNumBytesToSend++] = 0x6B;

// ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ = ą┤ą╗ąĖąĮą░ + 1 (ąĘą┤ąĄčüčī 1 čéą░ą║čé):

byOutputBuffer[dwNumBytesToSend++] = 0x00;

// ąöą░ąĮąĮčŗąĄ čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤, čéą░ą║ čćč鹊 TMS čüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ ą╗ąŠą│. 1. ąóą░ą║ąČąĄ

// ą▒ąĖčé 7 ą▓čŗą┤ą▓ąĖą│ą░ąĄčéčüčÅ ąĮą░ ą▓čŗčģąŠą┤ TDI, ąĖ čéą░ą║ąČąĄ 1 ą▒ąĖčé ą╗ąŠą│. 1 ąŠčüčéą░ą▓ąĖčé TMS ą▓ čüąŠčüč鹊čÅąĮąĖąĖ

// ą╗ąŠą│. 1 ą┤ą╗čÅ čüą╗ąĄą┤čāčÄčēąĖčģ ą║ąŠą╝ą░ąĮą┤:

byOutputBuffer[dwNumBytesToSend++] = 0x83;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ TMS:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

// ąØą░ą▓ąĖą│ą░čåąĖčÅ TMS ą┐ąŠ čüąŠčüč鹊čÅąĮąĖčÅą╝ Update-DR -> Select-DR-Scan -> Select-IR-Scan

// -> Test Logic Reset: TMS=1 TMS=1 TMS=1 TMS=1. ąØąĄ čćąĖčéą░ąĄą╝ ą┤ą░ąĮąĮčŗąĄ ą▓ čüąŠčüč鹊čÅąĮąĖčÅčģ

// Update-DR -> Select-DR-Scan -> Select-IR-Scan -> Test Logic Reset:

byOutputBuffer[dwNumBytesToSend++] = 0x4B;

// ąÜąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ = ą┤ą╗ąĖąĮą░ + 1 (ąĘą┤ąĄčüčī 4 čéą░ą║čéą░):

byOutputBuffer[dwNumBytesToSend++] = 0x03;

// ąöą░ąĮąĮčŗąĄ čüą┤ą▓ąĖą│ą░čÄčéčüčÅ ą╝ą╗ą░ą┤čłąĖą╝ ą▒ąĖč鹊ą╝ ą▓ą┐ąĄčĆąĄą┤, čéą░ą║ čćč鹊 ą┤ą░ąĮąĮčŗąĄ TMS ą▒čāą┤čāčé 101100:

byOutputBuffer[dwNumBytesToSend++] = 0xFF;

// ą×čéą┐čĆą░ą▓ą║ą░ ą║ąŠą╝ą░ąĮą┤čŗ TMS:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

do

{

// ą¤ąŠą╗čāč湥ąĮąĖąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣čé ą▓ąŠ ą▓čģąŠą┤ąĮąŠą╝ ą▒čāč乥čĆąĄ čāčüčéčĆąŠą╣čüčéą▓ą░:

ftStatus = FT_GetQueueStatus(ftHandle, &dwNumBytesToRead);

} while ((dwNumBytesToRead == 0) && (ftStatus == FT_OK));

// ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ čåąĖą║ą╗ą░ ą┐čĆąĖ ąŠčłąĖą▒ą║ąĄ ąĖą╗ąĖ ą┐ąŠ čéą░ą╣ą╝ą░čāčéčā

// ą¦č鹥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĖąĘ ą▓čģąŠą┤ąĮąŠą│ąŠ ą▒čāč乥čĆą░:

ftStatus = FT_Read(ftHandle, &byInputBuffer, dwNumBytesToRead, &dwNumBytesRead);

printf("\n");

printf("TI SN74BCT8244A IR default value is 0x81\n");

printf("The value scanned by the FT2232H is 0x%x\n",

byInputBuffer[dwNumBytesRead - 3]);

printf("\n");

printf("TI SN74BCT8244A DR bypass expected data is 00000010 = 0x2\n");

printf(" The value scanned by the FT2232H = 0x%x\n",

(byInputBuffer[dwNumBytesRead-1] >> 5));

// ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ Test-Logic-Reset. ąÆ čüąŠčüč鹊čÅąĮąĖąĖ

// Test-Logic-Reset ąĮąĄ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčéčüčÅ ąĮąĖą║ą░ą║ąĖčģ ą┤ąĄą╣čüčéą▓ąĖą╣, č鹊ą╗čīą║ąŠ ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāąĄčéčüčÅ

// ą│ąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ ą▒ąĄąĘ ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓:

byOutputBuffer[dwNumBytesToSend++] = 0x8F;

// (0x0002 + 1) * 8 = 24 čéą░ą║čéą░

byOutputBuffer[dwNumBytesToSend++] = 0x02;

byOutputBuffer[dwNumBytesToSend++] = 0x00;

// ąÆčŗą┤ą░čćą░ ą║ąŠą╝ą░ąĮą┤ ą┤ą╗čÅ čéą░ą║č鹊ą▓:

ftStatus = FT_Write(ftHandle, byOutputBuffer, dwNumBytesToSend, &dwNumBytesSent);

dwNumBytesToSend = 0; // čüą▒čĆąŠčü čāą║ą░ąĘą░č鹥ą╗čÅ ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ ą▒čāč乥čĆ

/*

// -----------------------------------------------------------

// ąŚą░ą║čĆąŠąĄą╝ ą▓čüąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ čĆąĄčüčāčĆčüčŗ:

// -----------------------------------------------------------

*/

printf("\nJTAG program executed successfully.\n");

printf("Press Enter to continue\n");

getchar(); // ą×ąČąĖą┤ą░ąĮąĖąĄ ąĮą░ąČą░čéąĖčÅ ą║ą╗ą░ą▓ąĖčłąĖ ą▓ąŠąĘą▓čĆą░čéą░ ą║ą░čĆąĄčéą║ąĖ

FT_Close(ftHandle); // ąŚą░ą║čĆčŗčéąĖąĄ ą┐ąŠčĆčéą░

return 0; // ąŻčüą┐ąĄčłąĮčŗą╣ ą▓čŗčģąŠą┤ ąĖąĘ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ

}

ąĀąĖčü 3.1. ą×čüčåąĖą╗ą╗ąŠą│čĆą░ą╝ą╝ą░ čüąĖą│ąĮą░ą╗ąŠą▓ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ SN74BCT8244A.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą▓čŗčģąŠą┤ TDI ą▓čüąĄą│ą┤ą░ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ, ąĖ ą▓čģąŠą┤ TDO ą┐ąŠą┤čéčÅąĮčāčé ą║ ą╗ąŠą│. 1 ą╝ąĖą║čĆąŠčüčģąĄą╝ąŠą╣ SN74BCT8244A. ąÆ ą┤ą░čéą░čłąĖč鹥 Texas Instruments ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą▒ą╗ą░čüč鹥ą╣ "donŌĆÖt care" (ąĮąĄ ąĖą╝ąĄąĄčé ąĘąĮą░č湥ąĮąĖčÅ), čćč鹊 ąĮą░ čŹč鹊ą╝ čüą║čĆąĖąĮčłąŠč鹥 čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą╗ąŠą│. 1.

ąØąĖąČąĄ ą┐ąŠą║ą░ąĘą░ąĮąŠ, ą║ą░ą║ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ TCK ą▒ąĄąĘ ą║ą░ą║ąŠą╣-ą╗ąĖą▒ąŠ ą░ą║čéąĖą▓ąĮąŠčüčéąĖ ąĮą░ TDI, TDO ąĖą╗ąĖ TMS.

ąĀąĖčü. 3.2. ąōąĄąĮąĄčĆą░čåąĖčÅ TCK.

ąōąĄąĮąĄčĆą░čåąĖčÅ čéą░ą║č鹊ą▓ ą┐ąŠą╗ąĄąĘąĮą░ ą┤ą╗čÅ ąĘą░ą┐čāčüą║ą░ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ č鹥čüčéą░ ą▓ąĮčāčéčĆąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ TAP. ąŚą┤ąĄčüčī ąĖą╝ąĄąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą┐čåąĖą╣, ą║ąŠč鹊čĆčŗąĄ ą▓ą║ą╗čÄčćą░čÄčé ą│ąĄąĮąĄčĆą░čåąĖčÄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ąĖą╝ą┐čāą╗čīčüąŠą▓, ąĖą╗ąĖ ą▓čŗą┤ą░čćą░ ąĖą╝ą┐čāą╗čīčüąŠą▓, ą┐ąŠą║ą░ čüąĖą│ąĮą░ą╗ GPIO ąĮąĄ ą┐ąĄčĆąĄą╣ą┤ąĄčé ą▓ ąĖąĘą▓ąĄčüčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ 24 čéą░ą║č鹊ą▓čŗčģ ąĖą╝ą┐čāą╗čīčüą░.

[ąĪčüčŗą╗ą║ąĖ]

1. AN_129 Interfacing FTDI USB Hi-Speed Devices to a JTAG TAP site:ftdichip.com.

2. FT2232H: ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮą░čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮą░čÅ USB ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ ą┤ą╗čÅ I/O.

3. AN_108 Command Processor for MPSSE and MCU Host Bus Emulation Modes site:ftdichip.com.

4. FT2232H Board - ą╝ą░ą║ąĄčéąĮą░čÅ ą┐ą╗ą░čéą░ ąĮą░ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮąŠą╝ čćąĖą┐ąĄ ą╝ąŠčüčéą░ USB čäąĖčĆą╝čŗ FTDI.

5. 170129FT2232-JTAG-Boundary-Scan.zip - ą┐čĆąĖą╝ąĄčĆčŗ ą║ąŠą┤ą░, ą┤čĆą░ą╣ą▓ąĄčĆčŗ, ą┤ąŠą║čāą╝ąĄąĮčéą░čåąĖčÅ. |