|

ąŻ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ADSP-BF538 ąĄčüčéčī č湥čéčŗčĆąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┐ąŠčĆčéą░ (SPORT). ą×ąĮąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┐čĆąŠč鹊ą║ąŠą╗čŗ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗą╝ąĖ, ąĖ ą╝ąŠą│čāčé ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą┐čĆčÅą╝ąŠąĄ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖąĄ ą╝ąĄąČą┤čā ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ ą▓ ą╝ąĮąŠą│ąŠą┐čĆąŠčåąĄčüčüąŠčĆąĮąŠą╣ čüąĖčüč鹥ą╝ąĄ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓čüąĄ ąĮąĄą┐ąŠąĮčÅčéąĮčŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ čĆą░ąĘą┤ąĄą╗ąĄ ąĪą╗ąŠą▓ą░čĆąĖą║ čüčéą░čéčīąĖ [3].

ąŁčéąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┐ąŠčĆčéčŗ (SPORT0, SPORT1, SPORT2, SPORT3) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ąĖąĮč鹥čĆč乥ą╣čü ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ ą┤ą╗čÅ čłąĖčĆąŠą║ąŠą│ąŠ čüą┐ąĄą║čéčĆą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ SPORT ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčé č鹊ą╗čīą║ąŠ čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ; ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąŠą▒ą╝ąĄąĮ (ą║ą░ą║ čā RS-232) čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ č湥čĆąĄąĘ UART [2]. ąÜą░ąČą┤čŗą╣ SPORT ąĖą╝ąĄąĄčé ąŠą┤ąĮčā ą│čĆčāą┐ą┐čā ą▓čŗą▓ąŠą┤ąŠą▓ (primary data, secondary data, clock ąĖ frame sync) ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą▓č鹊čĆąŠą╣ ąĮą░ą▒ąŠčĆ ą▓čŗą▓ąŠą┤ąŠą▓ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░. ążčāąĮą║čåąĖąĖ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ ą┐ąŠ ąŠčéą┤ąĄą╗čīąĮąŠčüčéąĖ. ąÜą░ąČą┤čŗą╣ SPORT čĆą░ą▒ąŠčéą░ąĄčé ą║ą░ą║ ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓ ąŠą▒ąŠąĖčģ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅčģ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ SPORT ą╝ąŠą│čāčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ąĮčāąČąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ (bit rate), čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ (frame sync) ąĖ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé ąĮą░ čüą╗ąŠą▓ąŠ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ MMR-čĆąĄą│ąĖčüčéčĆąŠą▓.

ąĪąŠą│ą╗ą░čłąĄąĮąĖčÅ ąĖą╝ąĄąĮąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĖ ą▓čŗą▓ąŠą┤ąŠą▓ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą╝ą░ą╗ąĄąĮčīą║čāčÄ ą▒čāą║ą▓čā x ą┤ą╗čÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ čåąĖčäčĆčŗ ąŠčé 0 ą┤ąŠ 3. ąØą░ą┐čĆąĖą╝ąĄčĆ, RFSx ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą▓čŗą▓ąŠą┤ą░ą╝ RFS0, RFS1, RFS2 ąĖą╗ąĖ RFS3, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖčģ SPORT0, SPORT1, SPORT2 ąĖ SPORT3. LSB ąŠą▒ąŠąĘąĮą░čćą░ąĄčé ą╝ą╗ą░ą┤čłąĖą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé (least significant bit), ąĖ MSB ąŠąĘąĮą░čćą░ąĄčé čüčéą░čĆčłąĖą╣ ąĘąĮą░čćą░čēąĖą╣ ą▒ąĖčé (most significant bit).

ąÆčüąĄ ą┐ąŠčĆčéčŗ SPORT ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčéčüčÅ čéą░ą║ąČąĄ ąŠą┤ąĖąĮą░ą║ąŠą▓ąŠ. ąÜą░ąČą┤čŗą╣ SPORTx ąĖą╝ąĄąĄčé čüą▓ąŠą╣ ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ.

SPORTx ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąĖą╝ą┐čāą╗čīčüčŗ ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (frame sync), čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ąĮą░čćą░ą╗ąŠ ą║ą░ąČą┤ąŠą│ąŠ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą┐ą░ą║ąĄčéą░ ą▒ąĖčé, ąĖ čéą░ą║č鹊ą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ ą╝ą░čĆą║ąĄčĆą░ ą▒ąĖčé (bit clock), ą┐ąŠą╝ąĄčćą░čÄčēąĖąĄ ąĮą░čćą░ą╗ąŠ ą▒ąĖčéą░ ą┤ą░ąĮąĮčŗčģ. ąöą╗čÅ ą▒čāč乥čĆąŠą▓ TX ąĖ RX ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ bit clock ąĖ frame sync.

ąĪ ąĮą░ą▒ąŠčĆąŠą╝ ąŠą┐čåąĖą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ čéą░ą║č鹊ą▓ ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčŗ SPORT ą┐ąŠąĘą▓ąŠą╗čÅčÄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī čĆą░ąĘą╗ąĖčćąĮčŗąĄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┐čĆąŠč鹊ą║ąŠą╗čŗ, ą▓ą║ą╗čÄčćą░čÅ H.100, ąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┐čĆąŠąĘčĆą░čćąĮčŗą╣ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čüą░ čüąŠ ą╝ąĮąŠą│ąĖą╝ąĖ ą║ąŠąĮą▓ąĄčĆč鹥čĆą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ ąĖ ą║ąŠą┤ąĄą║ą░ą╝ąĖ, čĆą░ą▒ąŠčéą░čÄčēąĖą╝ąĖ ą┐ąŠ ąĖąĮą┤čāčüčéčĆąĖą░ą╗čīąĮčŗą╝ čüčéą░ąĮą┤ą░čĆčéą░ą╝.

SPORTx ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī ąĮą░ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čéą░čģ ą▒ąĖčé ą┤ąŠ SCLK/2 ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, ąĖą╗ąĖ ą┤ąŠ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čüą╗čāčćą░čÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą│ąĄąĮąĄčĆą░čåąĖąĖ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▒ąĖčé. ąÆąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ą┤ą╗čÅ SPORT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ą╝ąĄąĮčīčłąĄ čćą░čüč鹊čéčŗ SCLK. ąØąĄąĘą░ą▓ąĖčüąĖą╝ąŠąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą▒ąŠą╗čīčłąĄ ą│ąĖą▒ą║ąŠčüčéąĖ ą┐čĆąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╝ ąŠą▒ą╝ąĄąĮąĄ ą┤ą░ąĮąĮčŗą╝ąĖ.

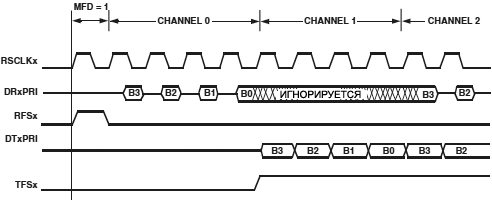

ąóą░ą║čéčŗ ą▒ąĖčé SPORT ąĖ čüąĖą│ąĮą░ą╗čŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ ą╝ąŠą│čāčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą▓ąĮčāčéčĆąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą╗ąĖą▒ąŠ ą╝ąŠą│čāčé ą┐ąŠą┤ą░ą▓ą░čéčīčüčÅ ąŠčé ą▓ąĮąĄčłąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░. ą¤ąŠčĆčéčŗ SPORT ą╝ąŠą│čāčé čĆą░ą▒ąŠčéą░čéčī čü č乊čĆą╝ą░č鹊ą╝ ą┐ąĄčĆąĄą┤ą░čćąĖ LSB first (ą╝ą╗ą░ą┤čłąĖą╣ ą▒ąĖčé ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝) ąĖą╗ąĖ MSB first (čüčéą░čĆčłąĖą╣ ą▒ąĖčé ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝), čü ą▓čŗą▒ąĖčĆą░ąĄą╝ąŠą╣ ą┤ą╗ąĖąĮąŠą╣ čüą╗ąŠą▓ą░ ąŠčé 3 ą┤ąŠ 32 ą▒ąĖčé. ą×ąĮąĖ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą▓čŗą▒ąĖčĆą░ąĄą╝čŗąĄ čĆąĄąČąĖą╝čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ╬╝-law ąĖą╗ąĖ A-law ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮą░ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ čāčĆąŠą▓ąĮąĄ. ąöą░ąĮąĮčŗąĄ SPORT ą╝ąŠą│čāčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ą╝ąĄąČą┤čā ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą▓ čćąĖą┐ ą┐ą░ą╝čÅčéčīčÄ ąĖ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéčīčÄ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ ą▒ą╗ąŠą║ąŠą▓čŗčģ ą┐ąĄčĆąĄčüčŗą╗ąŠą║ DMA [4]. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą║ą░ąČą┤čŗą╣ SPORTx ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čĆąĄąČąĖą╝ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ TDM (time-division-multiplexed).

ąÜą░ąČą┤čŗą╣ SPORTx ąĖą╝ąĄąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čäčāąĮą║čåąĖąĖ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ:

ŌĆó ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ čäčāąĮą║čåąĖą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░.

ŌĆó ąĪą╗ąŠą▓ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą╝ąŠą│čāčé ą▒čŗčéčī čĆą░ąĘą╝ąĄčĆąĮąŠčüčéčīčÄ ąŠčé 3 ą┤ąŠ 32 ą▒ąĖčé, ą╝ąŠąČąĮąŠ ą┐ąŠ ą▓čŗą▒ąŠčĆčā ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ą┐ąĄčĆą▓čŗą╝ MSB ą╗ąĖą▒ąŠ LSB.

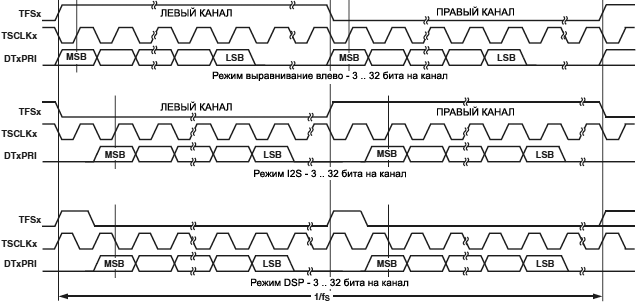

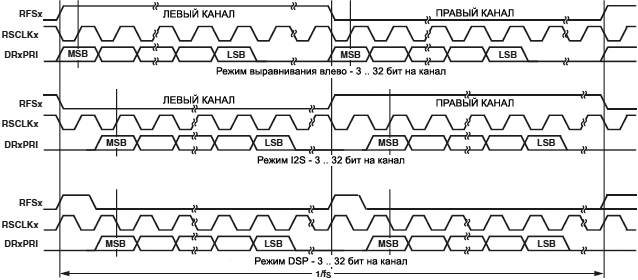

ŌĆó ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čĆą░ąĘą▒ąĖąĄąĮąĖčÅ ąĮą░ čäčĆąĄą╣ą╝čŗ ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ čü čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ I2S, ą░ čéą░ą║ąČąĄ čü ą┤čĆčāą│ąĖą╝ąĖ č乊čĆą╝ą░čéą░ą╝ąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ ąĘą▓čāą║ą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗąĄ ą▓ą╗ąĄą▓ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ čüč鹥čĆąĄąŠ).

ŌĆó ąĢčüčéčī FIFO čü ą┤ą▓ąŠą╣ąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĄą╣ ą┤ą░ąĮąĮčŗčģ (ąĖ čäčāąĮą║čåąĖčÅ ą┐čĆąĖąĄą╝ą░, ąĖ čäčāąĮą║čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╝ąĄčÄčé čĆąĄą│ąĖčüčéčĆ ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ ąĖ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░), čćč鹊 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čüąĄčĆą▓ąĖčü ąŠą▒čüą╗čāąČąĖą▓ą░ąĮąĖčÅ SPORT ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ.

ŌĆó ą£ąŠąČąĮąŠ čüąŠčüčéą░ą▓ą╗čÅčéčī čåąĄą┐ąŠčćą║ąĖ ą┐ąĄčĆąĄą┤ą░čć DMA ą┤ą╗čÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą▒ą╗ąŠą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ą¤čĆąĄą┤ąŠčüčéą░ą▓ą╗ąĄąĮčŗ ą┤ą▓ą░ čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čÄčēąĖčģ ąĖ ą┤ą▓ą░ čüąĖąĮčģčĆąŠąĮąĮčŗčģ ą┐čĆąĖąĮąĖą╝ą░čÄčēąĖčģ ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ąĖ ą▒čāč乥čĆčŗ ą▓ ą║ą░ąČą┤ąŠą╝ SPORT, čćč鹊ą▒čŗ čāą┤ą▓ąŠąĖčéčī ą┐čĆąŠą┐čāčüą║ąĮčāčÄ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄą╝čŗčģ ą┐ąŠč鹊ą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ.

ŌĆó ąÆčŗą┐ąŠą╗ąĮąĄąĮąĖąĄ ą░ą┐ą┐ą░čĆą░čéąĮąŠą│ąŠ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ A-law ąĖ ╬╝-law ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ čüą╗ąŠą▓ (ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÜąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ").

ŌĆó ąōąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░ čéą░ą║čéčŗ ą▒ąĖčé ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ čäčĆąĄą╣ą╝ą░ ą▓ čłąĖčĆąŠą║ąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čćą░čüč鹊čé, ą╗ąĖą▒ąŠ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéą░ą║č鹊ą▓čŗąĄ čüąĖą│ąĮą░ą╗čŗ, ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗąĄ čüąĮą░čĆčāąČąĖ.

ŌĆó ą£ąŠąČąĄčé čĆą░ą▒ąŠčéą░čéčī ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ą║ą░ą║ čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░, čéą░ą║ ąĖ ą▒ąĄąĘ ąĮąĖčģ, čü čüąĖą│ąĮą░ą╗ą░ą╝ąĖ čäčĆąĄą╣ą╝ą░, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄ ąĖą╗ąĖ ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗą╝ąĖ čüąĮą░čĆčāąČąĖ, čü ą░ą║čéąĖą▓ąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą╗ąŠą│. 1 ąĖą╗ąĖ ą╗ąŠą│. 0 ą┤ą╗čÅ čüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░, ąĖ čü ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗą╝ąĖ ą┤ą▓čāą╝čÅ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčÅą╝ąĖ čłąĖčĆąĖąĮčŗ ąĖą╝ą┐čāą╗čīčüą░ ąĖ ą▓čĆąĄą╝ąĄąĮąĮčŗą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ čüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░.

ŌĆó ąÆčŗą┐ąŠą╗ąĮčÅąĄčé ąŠą┤ąĖąĮąŠčćąĮčāčÄ ą┐ąĄčĆąĄą┤ą░čćčā čüą╗ąŠą▓ą░ ą▓ ą┐ą░ą╝čÅčéčī čćąĖą┐ą░ ąĖ ąĖąĘ ą┐ą░ą╝čÅčéąĖ čćąĖą┐ą░ čü ą┐ąŠą┤ą┤ąĄčƹȹ║ąŠą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ŌĆó ąÆčŗą┐ąŠą╗ąĮčÅąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ čü ą┐čĆčÅą╝čŗą╝ ą┤ąŠčüčéčāą┐ąŠą╝ ą║ ą┐ą░ą╝čÅčéąĖ (DMA) ą▓ ą┐ą░ą╝čÅčéčī ąĖ ąĖąĘ ą┐ą░ą╝čÅčéąĖ ą┐ąŠą┤ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝ DMA Master. DMA ą╝ąŠąČąĄčé ąĘą░ą┐čāčüą║ą░čéčīčüčÅ čü ą░ą▓č鹊ą┐ąŠą▓č鹊čĆą░ą╝ąĖ ą▒čāč乥čĆą░ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ, ą┐ąŠą▓č鹊čĆčÅčÄčēąĖąĄčüčÅ, ąŠą┤ąĖąĮą░ą║ąŠą▓čŗąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĖą╗ąĖ ąĮą░ ą▒ą░ąĘąĄ ą┤ąĄčüą║čĆąĖą┐č鹊čĆąŠą▓ (ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ ąĖą╗ąĖ čü ą┐ąŠą▓č鹊čĆčÅčÄčēąĖą╝ąĖčüčÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ą╝ąĖ ą┐ąĄčĆąĄą┤ą░čć, ą║ą░ąČą┤ą░čÅ ąĖąĘ ą║ąŠč鹊čĆčŗčģ ą╝ąŠąČąĄčé ąĖą╝ąĄčéčī čĆą░ąĘąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ DMA).

ŌĆó ąÆčŗą┐ąŠą╗ąĮčÅąĄčé ą┐ąĄčĆąĄą┤ą░čćąĖ DMA ą▓ ą┐ą░ą╝čÅčéčī čćąĖą┐ą░ ąĖ ąĖąĘ ąĮąĄčæ. ąÜą░ąČą┤čŗą╣ SPORT ą╝ąŠąČąĄčé ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĖąĮčÅčéčī ąĖ ą┐ąĄčĆąĄą┤ą░čéčī ą▓ąĄčüčī ą▒ą╗ąŠą║ ą┤ą░ąĮąĮčŗčģ.

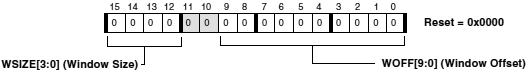

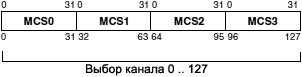

ŌĆó ąśą╝ąĄąĄčéčüčÅ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮčŗą╣ čĆąĄąČąĖą╝ ą┤ą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ TDM. ąÜą░ąČą┤čŗą╣ SPORT ą╝ąŠąČąĄčé ą┐čĆąĖąĮčÅčéčī ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čéčī ą┤ą░ąĮąĮčŗąĄ ą▓čŗą▒ąŠčĆąŠčćąĮąŠ ąĖąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ą▒ąĖčé TDM 128 čüąŠčüąĄą┤ąĮąĖčģ ą║ą░ąĮą░ą╗ąŠą▓ ąĖąĘ ąŠą▒čēąĄą│ąŠ ą┐ąŠč鹊ą║ą░ ą┤ąŠ 1024 ą║ą░ąĮą░ą╗ąŠą▓. ąŁč鹊čé čĆąĄąČąĖą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąĄąĘąĄąĮ ą▓ ą║ą░č湥čüčéą▓ąĄ čüąĄč鹥ą▓ąŠą╣ čüčģąĄą╝čŗ ąŠą▒ą╝ąĄąĮą░ ą╝ąĄąČą┤čā ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░ą╝ąĖ. 128 ą┤ąŠčüčéčāą┐ąĮčŗčģ ą║ą░ąĮą░ą╗ąŠą▓ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą╝ąŠąČąĮąŠ ą▓čŗą▒čĆą░čéčī ą┐čāč鹥ą╝ čüčéą░čĆčéą░ čü ą╗čÄą▒ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąŠčé 0 ą┤ąŠ 895 = (1023 ŌĆō 128). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ą▓čŗą▒ąŠčĆą░ ąĖ čĆąĄą│ąĖčüčéčĆ WSIZE čāą┐čĆą░ą▓ą╗čÅčÄčé č鹥ą╝, ą║ą░ą║ąŠąĄ ą┐ąŠą┤ą╝ąĮąŠąČąĄčüčéą▓ąŠ ąĖąĘ 128 ą║ą░ąĮą░ą╗ąŠą▓ ą┐ąŠą┐ą░ą┤ą░čÄčé ą▓ ą░ą║čéąĖą▓ąĮčāčÄ ąŠą▒ą╗ą░čüčéčī ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ ą┐ąĄčĆąĄą▓ąŠą┤čćąĖą║ą░: čéčāčé ą╝ąĮąŠą│ąŠ č湥ą│ąŠ ą┐ąŠąĮą░ą┐ąĖčüą░ąĮąŠ, ąĮąŠ ą║ čüąŠąČą░ą╗ąĄąĮąĖčÄ SPORT ąĖą╝ąĄąĄčé ąĮąĄ čéą░ą║ čāąČ ą╝ąĮąŠą│ąŠ ąĮą░čüčéčĆąŠąĄą║, ą║ą░ą║ čģąŠč鹥ą╗ąŠčüčī ą▒čŗ. ąÆ čćą░čüčéąĮąŠčüčéąĖ, ąŠč湥ąĮčī ą▒ąĄą┤ąĮčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ čüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (ą▓ čüčĆą░ą▓ąĮąĄąĮąĖąĖ, ąĮą░ą┐čĆąĖą╝ąĄčĆ, čü ą┐ąŠčĆč鹊ą╝ SSC ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ AT91 ą║ąŠą╝ą┐ą░ąĮąĖąĖ Atmel), čćč鹊 čāčüą╗ąŠąČąĮčÅąĄčé ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ SPORT čüąŠą▓ą╝ąĄčüčéąĮąŠ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ąĖ ąÉą”ą¤ č鹊ą╣ ąČąĄ ą║ąŠą╝ą┐ą░ąĮąĖąĖ Analog Devices. ąÆ čüčāčēąĮąŠčüčéąĖ, SPORT ąŠč湥ąĮčī ą┐čĆąŠčüč鹊ą╣, ąĖ ą▒ąĄą┤ąĮčŗą╣ ą┐ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčÅą╝ č鹊ąĮą║ąĖčģ ąĮą░čüčéčĆąŠąĄą║, čé. ąĄ. ąŠąĮ ąĘą░č鹊č湥ąĮ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ ąĮą░ ą║ąŠąĮą║čĆąĄčéąĮčŗąĄ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąĪčĆąĄą┤ąĖ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮčŗčģ čüą▓ąŠą╣čüčéą▓ SPORT ą╝ąŠąČąĮąŠ ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 ą┐ąŠčĆč鹊ą▓ SPORT ą╝ąĮąŠą│ąŠ, čåąĄą╗čŗčģ 4 čłčéčāą║ąĖ, ąĖ čćč鹊 ąŠąĮąĖ čüąĖąĮčģčĆąŠąĮąĮčŗ ą╝ąĄąČą┤čā čüąŠą▒ąŠą╣ ąĖ čéą░ą║ąČąĄ čüąĖąĮčģčĆąŠąĮąĮčŗ čü ą┤čĆčāą│ąĖą╝ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, čéą░ą╣ą╝ąĄčĆą░ą╝ąĖ, ą┐ąŠč鹊ą╝čā čćč鹊 čéą░ą║čéąĖčĆčāčÄčéčüčÅ ąŠą▒čēąĄą╣ čćą░čüč鹊č鹊ą╣ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ SCK). ąĢčēąĄ ą╝ąĮąĄ ąŠč湥ąĮčī ąĮčĆą░ą▓čÅčéčüčÅ ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéąĖ DMA ą┤ą╗čÅ čĆą░ą▒ąŠčéčŗ čüąŠą▓ą╝ąĄčüčéąĮąŠ čü SPORT - ą▓ąŠčé čéčāčé ą▓čüąĄ čģąŠčĆąŠčłąŠ ąĖ ą┐čĆąĖčÅčéąĮąŠ čüą┤ąĄą╗ą░ąĮąŠ.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 13-1 ą┐ąŠą║ą░ąĘą░ąĮčŗ ą▓čŗą▓ąŠą┤čŗ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ SPORT.

ąóą░ą▒ą╗ąĖčåą░ 13-1. ąÆčŗą▓ąŠą┤čŗ SPORT.

| ąÆčŗą▓ąŠą┤ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| DTxPRI |

Transmit Data Primary, ą┐ąĄčĆą▓ąĖčćąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. |

| DTxSEC |

Transmit Data Secondary, ą▓č鹊čĆąĖčćąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ. |

| TSCLKx |

Transmit Clock, čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé ą┐ąĄčĆąĄą┤ą░čćąĖ. |

| TFSx |

Transmit Frame Sync, čüąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ. |

| DRxPRI |

Receive Data Primary, ą┐ąĄčĆą▓ąĖčćąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ. |

| DRxSEC |

Receive Data Secondary, ą▓č鹊čĆąĖčćąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ. |

| RSCLKx |

Receive Clock, čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą▒ąĖčé ą┐čĆąĖąĄą╝ą░. |

| RFSx |

Receive Frame Sync, čüąĖą│ąĮą░ą╗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ąŠą▓ ą┐čĆąĖąĄą╝ą░. |

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: čā SPORT0 ąĖ SPORT1 ąĖą╝ąĄčÄčéčüčÅ ą▓čŗą┤ąĄą╗ąĄąĮąĮčŗąĄ ąĮąŠąČą║ąĖ ą║čĆąĖčüčéą░ą╗ą╗ą░, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ SPORT2 ąĖ SPORT3 ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆčāčÄčé čüą▓ąŠąĖ čäčāąĮą║čåąĖąĖ čü ą┐ąŠčĆčéą░ą╝ąĖ GPIO. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čŹčéąĖ GPIO čüą╝. čüčéą░čéčīčÄ [5].

ąÆ čéą░ą▒ą╗ąĖčåą░čģ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ čåąŠą║ąŠą╗ąĄą▓ą║ą░ ąĮąŠąČąĄą║ 316-ą▓čŗą▓ąŠą┤ąĮąŠą│ąŠ ą║ąŠčĆą┐čāčüą░ CSP BGA ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ Blackfin ADSP-BF538, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą║ SPORT0, SPORT1, SPORT2, SPORT3.

[SPORT0]

| ąÆčŗą▓ąŠą┤ |

ąØąŠąČą║ą░ CSP BGA |

| RSCLK0 |

R2 |

| RFS0 |

P2 |

| DR0PRI |

N2 |

| DR0SEC |

J3 |

| TSCLK0 |

P1 |

| TFS0 |

N1 |

| DT0PRI |

M1 |

| DT0SEC |

G3 |

[SPORT1]

| ąÆčŗą▓ąŠą┤ |

ąØąŠąČą║ą░ CSP BGA |

| RSCLK1 |

L1 |

| RFS1 |

K1 |

| DR1PRI |

J2 |

| DR1SEC |

H3 |

| TSCLK1 |

H2 |

| TFS1 |

J1 |

| DT1PRI |

H1 |

| DT1SEC |

D3 |

[SPORT2]

| ąÆčŗą▓ąŠą┤ |

ąØąŠąČą║ą░ CSP BGA |

| RSCLK2/PE0 |

W11 |

| RFS2/PE1 |

Y11 |

| DR2PRI/PE2 |

W12 |

| DR2SEC/PE3 |

V13 |

| TSCLK2/PE4 |

Y12 |

| TFS2/PE5 |

Y13 |

| DT2PRI/PE6 |

W13 |

| DT2SEC/PE7 |

V16 |

[SPORT3]

| ąÆčŗą▓ąŠą┤ |

ąØąŠąČą║ą░ CSP BGA |

| RSCLK3/PE8 |

U18 |

| RFS3/PE9 |

T18 |

| DR3PRI/PE10 |

R18 |

| DR3SEC/PE11 |

P18 |

| TSCLK3/PE12 |

L18 |

| TFS3/PE13 |

M18 |

| DT3PRI/PE14 |

F18 |

| DT3SEC/PE15 |

N18 |

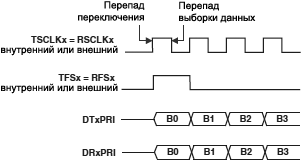

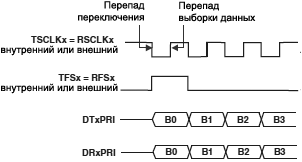

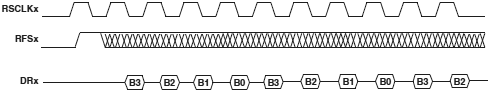

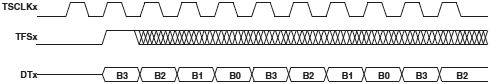

SPORT ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ čüą▓ąŠąĖ ą▓čģąŠą┤čŗ DRxPRI ąĖ DRxSEC, ąĖ ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ čüą▓ąŠąĖ ą▓čŗčģąŠą┤čŗ DTxPRI ąĖ DTxSEC. ą×ąĮ ą╝ąŠąČąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą┐čĆąĖąĮąĖą╝ą░čéčī ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī, čćč鹊 ą┤ą░ąĄčé ą┐ąŠą╗ąĮąŠą┤čāą┐ą╗ąĄą║čüąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ. ąöą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ (DTxPRI ąĖ DTxSEC) čüąĖąĮčģčĆąŠąĮąĮčŗ čü čéą░ą║čéą░ą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (TSCLKx). ąöą╗čÅ ą┐čĆąĖąĄą╝ą░ ą▒ąĖčéčŗ ą┤ą░ąĮąĮčŗčģ (DRxPRI ąĖ DRxSEC) čüąĖąĮčģčĆąŠąĮąĮčŗ čü čéą░ą║čéą░ą╝ąĖ ą┐čĆąĖąĄą╝ą░ (RSCLKx). ąóą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ čÅą▓ą╗čÅąĄčéčüčÅ ą▓čŗčģąŠą┤ąŠą╝, ąĄčüą╗ąĖ čéą░ą║čéčŗ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą▓ąĮčāčéčĆąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ąĖą╗ąĖ ą▓čģąŠą┤ąŠą╝, ąĄčüą╗ąĖ čéą░ą║čéčŗ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ čüąĮą░čĆčāąČąĖ. ąĪąĖą│ąĮą░ą╗čŗ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ RFSx ąĖ TFSx ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ, čćč鹊ą▒čŗ ą┐ąŠą║ą░ąĘą░čéčī ąĮą░čćą░ą╗ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ ąĖą╗ąĖ ą┐ąŠč鹊ą║ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ čüą╗ąŠą▓.

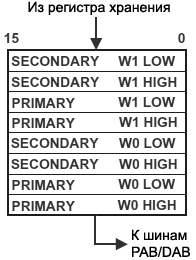

ąÆčŗą▓ąŠą┤čŗ ą┐ąĄčĆą▓ąĖčćąĮčŗčģ ąĖ ą▓č鹊čĆąĖčćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą╝ąĄč鹊ą┤ čāą▓ąĄą╗ąĖč湥ąĮąĖčÅ ą┐čĆąŠą┐čāčüą║ąĮąŠą╣ čüą┐ąŠčüąŠą▒ąĮąŠčüčéąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░. ą×ąĮąĖ ąĮąĄ ą▓ąĄą┤čāčé čüąĄą▒čÅ ą║ą░ą║ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠčéą┤ąĄą╗čīąĮčŗąĄ SPORT-čŗ; ą▓ą╝ąĄčüč鹊 čŹč鹊ą│ąŠ ąŠąĮąĖ čĆą░ą▒ąŠčéą░čÄčé čüąĖąĮčģčĆąŠąĮąĮąŠ (ąĖčüą┐ąŠą╗čīąĘčāčÅ ąŠą▒čēąĖą╣ čéą░ą║čé ąĖ čüąĖą│ąĮą░ą╗ čäčĆąĄą╣ą╝ą░), ąĮąŠ ą┐ąĄčĆąĄą│ąŠąĮčÅčÅ čĆą░ąĘąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąöą░ąĮąĮčŗąĄ, ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ č湥čĆąĄąĘ ą┐ąĄčĆą▓ąĖčćąĮčŗą╣ ąĖ ą▓č鹊čĆąĖčćąĮčŗą╣ ą▓čŗą▓ąŠą┤ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄą┤čāčÄčéčüčÅ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮčŗ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čłą░ą│ą░ ą▓ ą▒ą╗ąŠą║ąĄ ą│ąĄąĮąĄčĆą░č鹊čĆąŠą▓ ą░ą┤čĆąĄčüą░ ą┤ą░ąĮąĮčŗčģ (data address generators, DAG). ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ DAG čüą╝. [3].

ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ą░ą┤čĆąĄčüąŠą╝ ą┤ą╗čÅ TX ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮčŗ čĆąĄą│ąĖčüčéčĆčŗ TX ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╝ čüą┐ąŠčüąŠą▒ąŠą╝ - čüąĮą░čćą░ą╗ą░ ą┤ą╗čÅ ą┐ąĄčĆą▓ąĖčćąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░, ą┐ąŠč鹊ą╝ ą┤ą╗čÅ ą▓č鹊čĆąĖčćąĮąŠą│ąŠ, ąĖ čé. ą┤. ąŁč鹊 ą┐čĆąŠčēąĄ ą▓čŗą┐ąŠą╗ąĮčÅčéčī čü ą┐ąŠą╝ąŠčēčīčÄ čāąĘą╗ąŠą▓ DAG ą┐čĆąŠčåąĄčüčüąŠčĆą░.

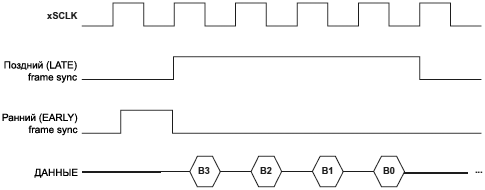

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ą░ą╝ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąĮą░ą▒ąČąĄąĮčŗ čüąĖą│ąĮą░ą╗ąŠą╝ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░. ąĪąĖą│ąĮą░ą╗ čäčĆąĄą╣ą╝ą░ ą╝ąŠąČąĄčé ą┐čĆąŠąĖčüčģąŠą┤ąĖčéčī ą╗ąĖą▒ąŠ ą▓ ąĮą░čćą░ą╗ąĄ ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ čüą╗ąŠą▓ą░, ą╗ąĖą▒ąŠ ą▓ ąĮą░čćą░ą╗ąĄ ą▒ą╗ąŠą║ą░ ąĖąĘ čüą╗ąŠą▓.

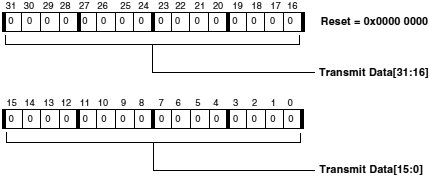

ąØą░ čĆąĖčü. 13-1 ą┐ąŠą║ą░ąĘą░ąĮą░ čāą┐čĆąŠčēąĄąĮąĮą░čÅ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ąŠą┤ąĮąŠą│ąŠ SPORT. ąöą░ąĮąĮčŗąĄ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ąĖąĘ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ čĆąĄą│ąĖčüčéčĆ SPORTx_TX č湥čĆąĄąĘ ą▓ąĮčāčéčĆąĄąĮąĮčÄčÄ čłąĖąĮčā ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝. ąŁčéąĖ ą┤ą░ąĮąĮčŗąĄ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą╝ąŠą│čāčé ą▒čŗčéčī ą░ą┐ą┐ą░čĆą░čéąĮąŠ ą║ąŠą╝ą┐čĆąĄčüčüąĖčĆąŠą▓ą░ąĮčŗ ąĖ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄą┤ą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ TX. ąæąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā ąĮą░ ą▓čŗą▓ąŠą┤ DTxPRI/DTxSEC, ą┐ąĄčĆą▓čŗą╝ ą╝ąŠąČąĄčé ąĖą┤čéąĖ MSB ąĖą╗ąĖ LSB (čŹč鹊 ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ), čüąĖąĮčģčĆąŠąĮąĮąŠ čü ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╝ąĖ čéą░ą║čéą░ą╝ąĖ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TSCLKx. ą¤čĆąĖąĮąĖą╝ą░čÄčēą░čÅ čćą░čüčéčī SPORT ą┐ąŠą╗čāčćą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ąŠčé ą▓čŗą▓ąŠą┤ą░ DRxPRI/DRxSEC čüąĖąĮčģčĆąŠąĮąĮąŠ čü čéą░ą║čéą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ RSCLKx. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅč鹊 ą▓čüąĄ čüą╗ąŠą▓ąŠ, ą┤ą░ąĮąĮčŗąĄ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ čĆą░čüčłąĖčĆčÅčÄčéčüčÅ (ąŠą┐ąĄčĆą░čåąĖčÅ, ąŠą▒čĆą░čéąĮą░čÅ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖčÄ), ąĘą░č鹥ą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ SPORTx_RX, ąĖ ąĘą░č鹥ą╝ ą▓ RX FIFO, ą│ą┤ąĄ ąŠąĮąĖ čüčéą░ąĮąŠą▓čÅčéčüčÅ ą┤ąŠčüčéčāą┐ąĮčŗą╝ąĖ ą┤ą╗čÅ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąĀąĖčü. 13-1. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ SPORT.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 1: ą▓čüąĄ ą┐čāčéąĖ ą┤ą░ąĮąĮčŗčģ čü čłąĖčĆąŠą║ąĖą╝ąĖ čüčéčĆąĄą╗ą║ą░ą╝ąĖ ąĖą╝ąĄčÄčé čłąĖčĆąĖąĮčā 16 ąĖą╗ąĖ 32 ą▒ąĖčéą░, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé SLEN. ąöą╗čÅ SLEN = 2 .. 15 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 16-ą▒ąĖčéąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ čü ą│ą╗čāą▒ąĖąĮąŠą╣ FIFO ąĖąĘ 8 čāčĆąŠą▓ąĮąĄą╣. ąöą╗čÅ SLEN = 16 .. 31, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 32-ą▒ąĖčéąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ čü ą│ą╗čāą▒ąĖąĮąŠą╣ FIFO 4 čāčĆąŠą▓ąĮčÅ.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ 2: čĆąĄą│ąĖčüčéčĆčŗ Tx čÅą▓ą╗čÅčÄčéčüčÅ ą┤ąĮąŠą╝ ą┤ą╗čÅ Tx FIFO, čĆąĄą│ąĖčüčéčĆčŗ Rx čÅą▓ą╗čÅčÄčéčüčÅ ą▓ąĄčĆčłąĖąĮąŠą╣ Rx FIFO.

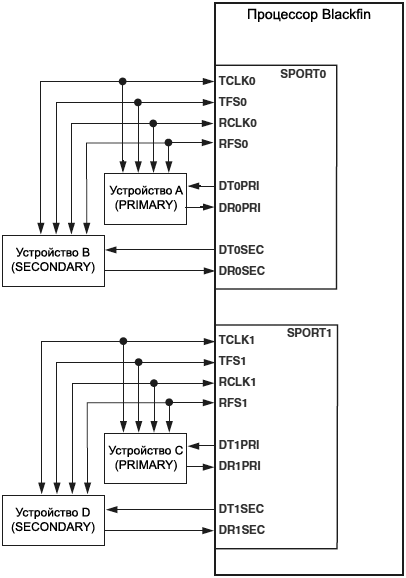

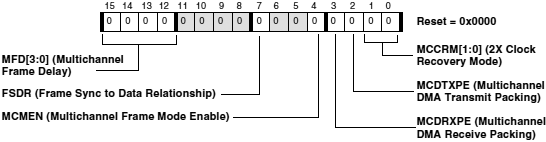

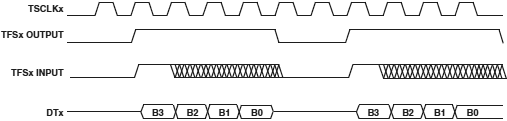

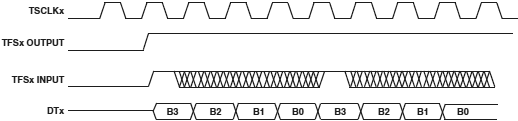

ąØą░ čĆąĖčü. 13-2 ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠąĄ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą║ ą┐ąŠčĆčéčā SPORT. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čāčüčéčĆąŠą╣čüčéą▓ą░ A ąĖ B ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī čüąĖąĮčģčĆąŠąĮąĮčŗą╝ąĖ, ą┐ąŠčüą║ąŠą╗čīą║čā ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą▒čēąĖąĄ čüąĖą│ąĮą░ą╗čŗ čäčĆąĄą╣ą╝ą░ ąĖ čéą░ą║č鹊ą▓. ąóąŠ ąČąĄ čüą░ą╝ąŠąĄ ą▓ąĄčĆąĮąŠ ąĖ ą┤ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ C ąĖ D.

ąĀąĖčü. 13-2. ąĪąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čü ą┐ąŠčĆč鹊ą╝ SPORT.

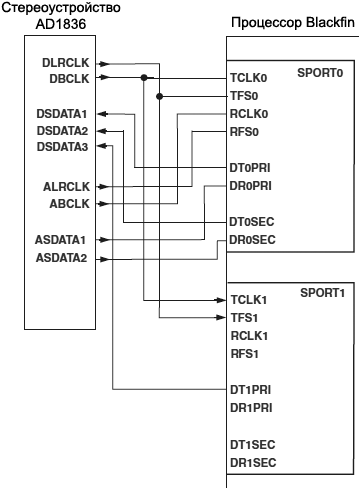

ąØą░ čĆąĖčü. 13-3 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ čüč鹥čĆąĄąŠč乊ąĮąĖč湥čüą║ąŠą│ąŠ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ čü 3 ą║ą░ąĮą░ą╗ą░ą╝ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ 2 ą║ą░ąĮą░ą╗ą░ą╝ąĖ ą┐čĆąĖąĄą╝ą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗčģ ą║ ą┐čĆąŠčåąĄčüčüąŠčĆčā.

ąĀąĖčü. 13-3. ą¤čĆąĖą╝ąĄčĆ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą┤ą╗čÅ ą▓čŗą▓ąŠą┤ą░ čüč鹥čĆąĄąŠčüąĖą│ąĮą░ą╗ą░.

[ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé SPORT]

ąÆ čŹč鹊ą╣ čüąĄą║čåąĖąĖ ąŠą┐ąĖčüą░ąĮ ąŠčüąĮąŠą▓ąĮąŠą╣ ą┐čĆąĖąĮčåąĖą┐ čĆą░ą▒ąŠčéčŗ SPORT, ąĖ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąŠą▒čŗčćąĮąŠąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ SPORT. ąóą░ą║ ą║ą░ą║ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčī SPORT ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ, ą▓ čŹč鹊ą╝ ąŠą┐ąĖčüą░ąĮąĖąĖ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮą░ č鹊ą╗čīą║ąŠ ąŠą┤ąĮą░ ąĖąĘ ą╝ąĮąŠą│ąĖčģ ą▓ąŠąĘą╝ąŠąČąĮčŗčģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖą╣.

ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ SPORTx_TX ą┐ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░ąĄčé SPORT ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĪąĖą│ąĮą░ą╗ TFSx ąĖąĮąĖčåąĖąĖčĆčāąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćą░ą╗ą░čüčī, ą║ą░ąČą┤ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, ąĘą░ą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ čĆąĄą│ąĖčüčéčĆ SPORTx_TX, ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ č湥čĆąĄąĘ FIFO ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŚą░č鹥ą╝ ą▒ąĖčéčŗ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ, ąĮą░čćąĖąĮą░čÅ čü ą╗ąĖą▒ąŠ MSB, ą╗ąĖą▒ąŠ čü LSB, ą║ą░ą║ čŹč鹊 ąĘą░ą┤ą░ąĮąŠ ąĮą░čüčéčĆąŠą╣ą║ąŠą╣ čĆąĄą│ąĖčüčéčĆą░ SPORTx_TCR1. ąÜą░ąČą┤čŗą╣ ą▒ąĖčé ą▓čŗą┤ą▓ąĖą│ą░ąĄčéčüčÅ ą┐ąŠ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╝čā ą┐ąĄčĆąĄą┐ą░ą┤čā TSCLKx. ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ TSCLKx ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ čäčĆąŠąĮčé ąĖą╗ąĖ čüą┐ą░ą┤. SPORT ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ąĘą░ą┐čĆąŠčü ą┐ąĄčĆąĄą┤ą░čćąĖ DMA, ą║ą░ą║ č鹊ą╗čīą║ąŠ ąĄčüčéčī ą╝ąĄčüč鹊 ą▓ TX FIFO.

ąÜą░ą║ č鹊ą╗čīą║ąŠ SPORT ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą▒ąĖčéčŗ, ąŠąĮąĖ ąĮą░ą║ą░ą┐ą╗ąĖą▓ą░čÄčé ąĖčģ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąĖąĄą╝ą░. ąÜąŠą│ą┤ą░ ą┐čĆąĖąĮčÅč鹊 ą▓čüąĄ čüą╗ąŠą▓ąŠ, ąŠąĮąŠ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ SPORT FIFO, ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ą┤ą╗čÅ čŹč鹊ą│ąŠ SPORT, ąĖą╗ąĖ ąĖąĮąĖčåąĖąĖčĆčāąĄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćą░ DMA. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą┐ąŠ-ą┤čĆčāą│ąŠą╝čā, ąĄčüą╗ąĖ ą▓čŗą┐ąŠą╗ąĮčÅąĄčéčüčÅ ą▒ą╗ąŠčćąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ DMA. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čĆą░ą▒ąŠčéčā DMA čüą╝. [4].

ąŚą░ą┐čĆąĄčé SPORT. SPORTx ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĘą░ą┐čĆąĄčēą░čÄčéčüčÅ ą┐čĆąĖ ą░ą┐ą┐ą░čĆą░čéąĮąŠą╝ ąĖą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą╝ čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░. SPORT čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮ ąĮą░ą┐čĆčÅą╝čāčÄ ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░(TSPEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPORTx_TCR1 ąĖ RSPEN ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPORTx_RCR1 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ). ąÜą░ąČą┤čŗą╣ ą╝ąĄč鹊ą┤ ą┤ą░ąĄčé čĆą░ąĘąĮčŗą╣ čŹčäč乥ą║čé ą┤ą╗čÅ SPORT.

ąĪą▒čĆąŠčü ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĘą░ą┐čĆąĄčēą░ąĄčé ą┐ąŠčĆčéčŗ SPORTx ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ SPORTx_TCR1, SPORTx_TCR2, SPORTx_RCR1 ąĖ SPORTx_RCR2 (ą▓ą║ą╗čÄčćą░čÅ čĆą░ąĘčĆąĄčłą░čÄčēąĖąĄ ą▒ąĖčéčŗ TSPEN ąĖ RSPEN) ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ SPORTx_TCLKDIV, SPORTx_RCLKDIV, SPORTx_TFSDIV ąĖ SPORTx_RFSDIV ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ čéą░ą║č鹊ą▓ ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░. ąøčÄą▒ą░čÅ ą┐čĆąŠąĖčüčģąŠą┤čÅčēą░čÅ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé čĆą░ą▒ąŠčéą░ ą▒čāą┤ąĄčé ą┐čĆąĄčĆą▓ą░ąĮą░.

ą×čćąĖčüčéą║ą░ ą▒ąĖč鹊ą▓ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ TSPEN ąĖ RSPEN ąĘą░ą┐čĆąĄčéąĖčé SPORTx ąĖ ąŠą▒ąŠčĆą▓ąĄčé ą╗čÄą▒čŗąĄ ą┐čĆąŠąĖčüčģąŠą┤čÅčēąĖąĄ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ąŠą┐ąĄčĆą░čåąĖąĖ. ąæąĖčéčŗ čüąŠčüč鹊čÅąĮąĖčÅ čéą░ą║ąČąĄ ąŠčćąĖčēą░čÄčéčüčÅ. ąæąĖčéčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąŠčüčéą░čÄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝ąĖ ąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ą║ąŠą│ą┤ą░ ąĖčģ ąĮčāąČąĮąŠ ąĖąĘą╝ąĄąĮąĖčéčī ąĖą╗ąĖ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░čéčī. ąöą╗čÅ ąĘą░ą┐čĆąĄčéą░ ą▓čŗčģąŠą┤ąĮčŗčģ čéą░ą║č鹊ą▓ SPORT ąĮčāąČąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī SPORT.

ąśą╝ąĄą╣č鹥 ą▓ ą▓ąĖą┤čā, čćč鹊 ąĘą░ą┐čĆąĄčēąĄąĮąĖąĄ SPORT č湥čĆąĄąĘ ą▒ąĖčéčŗ TSPEN/RSPEN ą╝ąŠąČąĄčé čāą║ąŠčĆąŠčéąĖčéčī č鹥ą║čāčēąĖąĄ ą░ą║čéąĖą▓ąĮčŗąĄ ąĖą╝ą┐čāą╗čīčüčŗ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ TFSx/RFSx ąĖ TSCLKx/RSCLKx, ąĄčüą╗ąĖ čŹčéąĖ čüąĖą│ąĮą░ą╗čŗ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮčŗ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą▓ąĮčāčéčĆąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░.

ąÜąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēą░ąĄčéčüčÅ SPORT ą▓ąŠ ą▓čĆąĄą╝čÅ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░, čüąĮą░čćą░ą╗ą░ ąĘą░ą┐čĆąĄčéąĖč鹥 TSPEN, ąĖ ąĘą░č鹥ą╝ ąĘą░ą┐čĆąĄčéąĖč鹥 RSPEN. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ąŠą▒ą░ TSPEN ąĖ RSPEN ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąĄčēąĄąĮčŗ ą┐ąĄčĆąĄą┤ ą┐ąŠą▓č鹊čĆąĮčŗą╝ ąĖčģ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝. ąØąĄą╗čīąĘčÅ ąĘą░ą┐čĆąĄčéąĖčéčī č鹊ą╗čīą║ąŠ TX ąĖą╗ąĖ č鹊ą╗čīą║ąŠ RX.

ąŻčüčéą░ąĮąŠą▓ą║ą░ čĆąĄąČąĖą╝ąŠą▓ SPORT. ąÜąŠąĮčäąĖą│čāčĆą░čåąĖčÅ SPORT ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖč鹊ą▓ ąĖ ąĘąĮą░č湥ąĮąĖą╣ ą▒ąĖč鹊ą▓čŗčģ ą┐ąŠą╗ąĄą╣ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ąÜą░ąČą┤čŗą╣ SPORT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┐ąĄčĆąĄą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖąĄą╝. ąÜą░ą║ č鹊ą╗čīą║ąŠ SPORT čĆą░ąĘčĆąĄčłąĄąĮ, ą┐ąŠčüą╗ąĄą┤čāčÄčēą░čÅ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPORT ąĘą░ą┐čĆąĄčēąĄąĮą░ (ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ SPORTx_RCLKDIV, SPORTx_TCLKDIV ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░). ąöą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖą╣ ą▓ąŠ ą▓čüąĄčģ ą┤čĆčāą│ąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPORT, ąĘą░ą┐čĆąĄčéąĖč鹥 čüąĮą░čćą░ą╗ą░ SPORT ąŠčćąĖčüčéą║ąŠą╣ TSPEN ą▓ SPORTx_TCR1 ąĖ/ąĖą╗ąĖ RSPEN ą▓ SPORTx_RCR1.

ąŻ ą║ą░ąČą┤ąŠą│ąŠ SPORT ąĄčüčéčī čüą▓ąŠą╣ čüąŠą▒čüčéą▓ąĄąĮąĮčŗą╣ ąĮą░ą▒ąŠčĆ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą▒čāč乥čĆąŠą▓ ą┤ą░ąĮąĮčŗčģ. ąŁčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąŠą┐ąĖčüą░ąĮčŗ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą▓ ą┐ąŠčüą╗ąĄą┤čāčÄčēąĖčģ čüąĄą║čåąĖčÅčģ. ąÆčüąĄ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆąŠą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüąŠčüč鹊čÅąĮąĖčÅ SPORT čÅą▓ą╗čÅčÄčéčüčÅ ą░ą║čéąĖą▓ąĮčŗą╝ąĖ, ąĄčüą╗ąĖ ąĮąĄ čāą║ą░ąĘą░ąĮąŠ ąŠą▒čĆą░čéąĮąŠąĄ.

ąŚą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆčŗ ąĖ čŹčäč乥ą║čéąĖą▓ąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░. ąÜąŠą│ą┤ą░ SPORT ąĘą░ą┐čĆąĄčēąĄąĮ (ąŠčćąĖčēąĄąĮčŗ TSPEN ąĖ RSPEN), ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SPORT ą▓ąĮčāčéčĆąĄąĮąĮąĄ ąĘą░ą▓ąĄčĆčłą░čÄčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖčÄ čåąĖą║ą╗ą░ SCLK, ą▓ ą║ąŠč鹊čĆąŠą╝ ąŠąĮąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąĖ, ąĖ čĆąĄą│ąĖčüčéčĆ ą▓čŗčćąĖčéčŗą▓ą░ąĄčéčüčÅ ąŠą▒čĆą░čéąĮąŠ ą▓ąĮąŠą▓čī ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĮą░ čüą╗ąĄą┤čāčÄčēąĄą╝ čåąĖą║ą╗ąĄ.

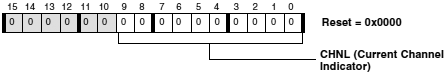

ąÜąŠą│ą┤ą░ SPORT čĆą░ąĘčĆąĄčłąĄąĮ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ TSPEN) ąĖą╗ąĖ ą┐čĆąĖąĄą╝ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ RSPEN), ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čĆąĄą│ąĖčüčéčĆ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPORT ąĘą░ą┐čĆąĄčēąĄąĮą░ ąĘą░ą┐ąĖčüčī (ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ SPORTx_RCLKDIV, SPORTx_TCLKDIV ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░ ą▓ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ). ąŚą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SPORTx_TX ą▓čüąĄą│ą┤ą░ čĆą░ąĘčĆąĄčłąĄąĮčŗ; čĆąĄą│ąĖčüčéčĆčŗ SPORTx_RX, SPORTx_CHNL ąĖ SPORTx_STAT čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ.

ą¤ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą▓ čĆąĄą│ąĖčüčéčĆ SPORT, ą║ąŠą│ą┤ą░ SPORT ąĘą░ą┐čĆąĄčēąĄąĮ, ą╗čÄą▒čŗąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▒ąĖč鹊ą▓ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čĆąĄąČąĖą╝ą░ ą▓čüčéčāą┐ą░čÄčé ą▓ čüąĖą╗čā č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ SPORT ą▒čāą┤ąĄčé čüąĮąŠą▓ą░ čĆą░ąĘčĆąĄčłąĄąĮ.

ąæąŠą╗čīčłąĖąĮčüčéą▓ąŠ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ąĖąĘą╝ąĄąĮąĄąĮčŗ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ SPORT ąĘą░ą┐čĆąĄčēąĄąĮ (TSPEN/RSPEN = 0). ąśąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čüčéčāą┐čÅčé ą▓ čüąĖą╗čā č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ čĆą░ą▒ąŠčéčŗ SPORT. ąśčüą║ą╗čÄč湥ąĮąĖąĄ ąĖąĘ čŹč鹊ą│ąŠ ą┐čĆą░ą▓ąĖą╗ą░ 0 čĆąĄą│ąĖčüčéčĆčŗ TCLKDIV/RCLKDIV ąĖ čĆąĄą│ąĖčüčéčĆčŗ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░.

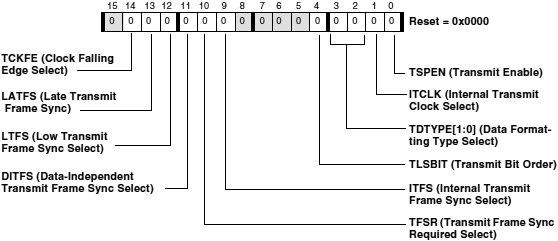

ą×čüąĮąŠą▓ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą╣ čćą░čüčéąĖ ą║ą░ąČą┤ąŠą│ąŠ SPORT, ąĮą░čüčéčĆą░ąĖą▓ą░čÄčēąĖąĄ ą┐ąĄčĆąĄą┤ą░čćčā, čŹč鹊 čĆąĄą│ąĖčüčéčĆčŗ SPORTx_TCR1 ąĖ SPORTx_TCR2.

SPORT čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā, ąĄčüą╗ąĖ ą▒ąĖčé 0 (TSPEN) čĆąĄą│ąĖčüčéčĆą░ SPORTx_TCR1 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ą╗ąĖą▒ąŠ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝, ą╗ąĖą▒ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čüą▒čĆąŠčüąŠą╝, čćč鹊 ąĘą░ą┐čĆąĄčēą░ąĄčé ą▓čüąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ SPORT.

ąÜąŠą│ą┤ą░ SPORT čĆą░ąĘčĆąĄčłąĄąĮ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (TSPEN čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ), ąĘą░ą┐ąĖčüąĖ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPORT ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮčŗ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ SPORTx_TCLKDIV ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░. ąŚą░ą┐ąĖčüąĖ ą▓ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄ ą┤ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ąÜąŠą│ą┤ą░ SPORT čĆą░ąĘčĆąĄčłąĄąĮ, SPORTx_TCR1 ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą▒ąĖčéą░ 0 (TSPEN). ąØą░ą┐čĆąĖą╝ąĄčĆ:

write (SPORTx_TCR1, 0x0001); /* SPORT TX čĆą░ąĘčĆąĄčłąĄąĮ */

write (SPORTx_TCR1, 0xFF01); /* ąŠą┐ąĄčĆą░čåąĖčÅ ą▒čāą┤ąĄčé ą┐čĆąŠąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░ąĮą░,

ąĖ ąĮąĄ ą┤ą░čüčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░ */

write (SPORTx_TCR1, 0xFFF0); /* SPORT ąĘą░ą┐čĆąĄčēąĄąĮ, SPORTx_TCR1

ą▓čüąĄ ąĄčēąĄ čĆą░ą▓ąĄąĮ 0x0000 */

ąÉą┤čĆąĄčüą░ ą┤ą╗čÅ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ SPORT:

SPORT0_TCR1 ŌĆō 0xFFC0 0800 SPORT0_TCR2 ŌĆō 0xFFC0 0804

SPORT1_TCR1 ŌĆō 0xFFC0 0900 SPORT1_TCR2 ŌĆō 0xFFC0 0904

SPORT2_TCR1 ŌĆō 0xFFC0 2500 SPORT2_TCR2 ŌĆō 0xFFC0 2504

SPORT3_TCR1 ŌĆō 0xFFC0 2600 SPORT3_TCR2 ŌĆō 0xFFC0 2604

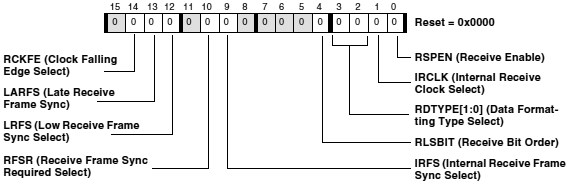

ąĀąĖčü. 13-4. SPORTx Transmit Configuration 1 Register.

ŌĆó Transmit Enable (TSPEN). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé, čĆą░ąĘčĆąĄčłąĄąĮ ą╗ąĖ SPORT ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (ąĄčüą╗ąĖ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ ąČąĄ ąĘą░ą┐čĆąĄčēąĄąĮ (ąĄčüą╗ąĖ ąŠčćąĖčēąĄąĮ).

ąŻčüčéą░ąĮąŠą▓ą║ą░ TSPEN ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠą╝čā ą▓čŗčüčéą░ą▓ą╗ąĄąĮąĖčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ SPORT TX, čćč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐čāčüč鹊čéčā ą▒čāč乥čĆą░ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čćč鹊 ąĄą│ąŠ ąĮčāąČąĮąŠ ąĘą░ą┐ąŠą╗ąĮąĖčéčī. ą×ą▒čŗčćąĮąŠ čŹč鹊 ąČąĄą╗ą░ąĄą╝ąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐ąŠąĘą▓ąŠą╗ąĖčé čåąĄąĮčéčĆą░ą╗ąĖąĘąŠą▓ą░čéčī ą║ąŠą┤ ąĘą░ą┐ąĖčüąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ TX (ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüąŠą║čĆą░čēąĄąĮąĮąŠ ąĮą░ąĘčŗą▓ą░ąĄčéčüčÅ ISR, ąŠčé čüąŠą║čĆą░čēąĄąĮąĖčÅ interrupt service routine). ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ TSPEN ą┤ąŠą╗ąČąĄąĮ čüąĮą░čćą░ą╗ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ISR, čćč鹊ą▒čŗ ą▒čŗčéčī ą│ąŠč鹊ą▓čŗą╝ ą║ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ TX.

ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ DMA, čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ DMA ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą║ąŠčĆčĆąĄą║čéąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąŠ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ TSPEN. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▓čüąĄ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DMA ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ TSPEN.

ą×čćąĖčüčéą║ą░ TSPEN ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 SPORT ąŠčüčéą░ąĮąŠą▓ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ą▓čŗą▓ąŠą┤ąŠą╝ ą┤ą░ąĮąĮčŗčģ, ą│ąĄąĮąĄčĆą░čåąĖčÄ čéą░ą║č鹊ą▓ TSCLK ąĖ čüąĖą│ąĮą░ą╗ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░; čŹč鹊 čéą░ą║ąČąĄ ą▓čŗą║ą╗čÄčćąĖčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüčģąĄą╝čŗ SPORT. ąÆ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą│ą┤ąĄ čüą┤ąĄą╗ą░ąĮ ą░ą║čåąĄąĮčé ąĮą░ čüąĮąĖąČąĄąĮąĖąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ąČąĖąĘąĮčī ą▒ą░čéą░čĆąĄąĖ ą╝ąŠąČąĮąŠ ą┐čĆąŠą┤ą╗ąĖčéčī, ąĄčüą╗ąĖ ąŠčćąĖčēą░čéčī TSPEN ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ SPORT ąĮąĄ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮ.

ąÆčüąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ SPORT ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ TSPEN. ąóąĖą┐ąĖčćąĮčŗą╣ ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ SPORT čüąĮą░čćą░ą╗ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą▓čüąĄ ą┐ąŠą╗čÅ ąĖ ą▒ąĖčéčŗ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓ (ą▓ą║ą╗čÄčćą░čÅ DMA, ąĄčüą╗ąĖ čŹč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ). ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čłą░ą│ ą▓ ą║ąŠą┤ąĄ - ąĘą░ą┐ąĖčüčī ą▓ SPORTx_TCR1 čüąŠ ą▓čüąĄą╝ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗą╝ąĖ ą▒ąĖčéą░ą╝ąĖ, ą▓ą║ą╗čÄčćą░čÅ TSPEN.

ŌĆó Internal Transmit Clock Select (ITCLK). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čéą░ą║čéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ (ąĄčüą╗ąĖ ITCLK čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖąĄ čéą░ą║čéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ (ąĄčüą╗ąĖ ITCLK ąŠčćąĖčēąĄąĮ) ąĮą░ ą▓čŗą▓ąŠą┤ąĄ TSCLK. ąŚąĮą░č湥ąĮąĖąĄ TCLKDIV MMR ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ą▓ąĮąĄčłąĮčÅčÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░.

ŌĆó Data Formatting Type Select (TDTYPE[1:0]). ąöą▓ą░ ą▒ąĖčéą░ TDTYPE čāą║ą░ąĘčŗą▓ą░čÄčé č乊čĆą╝ą░čéčŗ ą┤ą░ąĮąĮčŗčģ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ąŠą┤ąĮąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ ąĖ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ.

00 - ą×ą▒čŗčćąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ.

01 - ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ.

10 - ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ╬╝-law.

11 - ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ A-law.

ŌĆó Bit Order Select (TLSBIT). ąæąĖčé TLSBIT ą▓čŗą▒ąĖčĆą░ąĄčé ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ č湥čĆąĄąĘ SPORT (ą║ą░ą║ąŠą╣ ą▒ąĖčé ąĖą┤ąĄčé ą┐ąĄčĆą▓čŗą╝ - MSB ąĖą╗ąĖ LSB).

ŌĆó Serial Word Length Select (SLEN). ąöą╗ąĖąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą▓ ą║ą░ąČą┤ąŠą╝ čüą╗ąŠą▓ąĄ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą╝ č湥čĆąĄąĘ SPORT) ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐čāč鹥ą╝ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖčÅ 1 ą║ ąĘąĮą░č湥ąĮąĖčÄ ą┐ąŠą╗čÅ SLEN:

Serial Word Length = SLEN + 1

ą¤ąŠą╗ąĄ SLEN ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 2 ą┤ąŠ 31; 0 ąĖ 1 ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą┐ąŠą╗čÅ. ąóčĆąĖ ąŠą▒čēąĖąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┤ą╗čÅ ą┐ąŠą╗čÅ SLEN čŹč鹊 15 (ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąŠą╗ąĮąŠą│ąŠ 16-ą▒ąĖčéąĮąŠą│ąŠ čüą╗ąŠą▓ą░, 7 (ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ 8 ą▒ąĖčé ą▒ą░ą╣čéą░) ąĖ 23 (ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ 24 ą▒ąĖčéąĮąŠą│ąŠ čüą╗ąŠą▓ą░). ą¤čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ąĘą░ą│čĆčāąĘąĖčéčī 16- ąĖą╗ąĖ 32-ą▒ąĖčéąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ą▓ ą▒čāč乥čĆ ą┐ąĄčĆąĄą┤ą░čćąĖ č湥čĆąĄąĘ DMA ąĖą╗ąĖ ąĖąĮčüčéčĆčāą║čåąĖčÄ ąĘą░ą┐ąĖčüąĖ MMR; ą┐ąŠą╗ąĄ SLEN ą│ąŠą▓ąŠčĆąĖčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā SPORT, čüą║ąŠą╗čīą║ąŠ čŹčéąĖčģ ą▒ąĖčé ą▓čŗą┤ą▓ąĖą│ą░čéčī ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą╗ąĖąĮą║. ą¤ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ą┐ąŠčĆčé ą┐ąĄčĆąĄą┤ą░ąĄčé ą▒ąĖčéčŗ [SLEN:0] ąĖąĘ ą▒čāč乥čĆą░ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąĪąĖą│ąĮą░ą╗ frame sync čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ SPORTx_TFSDIV ąĖ SPORTx_RFSDIV, ąĮąĄ SLEN. ąöą╗čÅ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖą╝ą┐čāą╗čīčüą░ frame sync ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą░ą╣čéą░, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ą┤ąĄą╗ąĖč鹥ą╗čī ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖą╝ą┐čāą╗čīčüą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ (frame sync divider) ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ; čāčüčéą░ąĮąŠą▓ą║ą░ SLEN ą▓ ąĘąĮą░č湥ąĮąĖąĄ 7 ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖą╝ą┐čāą╗čīčüą░ frame sync ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą░ą╣čéą░.

ŌĆó Internal Transmit Frame Sync Select (ITFS). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą╗ąĖ SPORT ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗ TFS (ąĄčüą╗ąĖ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ TFS (ąĄčüą╗ąĖ ąŠčćąĖčēąĄąĮ).

ŌĆó Transmit Frame Sync Required Select (TFSR). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé, čéčĆąĄą▒čāąĄčé ą╗ąĖ SPORT (ąĄčüą╗ąĖ ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ ąĮąĄ čéčĆąĄą▒čāąĄčé (ąĄčüą╗ąĖ ąŠčćąĖčēąĄąĮ) ą┐ąĄčĆąĄą┤ą░čćąĖ frame sync ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ.

ąæąĖčé TFSR ąŠą▒čŗčćąĮąŠ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ąŠ ą▓čĆąĄą╝čÅ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ SPORT. ąśą╝ą┐čāą╗čīčü frame sync ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą┐ąŠą╝ąĄčéą║ąĖ ąĮą░čćą░ą╗ą░ ą║ą░ąČą┤ąŠą│ąŠ čüą╗ąŠą▓ą░ ąĖą╗ąĖ ą┐ą░ą║ąĄčéą░ ą┤ą░ąĮąĮčŗčģ, ąĖ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ąŠ čüąĖčüč鹥ą╝ ąĮčāąČą┤ą░čÄčéčüčÅ ą▓ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╝ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĖ frame sync.

ŌĆó Data-Independent Transmit Frame Sync Select (DITFS). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé, ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ą╗ąĖ SPORT ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ ąŠčé ą┤ą░ąĮąĮčŗčģ TFS (čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüčŗ čüą╗ąĄą┤čāčÄčé čü ą▓čŗą▒čĆą░ąĮąĮčŗą╝ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą╝) ąĖą╗ąĖ ąĘą░ą▓ąĖčüąĖą╝čŗą╣ ąŠčé ą┤ą░ąĮąĮčŗčģ TFS (čüąĖąĮčģčĆąŠąĖą╝ą┐čāą╗čīčüčŗ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ, ą║ąŠą│ą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą┐čĆąĖčüčāčéčüčéą▓čāčÄčé ą▓ SPORTx_TX) ą┤ą╗čÅ čüą╗čāčćą░čÅ, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ frame sync (ITFS = 1). ąæąĖčé DITFS ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮ ą▓ąĮąĄčłąĮąĖą╣ čüąĖą│ąĮą░ą╗ frame sync.

ąÜą░ą║ čāąČąĄ čāą┐ąŠą╝ąĖąĮą░ą╗ąŠčüčī, ąĖą╝ą┐čāą╗čīčü frame sync ą┐ąŠą╝ąĄčćą░ąĄčé ąĮą░čćą░ą╗ąŠ ą║ą░ąČą┤ąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ąĢčüą╗ąĖ ą▒ąĖčé DITFS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ąĖą╝ą┐čāą╗čīčü frame sync ą▓čŗą┤ą░ąĄčéčüčÅ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé č鹊ą│ąŠ, ą▒čŗą╗ ą╗ąĖ ąĘą░ą│čĆčāąČąĄąĮ čĆąĄą│ąĖčüčéčĆ SPORTx_TX ąĖą╗ąĖ ąĮąĄčé; ąĄčüą╗ąĖ ąČąĄ DITFS ąŠčćąĖčēąĄąĮ, ąĖą╝ą┐čāą╗čīčü frame sync ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ ąĘą░ą│čĆčāąČąĄąĮ čĆąĄą│ąĖčüčéčĆ ą┤ą░ąĮąĮčŗčģ SPORTx_TX. ąĢčüą╗ąĖ ą┐čĆąĖąĄą╝ąĮąĖą║ čéčĆąĄą▒čāąĄčé čĆąĄą│čāą╗čÅčĆąĮčŗčģ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ ąĖą╝ą┐čāą╗čīčüąŠą▓ frame sync, č鹊 DITFS ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ą┤ąŠą╗ąČąĄąĮ čüą╗ąĄą┤ąĖčéčī ąĘą░ ąĘą░ą│čĆčāąĘą║ąŠą╣ ą▓ ąĮčāąČąĮąŠąĄ ą▓čĆąĄą╝čÅ čĆąĄą│ąĖčüčéčĆą░ SPORTx_TX. ąĢčüą╗ąĖ čĆąĄą│ąĖčüčéčĆ ą┤ąŠą┐čāčüą║ą░ąĄčé ą┐čĆąŠąĖąĘą▓ąŠą╗čīąĮąŠ ą┐ąŠąĘą┤ąĮąĄąĄ ą┐ąŠčÅą▓ą╗ąĄąĮąĖąĄ ąĖą╝ą┐čāą╗čīčüąŠą▓ frame sync, DITFS ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąŠčćąĖčēąĄąĮ ą┤ą╗čÅ ą┐čĆąĄą┤ąŠčéą▓čĆą░čēąĄąĮąĖčÅ ą┐ąŠą▓č鹊čĆąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ čüčéą░čĆčŗčģ ą┤ą░ąĮąĮčŗčģ SPORT, ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, ąĄčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąŠą┐ąŠąĘą┤ą░ą╗ čü ąĘą░ą│čĆčāąĘą║ąŠą╣ čĆąĄą│ąĖčüčéčĆą░ SPORTx_TX.

ŌĆó Low Transmit Frame Sync Select (LTFS). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé ą░ą║čéąĖą▓ąĮčŗą╣ 0 ą┤ą╗čÅ TFS (ąĄčüą╗ąĖ ą▒ąĖčé LTFS) ąĖą╗ąĖ ą░ą║čéąĖą▓ąĮčŗą╣ 1 ą┤ą╗čÅ TFS (ąĄčüą╗ąĖ LTFS ąŠčćąĖčēąĄąĮ).

ŌĆó Late Transmit Frame Sync (LATFS). ąŁč鹊čé ą▒ąĖčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé ą┐ąŠąĘą┤ąĮąĖąĄ ąĖą╝ą┐čāą╗čīčüčŗ frame sync (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ čĆą░ąĮąĮąĖąĄ ąĖą╝ą┐čāą╗čīčüčŗ frame sync (ąĄčüą╗ąĖ ąŠčćąĖčēąĄąĮ).

ŌĆó Clock Drive/Sample Edge Select (TCKFE). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé, ą┐ąŠ ą║ą░ą║ąŠą╝čā čüčĆąĄąĘčā čüąĖą│ąĮą░ą╗ą░ TCLKx SPORT čāą┐čĆą░ą▓ą╗čÅąĄčé ą┤ą░ąĮąĮčŗą╝ąĖ ą┤ą╗čÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░ čüąĖą│ąĮą░ą╗ąŠą▓ frame sync, ąĖ ą┤ą╗čÅ ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ frame sync čüąĮą░čĆčāąČąĖ. ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą┤ą░ąĮąĮčŗąĄ ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ą▓ąĮčāčéčĆąĖ čüąĖą│ąĮą░ą╗čŗ frame syncs čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā, ąĖ ą▓ąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ frame sync ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ. ąĢčüą╗ąĖ ą▒ąĖčé ąŠčćąĖčēąĄąĮ, č鹊 ą┤ą░ąĮąĮčŗąĄ ąĖ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ą▓ąĮčāčéčĆąĖ čüąĖą│ąĮą░ą╗čŗ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ, ąĖ ą▓ąĮąĄčłąĮąĖąĄ čüąĖą│ąĮą░ą╗čŗ frame sync ą░ąĮą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā.

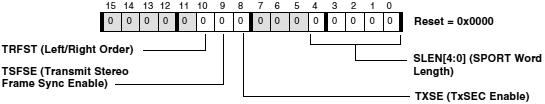

ąĀąĖčü. 13-5. SPORTx Transmit Configuration 2 Register.

ŌĆó SLEN[4:0]. ą¤ąŠą╗ąĄ, ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčēąĄąĄ ą┤ą╗ąĖąĮčā čüą╗ąŠą▓ą░. ąŚąĮą░č湥ąĮąĖčÅ 00000 ąĖ 00001 ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗ, ąŠčüčéą░ą╗čīąĮčŗąĄ ąĘąĮą░č湥ąĮąĖčÅ ąĘą░ą┤ą░čÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą▓ čüą╗ąŠą▓ąĄ +1.

ŌĆó TxSec Enable (TXSE). ąŁč鹊čé ą▒ąĖčé (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) čĆą░ąĘčĆąĄčłą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ą▓č鹊čĆąĖčćąĮąŠą╣ čćą░čüčéąĖ ą┤ą░ąĮąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ ą┐ąŠčĆčéą░.

ŌĆó Stereo Serial Enable (TSFSE). ąŁč鹊čé ą▒ąĖčé (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) čĆą░ąĘčĆąĄčłą░ąĄčé čĆąĄąČąĖą╝ čĆą░ą▒ąŠčéčŗ stereo. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, čĆą░ąĘčĆąĄčłą░čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ąĖ čüąĖą│ąĮą░ą╗ąŠą▓ frame sync.

ŌĆó Left/Right Order (TRFST). ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą▓ čĆąĄąČąĖą╝ąĄ stereo ą┐čĆą░ą▓čŗą╣ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą┐ąĄčĆą▓čŗą╝. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, čéą░ą║ čćč鹊 ą┐ąĄčĆą▓čŗą╝ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ą╗ąĄą▓čŗą╣ ą║ą░ąĮą░ą╗.

ą×čüąĮąŠą▓ąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ąĮąŠą╣ čćą░čüčéąĖ ą║ą░ąČą┤ąŠą│ąŠ SPORT, ąĮą░čüčéčĆą░ąĖą▓ą░čÄčēąĖąĄ ą┐čĆąĖąĄą╝, čŹč鹊 čĆąĄą│ąĖčüčéčĆčŗ SPORTx_RCR1 ąĖ SPORTx_RCR2.

SPORT čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ ąĮą░ ą┐čĆąĖąĄą╝, ąĄčüą╗ąĖ ą▒ąĖčé 0 (RSPEN) čĆąĄą│ąĖčüčéčĆą░ SPORTx_RCR1 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1. ąŁč鹊čé ą▒ąĖčé ąŠčćąĖčēą░ąĄčéčüčÅ ą╗ąĖą▒ąŠ ą░ą┐ą┐ą░čĆą░čéąĮčŗą╝, ą╗ąĖą▒ąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╝ čüą▒čĆąŠčüąŠą╝, čćč鹊 ąĘą░ą┐čĆąĄčēą░ąĄčé ą▓ąĄčüčī ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ SPORT.

ąÜąŠą│ą┤ą░ SPORT čĆą░ąĘčĆąĄčłąĄąĮ ąĮą░ ą┐čĆąĖąĄą╝ (RSPEN čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ), č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPORT ąĮąĄą╗čīąĘčÅ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ SPORTx_RCLKDIV ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą▓čŗą▒ąŠčĆą░ ą║ą░ąĮą░ą╗ą░ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░. ąŚą░ą┐ąĖčüąĖ ą▓ ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄ ą┤ą░čÄčé ąĮąĖą║ą░ą║ąŠą│ąŠ čŹčäč乥ą║čéą░. ą¤ąŠą║ą░ SPORT čĆą░ąĘčĆąĄčłąĄąĮ, SPORTx_RCR1 ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ, ąĘą░ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝ ą▒ąĖčéą░ 0 (RSPEN). ąØą░ą┐čĆąĖą╝ąĄčĆ:

write (SPORTx_RCR1, 0x0001); /* SPORT RX čĆą░ąĘčĆąĄčłąĄąĮ */

write (SPORTx_RCR1, 0xFF01); /* ą┤ąĄą╣čüčéą▓ąĖąĄ ąĖą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ, ąĖ ąĮąĄ ą┤ą░ąĄčé čŹčäč乥ą║čéą░ */

write (SPORTx_RCR1, 0xFFF0); /* SPORT ąĘą░ą┐čĆąĄčēąĄąĮ, SPORTx_RCR1 ą▓čüąĄ ąĄčēąĄ

čĆą░ą▓ąĄąĮ 0x0000 */

ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ąĮą░čüčéčĆąŠą╣ą║ąĖ ą┐čĆąĖąĄą╝ą░ SPORT:

SPORT0_RCR1 ŌĆō 0xFFC0 0820 SPORT0_RCR2 ŌĆō 0xFFC0 0824

SPORT1_RCR1 ŌĆō 0xFFC0 0920 SPORT1_RCR2 ŌĆō 0xFFC0 0924

SPORT2_RCR1 ŌĆō 0xFFC0 2520 SPORT2_RCR2 ŌĆō 0xFFC0 2524

SPORT3_RCR1 ŌĆō 0xFFC0 2620 SPORT3_RCR2 ŌĆō 0xFFC0 2624

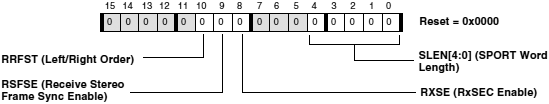

ąĀąĖčü. 13-6. SPORTx Receive Configuration 1 Register.

ŌĆó Receive Enable (RSPEN). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé, ą▒čāą┤ąĄčé ą╗ąĖ SPORT čĆą░ąĘčĆąĄčłąĄąĮ ąĮą░ ą┐čĆąĖąĄą╝ (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ (ąĄčüą╗ąĖ ąŠčćąĖčēąĄąĮ). ąŻčüčéą░ąĮąŠą▓ą║ą░ RSPEN ą▓ą║ą╗čÄčćą░ąĄčé SPORT ąĖ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ąŠčåąĖčäčĆąŠą▓ą║ąĄ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ ąĖ čĆą░ą▒ąŠčéčā čāąĘą╗ąŠą▓ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ąĖ čüąĖą│ąĮą░ą╗ą░ frame sync ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ąĮą░čüčéčĆąŠą╣ą║ą░ą╝ąĖ.

ąŻčüčéą░ąĮąŠą▓ą║ą░ RSPEN čĆą░ąĘčĆąĄčłą░ąĄčé ą┐čĆąĖąĄą╝ąĮąĖą║ SPORTx, ą║ąŠč鹊čĆčŗą╣ ą╝ąŠąČąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPORTx RX. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ą║ąŠą┤ ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ RSPEN ą┤ąŠą╗ąČąĄąĮ čüąĮą░čćą░ą╗ą░ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░čéčī ISR ąĖ/ąĖą╗ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ DMA (ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé č鹊ą│ąŠ ą║ą░ą║ą░čÅ čüčģąĄą╝ą░ ą┐čĆąĖąĄą╝ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ), čćč鹊ą▒čŗ ą▒čŗčéčī ą│ąŠč鹊ą▓čŗą╝ ą║ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ RX. ąŻčüčéą░ąĮąŠą▓ą║ą░ RSPEN čéą░ą║ąČąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąĘą░ą┐čĆąŠčüčŗ DMA, ąĄčüą╗ąĖ DMA čĆą░ąĘčĆąĄčłąĄąĮ ąĖ ą┤ą░ąĮąĮčŗąĄ ą▒čŗą╗ąĖ ą┐čĆąĖąĮčÅčéčŗ. ąŻčüčéą░ąĮąŠą▓ąĖč鹥 ą▓čüąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ DMA ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ RSPEN. ą×čćąĖčüčéą║ą░ RSPEN ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ č鹊ą╝čā, čćč鹊 SPORT čüčĆą░ąĘčā ąŠčüčéą░ąĮąŠą▓ąĖčé ą┐čĆąĖąĄą╝ ą┤ą░ąĮąĮčŗčģ; ąŠčćąĖčüčéą║ą░ čŹč鹊ą│ąŠ ą▒ąĖčéą░ čéą░ą║ąČąĄ ą▓čŗą║ą╗čÄčćąĖčé ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čüčģąĄą╝čŗ SPORT. ąÆ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ, ą│ą┤ąĄ čüą┤ąĄą╗ą░ąĮ ą░ą║čåąĄąĮčé ąĮą░ čüąĮąĖąČąĄąĮąĖąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ąČąĖąĘąĮčī ą▒ą░čéą░čĆąĄąĖ ą╝ąŠąČąĮąŠ ą┐čĆąŠą┤ą╗ąĖčéčī, ąĄčüą╗ąĖ ąŠčćąĖčēą░čéčī RSPEN ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ SPORT ąĮąĄ ąĘą░ą┤ąĄą╣čüčéą▓ąŠą▓ą░ąĮ.

ąÆčüąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ SPORT ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮčŗ ą┐ąĄčĆąĄą┤ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ RSPEN. ąóąĖą┐ąĖčćąĮčŗą╣ ą║ąŠą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĖ SPORT čüąĮą░čćą░ą╗ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé ą▓čüąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ, ą▓ą║ą╗čÄčćą░čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ DMA, ąĄčüą╗ąĖ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ. ą¤ąŠčüą╗ąĄą┤ąĮąĖą╣ čłą░ą│ ą▓ čĆą░ą▒ąŠč鹥 ą║ąŠą┤ą░ - ąĘą░ą┐ąĖčüčī ą▓ SPORTx_RCR1 ą▓čüąĄčģ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗčģ ą▒ąĖčé, ą▓ą║ą╗čÄčćą░čÅ čāčüčéą░ąĮąŠą▓ą║čā RSPEN.

ŌĆó Internal Receive Clock Select (IRCLK). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▒ąĖčé ą┐čĆąĖąĄą╝ą░ (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ (ąĄčüą╗ąĖ ąŠčćąĖčēąĄąĮ). ąŚąĮą░č湥ąĮąĖąĄ RCLKDIV MMR ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮąŠ ą▓ąĮąĄčłąĮąĄąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ.

ŌĆó Data Formatting Type Select (RDTYPE[1:0]). ąöą▓ą░ ą▒ąĖčéą░ RDTYPE ąĘą░ą┤ą░čÄčé ąŠą┤ąĖąĮ ąĖąĘ 4 č乊čĆą╝ą░č鹊ą▓ ą┤ą░ąĮąĮčŗčģ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┤ą╗čÅ ąŠą┤ąĮąŠą║ą░ąĮą░ą╗čīąĮąŠą╣ ąĖ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ.

00 - ą×ą▒čŗčćąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ (Zero-fill).

01 - Sign-extended.

10 - ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ╬╝-law.

11 - ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ A-law.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą┐ąŠą╗ąĄ RDTYPE čāą┤ąŠą▒ąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖčÅ čüčćąĖčéčŗą▓ą░ąĄą╝ąŠą│ąŠ ąĖąĘ SPORT ąĘąĮą░č湥ąĮąĖčÅ čüą╗ąŠą▓ą░ ą║ą░ą║ čćąĖčüą╗ąŠ ą▓ č乊čĆą╝ą░č鹥 ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĘąĮą░ą║ą░ čü ą┤ą▓ąŠąĖčćąĮčŗą╝ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄą╝ ą┤ąŠ 2 (čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝čŗą╣ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą║ąŠą┤), ąĄčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č乊čĆą╝ą░čé 01 - Sign-extended. ąŁč鹊 čüčéą░ąĮą┤ą░čĆčéąĮčŗą╣ č乊čĆą╝ą░čé ą┤ą╗čÅ ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮčŗčģ čćąĖčüąĄą╗, ą║ąŠč鹊čĆčŗą╣ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą▓ąŠ ą╝ąĮąŠą│ąĖčģ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ ąÉą”ą¤. ąØą░ą┐čĆąĖą╝ąĄčĆ, 18-ą▒ąĖčéąĮąŠąĄ ąÉą”ą¤ AD7691 [6] ą║ą░ą║ čĆą░ąĘ ąĖčüą┐ąŠą╗čīąĘčāąĄčé čéą░ą║ąŠą╣ č乊čĆą╝ą░čé ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ čĆąĄąĘčāą╗čīčéą░čéą░ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ, ą┐ąŠčŹč鹊ą╝čā čāčüčéą░ąĮąŠą▓ą║ą░ ą┐ąŠą╗čÅ RDTYPE ą▓ ąĘąĮą░č湥ąĮąĖąĄ 01 ąĖąĘą▒ą░ą▓ą╗čÅąĄčé ąŠčé ą╗ąĖčłąĮąĖčģ ą║ąŠą╝ą░ąĮą┤ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ ą▓čŗą▒ąŠčĆą║ąĖ ąÉą”ą¤, čüčĆą░ąĘčā ą┤ą░ą▓ą░čÅ ąĮčāąČąĮčŗą╣ č乊čĆą╝ą░čé čćąĖčüą╗ą░. ąó. ąĄ. 18-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, čüčćąĖčéą░ąĮąĮąŠąĄ ąĖąĘ ąÉą”ą¤, ą▒čāą┤ąĄčé čüčĆą░ąĘčā ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąŠ ą▓ 32-ą▒ąĖčéąĮąŠąĄ ą│ąŠč鹊ą▓ąŠąĄ čćąĖčüą╗ąŠ čüąŠ ąĘąĮą░ą║ąŠą╝ čéąĖą┐ą░ int.

ŌĆó Bit Order Select (RLSBIT). ąæąĖčé RLSBIT ą▓čŗą▒ąĖčĆą░ąĄčé ą┐ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé, ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗčģ SPORT.

ŌĆó Internal Receive Frame Sync Select (IRFS). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé, ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą╗ąĖ SPORT ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ RFS (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ ą▓ąĮąĄčłąĮąĖą╣ RFS (ąĄčüą╗ąĖ ąŠčćąĖčēąĄąĮ).

ŌĆó Receive Frame Sync Required Select (RFSR). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé, čéčĆąĄą▒čāąĄčé ą╗ąĖ SPORT (ąĄčüą╗ąĖ RFSR čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) ąĖą╗ąĖ ąĮąĄ čéčĆąĄą▒čāąĄčé (ąĄčüą╗ąĖ RFSR ąŠčćąĖčēąĄąĮ) ą┐ąŠą╗čāč湥ąĮąĖčÅ frame sync ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ.

ŌĆó Low Receive Frame Sync Select (LRFS). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé ą░ą║čéąĖą▓ąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī 0 ą┤ą╗čÅ RFS (ąĄčüą╗ąĖ LRFS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ), ąĖą╗ąĖ ą░ą║čéąĖą▓ąĮčŗą╣ 1 ą┤ą╗čÅ RFS (ąĄčüą╗ąĖ LRFS ąŠčćąĖčēąĄąĮ).

ŌĆó Late Receive Frame Sync (LARFS). ąŁč鹊čé ą▒ąĖčé ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčé ą┐ąŠąĘą┤ąĮąĖą╣ frame sync (ąĄčüą╗ąĖ LARFS čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ), ąĖą╗ąĖ čĆą░ąĮąĮąĖą╣ frame sync (ąĄčüą╗ąĖ LARFS ąŠčćąĖčēąĄąĮ).

ŌĆó Clock Drive/Sample Edge Select (RCKFE). ąŁč鹊čé ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčé, ą║ą░ą║ąŠą╣ ą┐ąĄčĆąĄą┐ą░ą┤ čüąĖą│ąĮą░ą╗ą░ RSCLK ąĖčüą┐ąŠą╗čīąĘčāąĄčé SPORT ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą┤ą░ąĮąĮčŗčģ, ą║ą░ą║ ą┤ą╗čÅ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ą▓ąĮčāčéčĆąĖ čüąĖą│ąĮą░ą╗ąŠą▓ čäčĆąĄą╣ą╝ą░, čéą░ą║ ąĖ ą┐ąŠčüčéčāą┐ą░čÄčēąĖčģ čüąĮą░čĆčāąČąĖ. ąĢčüą╗ąĖ RCKFE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ą▓ąĮčāčéčĆąĖ čüąĖą│ąĮą░ą╗čŗ frame sync čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā, ąĖ ą┤ą░ąĮąĮčŗąĄ ąĖ ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ čüąĮą░čĆčāąČąĖ frame sync ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā. ąĢčüą╗ąĖ RCKFE ąŠčćąĖčēąĄąĮ, č鹊 ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ ą▓ąĮčāčéčĆąĖ frame sync čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ, ąĖ ą┤ą░ąĮąĮčŗąĄ ąĖ ą┐ąŠčüčéčāą┐ą░čÄčēąĖąĄ čüąĮą░čĆčāąČąĖ frame sync ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā.

ąĀąĖčü. 13-7. SPORTx Receive Configuration 2 Register.

ŌĆó Serial Word Length Select (SLEN[4:0]). ąöą╗ąĖąĮą░ čüą╗ąŠą▓ą░ ą▒ąĖčé (ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ąĖčé ą▓ ą║ą░ąČą┤ąŠą╝ čüą╗ąŠą▓ąĄ, ą┐čĆąĖąĮčÅč鹊ą╝ SPORT) ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄą╝ 1 ą║ ąĘąĮą░č湥ąĮąĖčÄ ą┐ąŠą╗čÅ SLEN. ą¤ąŠą╗ąĄ SLEN ą╝ąŠąČąĄčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąŠčé 2 ą┤ąŠ 31; ąĘąĮą░č湥ąĮąĖčÅ 0 ąĖ 1 ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗ ą┤ą╗čÅ čŹč鹊ą│ąŠ ą┐ąŠą╗čÅ.

ąĪąĖą│ąĮą░ą╗ frame sync čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ SPORTx_TFSDIV ąĖ SPORTx_RFSDIV, ąĮąĄ SLEN. ą¦č鹊ą▒čŗ ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ąĖą╝ą┐čāą╗čīčü frame sync ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą░ą╣čéą░ ąĖą╗ąĖ čüą╗ąŠą▓ą░, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ frame sync divider ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ; čāčüčéą░ąĮąŠą▓ą║ą░ SLEN ą▓ 7 ąĮąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ ąĖą╝ą┐čāą╗čīčüą░ frame sync ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ ą▒ą░ą╣čéą░.

ŌĆó RxSec Enable (RXSE). ąŁč鹊čé ą▒ąĖčé (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) čĆą░ąĘčĆąĄčłą░ąĄčé ą▓č鹊čĆąĖčćąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ.

ŌĆó Stereo Serial Enable (RSFSE). ąŁč鹊čé ą▒ąĖčé (ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ) čĆą░ąĘčĆąĄčłą░ąĄčé čĆą░ą▒ąŠčéčā čĆąĄąČąĖą╝ą░ stereo. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, čćč鹊 čĆą░ąĘčĆąĄčłą░ąĄčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ąĖ ą│ąĄąĮąĄčĆą░čåąĖąĖ frame sync.

ŌĆó Left/Right Order (RRFST). ąĢčüą╗ąĖ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą▓ čĆąĄąČąĖą╝ąĄ stereo čüąĮą░čćą░ą╗ą░ ą┐čĆąĖąĮąĖą╝ą░ąĄčéčüčÅ ą┐čĆą░ą▓čŗą╣ ą║ą░ąĮą░ą╗. ą¤ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čŹč鹊čé ą▒ąĖčé ąŠčćąĖčēąĄąĮ, čéą░ą║ čćč鹊 ą┐ąĄčĆą▓čŗą╝ ą▒čāą┤ąĄčé ą┐čĆąĖąĮąĖą╝ą░čéčīčüčÅ ą╗ąĄą▓čŗą╣ ą║ą░ąĮą░ą╗.

[ążąŠčĆą╝ą░čéčŗ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ]

ążąŠčĆą╝ą░čé čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ č湥čĆąĄąĘ SPORT, ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄčéčüčÅ ą║ąŠą╝ą▒ąĖąĮą░čåąĖąĄą╣ ą┐ąŠą╗čÅ SLEN ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐ąŠą╗čÅ SLEN ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░, ą░ čéą░ą║ąČąĄ ą▒ąĖč鹊ą▓ RDTYPE, TDTYPE, RLSBIT ąĖ TLSBIT bits čĆąĄą│ąĖčüčéčĆąŠą▓ SPORTx_TCR1, SPORTx_TCR2, SPORTx_RCR1 ąĖ SPORTx_RCR2.

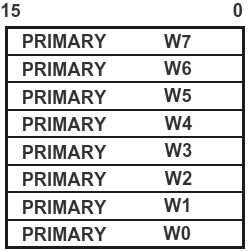

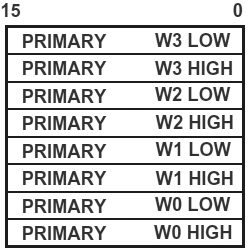

ąĀąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ SPORTx (SPORTx_TX) čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ ąĘą░ą┐ąĖčüčī. ą¦č鹥ąĮąĖąĄ ą┐čĆąĖą▓ąĄą┤ąĄčé ąĄ ąŠčłąĖą▒ą║ąĄ ą┤ąŠčüčéčāą┐ą░ ą║ čłąĖąĮąĄ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (peripheral access bus, PAB). ąŚą░ą┐ąĖčüąĖ ą▓ čŹč鹊čé čĆąĄą│ąĖčüčéčĆ ą┐čĆąĖą▓ąĄą┤čāčé ą║ ąĘą░ą┐ąĖčüčÅą╝ ą▓ FIFO ą┐ąĄčĆąĄą┤ą░čéčćąĖą║ą░. ąĢčüą╗ąĖ FIFO čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ 16 ą▒ąĖčé (ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮąĮą░čÅ ą┤ą╗ąĖąĮą░ čüą╗ąŠą▓ą░ ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮą░ 16 ą▒ąĖčé), č鹊 ąŠąĮ ą▒čāą┤ąĄčé ą│ą╗čāą▒ąĖąĮąŠą╣ ą▓ 8 čÅč湥ąĄą║. ąĢčüą╗ąĖ FIFO čĆą░ą▒ąŠčéą░ąĄčé ą▓ čĆąĄąČąĖą╝ąĄ 32 ą▒ąĖčéą░ (ą║ąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮąĮą░čÅ ą┤ą╗ąĖąĮą░ čüą╗ąŠą▓ą░ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé), č鹊 ą│ą╗čāą▒ąĖąĮą░ FIFO ą▒čāą┤ąĄčé 4 čÅč湥ą╣ą║ąĖ. FIFO čÅą▓ą╗čÅąĄčéčüčÅ ąŠą▒čēąĖą╝ ąĖ ą┤ą╗čÅ ą┐ąĄčĆą▓ąĖčćąĮčŗčģ, ąĖ ą┤ą╗čÅ ą▓č鹊čĆąĖčćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠčĆčÅą┤ąŠą║ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ FIFO ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 13-8.

| ąĀą░ąĘčĆąĄčłąĄąĮ č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ PRIMARY: |

ąĀą░ąĘčĆąĄčłąĄąĮčŗ ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░, PRIMARY ąĖ SECONDARY: |

|

|

| ąöą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮą░ 16 ą▒ąĖčé. ąÆ FIFO ąĮą░čģąŠą┤ąĖčéčüčÅ 8 čüą╗ąŠą▓ PRIMARY-ą┤ą░ąĮąĮčŗčģ |

ąöą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮą░ 16 ą▒ąĖčé. ąÆ FIFO ąĮą░čģąŠą┤ąĖčéčüčÅ 4 čüą╗ąŠą▓ą░ PRIMARY-ą┤ą░ąĮąĮčŗčģ ąĖ 4 čüą╗ąŠą▓ą░ SECONDARY-ą┤ą░ąĮąĮčŗčģ |

|

|

| ąĀą░ąĘčĆąĄčłąĄąĮ č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ PRIMARY. ąöą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé. ąÆ FIFO ąĮą░čģąŠą┤ąĖčéčüčÅ 4 čüą╗ąŠą▓ą░ PRIMARY-ą┤ą░ąĮąĮčŗčģ |

ąöą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé. ąÆ FIFO ąĮą░čģąŠą┤ąĖčéčüčÅ 2 čüą╗ąŠą▓ą░ PRIMARY-ą┤ą░ąĮąĮčŗčģ ąĖ 2 čüą╗ąŠą▓ą░ SECONDARY-ą┤ą░ąĮąĮčŗčģ |

ąĀąĖčü. 13-8. ą¤ąŠčĆčÅą┤ąŠą║ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ SPORT Transmit FIFO.

ąÆą░ąČąĮąŠ čüąŠčģčĆą░ąĮąĖčéčī č湥čĆąĄą┤ąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆą▓ąĖčćąĮčŗčģ ąĖ ą▓č鹊čĆąĖčćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą▓ FIFO čéą░ą║, ą║ą░ą║ čŹč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčüčāąĮą║ąĄ. ąŁč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĘą░ą┐ąĖčüąĖ PAB/DMA ą▓ FIFO ą┤ąŠą╗ąČąĮčŗ čüą╗ąĄą┤ąŠą▓ą░čéčī čéą░ą║ąŠą╝čā ą┐ąŠčĆčÅą┤ą║čā, čćč鹊 ą┐ąĄčĆą▓ąĖčćąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĖą┤čāčé ą┐ąĄčĆą▓čŗą╝ąĖ, ąĖ ąĘą░č鹥ą╝ ąĖą┤čāčé ą▓č鹊čĆąĖčćąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ąĄčüą╗ąĖ ą▓č鹊čĆąĖčćąĮčŗą╣ ą║ą░ąĮą░ą╗ ą┤ą░ąĮąĮčŗčģ čĆą░ąĘčĆąĄčłąĄąĮ. ąŚą░ą┐ąĖčüąĖ DAB/PAB ą┤ąŠą╗ąČąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą┐ąŠ čĆą░ąĘą╝ąĄčĆčā ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą┤ą╗ąĖąĮąĄ čüą╗ąŠą▓ą░. ąöą╗čÅ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓ą░ ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠą│ąŠ 16 ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 16-ą▒ąĖčéąĮčŗąĄ ąĘą░ą┐ąĖčüąĖ. ąöą╗čÅ čüą╗ąŠą▓ ą┤ą╗ąĖąĮąŠą╣ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 32-ą▒ąĖčéąĮčŗąĄ ąĘą░ą┐ąĖčüąĖ.

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ čĆą░ąĘčĆąĄčłąĄąĮą░, ą┤ą░ąĮąĮčŗąĄ ą┤ą╗čÅ FIFO čüąŠą▒ąĖčĆą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čģčĆą░ąĮąĄąĮąĖčÅ TX ąĮą░ ą▒ą░ąĘąĄ ą▓čŗą▒čĆą░ąĮąĮčŗčģ TXSE ąĖ SLEN, ąĖ ąĘą░č鹥ą╝ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ą▓ ą┐ąĄčĆą▓ąĖčćąĮčŗą╣ ąĖ ą▓č鹊čĆąĖčćąĮčŗą╣ čĆąĄą│ąĖčüčéčĆčŗ čüą┤ą▓ąĖą│ą░. ą×čéčüčÄą┤ą░ ą┤ą░ąĮąĮčŗąĄ ą▓čŗą┤ą▓ąĖą│ą░čÄčéčüčÅ ąĮą░čĆčāąČčā ą▒ąĖčé ąĘą░ ą▒ąĖč鹊ą╝ č湥čĆąĄąĘ ą▓čŗą▓ąŠą┤čŗ DTxPRI ąĖ DTxSEC (ą┐ąĄčĆą▓ąĖčćąĮčŗą╣ ąĖ ą▓č鹊čĆąĖčćąĮčŗą╣ ą▓čŗą▓ąŠą┤čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ). ąĪą╝. čĆąĖčü. 13-9.

ąĀąĖčü. 13-9. SPORTx Transmit Data Register.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPORT TX ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ TSPEN = 1 ąĖ ą▓ TX FIFO ąĖą╝ąĄąĄčéčüčÅ ą╝ąĄčüč鹊 ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗčģ čüą╗ąŠą▓. ąŁč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé, ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ DMA ą┤ą╗čÅ SPORT. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čĆą░ą▒ąŠčéčā DMA čüą╝. čüčéą░čéčīčÄ [4].

ąæąĖčé ąĘą░ą┐ą░ąĘą┤čŗą▓ą░ąĮąĖčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit underflow, TUVF) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ SPORT, ą║ąŠą│ą┤ą░ ą┐ąŠčÅą▓ąĖčéčüčÅ ąĖą╝ą┐čāą╗čīčü frame sync ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄ ą▒čŗą╗ąĖ ąĘą░ą│čĆčāąČąĄąĮčŗ ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąÆ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (multichannel mode, MCM), TUVF čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ ąĮąĄ ąĘą░ą│čĆčāąČąĄąĮ, ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ąĮą░čćą░ą╗ą░čüčī čü č鹥ą║čāčēąĄą│ąŠ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░. ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ TUVF čÅą▓ą╗čÅąĄčéčüčÅ sticky-ą▒ąĖč鹊ą╝ (čāą┤ąĄčƹȹĖą▓ą░čÄčēąĖą╝ čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ), čĆą░ą▒ąŠčéą░čÄčēąĖą╝ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā write-1-to-clear (W1C, ąĘą░ą┐ąĖčüą░čéčī 1 ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ), ąĖ ą║ąŠč鹊čĆčŗą╣ čéą░ą║ąČąĄ ąŠčćąĖčēą░ąĄčéčüčÅ ą┐čĆąĖ ąĘą░ą┐čĆąĄč鹥 SPORT ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (ąĘą░ą┐ąĖčüčīčÄ TSPEN = 0).

ąĢčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą┐čŗčéą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüą░čéčī ą▓ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮčŗą╣ TX FIFO č湥čĆąĄąĘ ąĘą░ą┐ąĖčüčī SPORTx_TX, č鹊 ąĮąŠą▓čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▒čāą┤čāčé ą┐ąŠč鹥čĆčÅąĮčŗ, ąĖ ąĖą╝ąĄčÄčēąĖąĄčüčÅ ą┤ą░ąĮąĮčŗąĄ ą▓ FIFO ąĮąĄ ą▒čāą┤čāčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮčŗ. ąÆ čéą░ą║ąŠą╣ čüąĖčéčāą░čåąĖąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé čüčéą░čéčāčüą░ TOVF ąĖ ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ SPORT. ąæąĖčé TOVF čéą░ą║ąČąĄ čÅą▓ą╗čÅąĄčéčüčÅ sticky-ą▒ąĖč鹊ą╝, ą┐čĆąĖč湥ą╝ ąĄą│ąŠ ą╝ąŠąČąĮąŠ ąŠčćąĖčüčéąĖčéčī č鹊ą╗čīą║ąŠ ą┐čāč鹥ą╝ ąĘą░ą┐čĆąĄčéą░ SPORT TX. ą¦č鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą╝ąŠąČąĄčé ą╗ąĖ čÅą┤čĆąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆčā SPORTx_TX ą▒ąĄąĘ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ čéą░ą║ąŠą╣ ąŠčłąĖą▒ą║ąĖ, čüąĮą░čćą░ą╗ą░ ą┐čĆąŠčćąĖčéą░ą╣č鹥 čĆąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ (čüąŠčüč鹊čÅąĮąĖčÅ). ąæąĖčé TXF čĆąĄą│ąĖčüčéčĆą░ čüčéą░čéčāčüą░ SPORT ą▒čāą┤ąĄčé čĆą░ą▓ąĄąĮ 0, ąĄčüą╗ąĖ ą▓ FIFO ąĖą╝ąĄąĄčéčüčÅ ą╝ąĄčüč鹊 ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ąŠč湥čĆąĄą┤ąĮąŠą│ąŠ čüą╗ąŠą▓ą░.

ąæąĖčéčŗ čüčéą░čéčāčüą░ TXF ąĖ TOVF ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ SPORTx ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ ąĖąĘ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ SPORT ąĘą░ą┐čĆąĄčēąĄąĮ.

ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ąĮąĮčŗčģ SPORT:

SPORT0_TX ŌĆō 0xFFC0 0810 SPORT2_TX ŌĆō 0xFFC0 2510

SPORT1_TX ŌĆō 0xFFC0 0910 SPORT3_TX ŌĆō 0xFFC0 2610

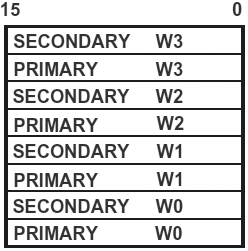

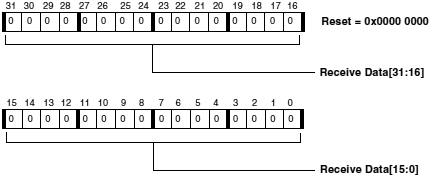

ąĀąĄą│ąĖčüčéčĆ ą┐čĆąĖąĄą╝ą░ ą┤ą░ąĮąĮčŗčģ SPORTx (SPORTx_RX) čĆą░ą▒ąŠčéą░ąĄčé č鹊ą╗čīą║ąŠ ąĮą░ čćč鹥ąĮąĖąĄ, čüą╝. čĆąĖčü. 13-10. ąŚą░ą┐ąĖčüčī ą▓ ąĮąĄą│ąŠ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčłąĖą▒ą║ąĄ PAB. ąŻ čĆąĄą│ąĖčüčéčĆą░ ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ ą╝ąĄčüč鹊 ą┐ąŠą╗ąŠąČąĄąĮąĖčÅ ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą║ą░ą║ ą┤ą╗čÅ ą┐ąĄčĆą▓ąĖčćąĮčŗčģ, čéą░ą║ ąĖ ą┤ą╗čÅ ą▓č鹊čĆąĖčćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ą¦č鹥ąĮąĖąĄ ąĖąĘ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ ą┐ąŠą╗čāč湥ąĮąĖčÄ ąĖąĘ FIFO ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ. ąŻ FIFO ą┐čĆąĖąĄą╝ą░ čéą░ą║ą░čÅ ąČąĄ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖčÅ, ą║ą░ą║ ąĖ čā FIFO ą┐ąĄčĆąĄą┤ą░čćąĖ, čé. ąĄ. ą▓ 16-ą▒ąĖčéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (ą║ąŠą│ą┤ą░ ą┤ą╗ąĖąĮą░ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░ ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮą░ 16 ą▒ąĖčé) FIFO ą▒čāą┤ąĄčé 8 čÅč湥ąĄą║ ą│ą╗čāą▒ąĖąĮąŠą╣, ąĖ ą▓ 32-ą▒ąĖčéąĮąŠą╝ čĆąĄąČąĖą╝ąĄ (ą║ąŠą│ą┤ą░ ą┤ą╗ąĖąĮą░ čüą╗ąŠą▓ą░ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé) ą│ą╗čāą▒ąĖąĮą░ FIFO ą▒čāą┤ąĄčé 4 čÅč湥ą╣ą║ąĖ. FIFO čÅą▓ą╗čÅąĄčéčüčÅ ąŠą▒čēąĖą╝ ą┤ą╗čÅ ą┐ąĄčĆą▓ąĖčćąĮčŗčģ ąĖ ą▓č鹊čĆąĖčćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░. ą¤ąŠčĆčÅą┤ąŠą║ čćč鹥ąĮąĖčÅ ą┤ą╗čÅ čćč鹥ąĮąĖą╣ PAB/DMA ą▓ą░ąČąĄąĮ, ą┐ąŠčüą║ąŠą╗čīą║čā ą┤ą░ąĮąĮčŗąĄ ą▓ FIFO čüąŠčģčĆą░ąĮčÅčÄčéčüčÅ ą┐ąŠ-čĆą░ąĘąĮąŠą╝čā ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čāčüčéą░ąĮąŠą▓ąŠą║ ą▒ąĖčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SLEN ąĖ RXSE.

ąĀąĖčü. 13-10. SPORTx Receive Data Register.

ąÜąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé čćč鹥ąĮąĖąĄ FIFO ą┤ą╗čÅ ą┐ąŠą╗čāč湥ąĮąĖčÅ ą║ą░ą║ ą┐ąĄčĆą▓ąĖčćąĮčŗčģ, čéą░ą║ ąĖ ą▓č鹊čĆąĖčćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ, čüąĮą░čćą░ą╗ą░ ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ ą┐ąĄčĆą▓ąĖčćąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ąĘą░ ą║ąŠč鹊čĆčŗą╝ąĖ ą▒čāą┤čāčé ąĖą┤čéąĖ ą▓č鹊čĆąĖčćąĮčŗąĄ. ą¦č鹥ąĮąĖčÅ DAB/PAB ą┤ąŠą╗ąČąĮčŗ čüąŠąŠčéą▓ąĄčéčüčéą▓ąŠą▓ą░čéčī ą┐ąŠ čüą▓ąŠąĄą╝čā čĆą░ąĘą╝ąĄčĆčā ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą╣ ą┤ą╗ąĖąĮąĄ čüą╗ąŠą▓ ą┤ą░ąĮąĮčŗčģ. ąöą╗čÅ čüą╗ąŠą▓ ą┤ą╗ąĖąĮąŠą╣ ą┤ąŠ 16 ą▒ąĖčé ą▓ą║ą╗čÄčćąĖč鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 16-ą▒ąĖčéąĮąŠąĄ čćč鹥ąĮąĖąĄ. ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 32-ą▒ąĖčéąĮąŠąĄ čćč鹥ąĮąĖąĄ ą┤ą╗čÅ čüą╗ąŠą▓ ą┤ą╗ąĖąĮąŠą╣ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé.

ąÜąŠą│ą┤ą░ ą┐čĆąĖąĄą╝ čĆą░ąĘčĆąĄčłąĄąĮ, ą┤ą░ąĮąĮčŗąĄ čü ą▓čŗą▓ąŠą┤ą░ DRxPRI ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ ą┐ąĄčĆą▓ąĖčćąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ RX, č鹊ą│ą┤ą░ ą║ą░ą║ ą┤ą░ąĮąĮčŗąĄ čü ą▓čŗą▓ąŠą┤ą░ DRxSEC ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ąŠ ą▓č鹊čĆąĖčćąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ RX. ą¤čĆąĖ ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆčŗ čģčĆą░ąĮąĄąĮąĖčÅ RX ą┤ą╗čÅ ą┐ąĄčĆą▓ąĖčćąĮčŗčģ ąĖ ą┤ą╗čÅ ą▓č鹊čĆąĖčćąĮčŗčģ ą┤ą░ąĮąĮčŗčģ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąŚą░č鹥ą╝ ą┤ą░ąĮąĮčŗąĄ ąĖąĘ čĆąĄą│ąĖčüčéčĆąŠą▓ čģčĆą░ąĮąĄąĮąĖčÅ ą┐ąĄčĆąĄą╝ąĄčēą░čÄčéčüčÅ ą▓ FIFO, ąŠčüąĮąŠą▓čŗą▓ą░čÅčüčī ąĮą░ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆą░čģ RXSE ąĖ SLEN.

ąōąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPORT RX, ą║ąŠą│ą┤ą░ RSPEN = 1 ąĖ ą▓ RX FIFO ąĖą╝ąĄčÄčéčüčÅ ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąÜąŠą│ą┤ą░ čÅą┤čĆąŠ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą┐čĆąŠčćąĖčéą░ą╗ąŠ ą▓čüąĄ čüą╗ąŠą▓ą░ ą▓ FIFO, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ RX ąŠčćąĖčēą░ąĄčéčüčÅ. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPORT RX čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ąĘą░ą┐čĆąĄčēąĄąĮąŠ SPORT RX DMA; ąĖąĮą░č湥 FIFO ą▒čāą┤ąĄčé ą▓čŗčćąĖčéčŗą▓ą░čéčīčüčÅ čćč鹥ąĮąĖčÅą╝ąĖ DMA.

ąĢčüą╗ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░ ą┐ąŠą┐čŗčéą░ąĄčéčüčÅ ą┐čĆąŠčćąĖčéą░čéčī ą┐čāčüč鹊ą╣ RX FIFO, ą▒čāą┤čāčé ą┐čĆąŠčćąĖčéą░ąĮčŗ čüčéą░čĆčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ąĖ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ SPORTx_STAT čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čäą╗ą░ą│ RUVF, ąĖ ą▒čāą┤ąĄčé ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ SPORT. ąæąĖčé RUVF čÅą▓ą╗čÅąĄčéčüčÅ sticky-ą▒ąĖč鹊ą╝, ąĖ ąŠąĮ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ č鹊ą╗čīą║ąŠ ą║ąŠą│ą┤ą░ SPORT ą▒čāą┤ąĄčé ąĘą░ą┐čĆąĄčēąĄąĮ. ą¦č鹊ą▒čŗ ąŠą┐čĆąĄą┤ąĄą╗ąĖčéčī, ą╝ąŠąČąĄčé ą╗ąĖ čÅą┤čĆąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čĆąĄą│ąĖčüčéčĆą░ą╝ RX ą▒ąĄąĘ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ čéą░ą║ąŠą╣ ąŠčłąĖą▒ą║ąĖ, čüąĮą░čćą░ą╗ą░ ą┐čĆąŠčćąĖčéą░ą╣č鹥 čüąŠčüč鹊čÅąĮąĖąĄ RX FIFO (RXNE ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ SPORT). ąæąĖčé RUVF ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ SPORT ąĘą░ą┐čĆąĄčēąĄąĮ.

ąæąĖčé čüčéą░čéčāčüą░ ROVF ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPORTx_STAT čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ąĮąŠą▓ąŠąĄ čüą╗ąŠą▓ąŠ čüąŠą▒čĆą░ąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüą┤ą▓ąĖą│ą░ RX, ąĖ čĆąĄą│ąĖčüčéčĆ čģčĆą░ąĮąĄąĮąĖčÅ RX ąĮąĄ ą┐ąĄčĆąĄą╝ąĄčüčéąĖą╗ ą┤ą░ąĮąĮčŗąĄ ą▓ FIFO. ąĪą╗ąŠą▓ąŠ, ą║ąŠč鹊čĆąŠąĄ ą▒čŗą╗ąŠ čĆą░ąĮąĄąĄ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆ čģčĆą░ąĮąĄąĮąĖčÅ, ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮąŠ (čé. ąĄ. ą┐ąŠč鹥čĆčÅąĮąŠ). ąæąĖčé ROVF čÅą▓ą╗čÅąĄčéčüčÅ sticky-ą▒ąĖč鹊ą╝; ąŠąĮ ąŠčćąĖčēą░ąĄčéčüčÅ č鹊ą╗čīą║ąŠ ąĘą░ą┐čĆąĄč鹊ą╝ ą┐čĆąĖąĄą╝ąĮąĖą║ą░ SPORT.

ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą░ąĮąĮčŗčģ ą┐čĆąĖąĄą╝ą░ SPORT:

SPORT0_RX ŌĆō 0xFFC0 0818

SPORT1_RX ŌĆō 0xFFC0 0918

SPORT2_RX ŌĆō 0xFFC0 2518

SPORT3_RX ŌĆō 0xFFC0 2618

ąźčĆą░ąĮąĖą╗ąĖčēąĄ ą┤ą░ąĮąĮčŗčģ ąĖ ą┐ąŠčĆčÅą┤ąŠą║ čģčĆą░ąĮąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ FIFO ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčü. 13-11.

| ąĀą░ąĘčĆąĄčłąĄąĮ č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ PRIMARY: |

ąĀą░ąĘčĆąĄčłąĄąĮčŗ ąŠą▒ą░ ą║ą░ąĮą░ą╗ą░, PRIMARY ąĖ SECONDARY: |

|

|

| ąöą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮą░ 16 ą▒ąĖčé. ąÆ FIFO ąĮą░čģąŠą┤ąĖčéčüčÅ 8 čüą╗ąŠą▓ PRIMARY-ą┤ą░ąĮąĮčŗčģ |

ąöą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąĮčīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮą░ 16 ą▒ąĖčé. ąÆ FIFO ąĮą░čģąŠą┤ąĖčéčüčÅ 4 čüą╗ąŠą▓ą░ PRIMARY-ą┤ą░ąĮąĮčŗčģ ąĖ 4 čüą╗ąŠą▓ą░ SECONDARY-ą┤ą░ąĮąĮčŗčģ |

|

|

| ąĀą░ąĘčĆąĄčłąĄąĮ č鹊ą╗čīą║ąŠ ą║ą░ąĮą░ą╗ PRIMARY. ąöą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé. ąÆ FIFO ąĮą░čģąŠą┤ąĖčéčüčÅ 4 čüą╗ąŠą▓ą░ PRIMARY-ą┤ą░ąĮąĮčŗčģ |

ąöą╗ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé. ąÆ FIFO ąĮą░čģąŠą┤ąĖčéčüčÅ 2 čüą╗ąŠą▓ą░ PRIMARY-ą┤ą░ąĮąĮčŗčģ ąĖ 2 čüą╗ąŠą▓ą░ SECONDARY-ą┤ą░ąĮąĮčŗčģ |

ąĀąĖčü. 13-11. ąÜą░ą║ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮčŗ ą┤ą░ąĮąĮčŗąĄ ą▓ SPORT Receive FIFO.

ąĀąĄą│ąĖčüčéčĆ čüčéą░čéčāčüą░ (čüąŠčüč鹊čÅąĮąĖčÅ) SPORT (SPORTx_STAT) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ, ą╝ąŠąČąĮąŠ ą╗ąĖ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ RX FIFO ąĖą╗ąĖ TX FIFO ą┐čāč鹥ą╝ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĖčģ čüąŠčüč鹊čÅąĮąĖčÅ ąĘą░ą┐ąŠą╗ąĮąĄąĮąĮąŠčüčéąĖ ąĖą╗ąĖ ąŠą┐čāčüč鹊賹ĄąĮąĖčÅ. ąĪą╝. čĆąĖčü. 13-12.

ąæąĖčé TXF ą▓ čĆąĄą│ąĖčüčéčĆąĄ čüąŠčüč鹊čÅąĮąĖčÅ SPORT ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ąĄčüčéčī ąĖą╗ąĖ ąĮąĄčé ą╝ąĄčüč鹊 ą▓ TX FIFO. ąæąĖčé RXNE ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, ąĄčüčéčī ąĖą╗ąĖ ąĮąĄčé ą┐čĆąĖąĮčÅčéčŗąĄ čüą╗ąŠą▓ą░ ą▓ RX FIFO. ąæąĖčé TXHRE ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 čĆąĄą│ąĖčüčéčĆ čģčĆą░ąĮąĄąĮąĖčÅ TX ą┐čāčüčé.

ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ ąĮąĄą┤ąŠą│čĆčāąĘą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit underflow, TUVF) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓čüčÅą║ąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐ąŠčÅą▓ąĖą╗čüčÅ ą░ą║čéąĖą▓ąĮčŗą╣ ąĖą╝ą┐čāą╗čīčü TFS (čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą▓ąĮčāčéčĆąĖ ąĖą╗ąĖ ą┐ąŠą╗čāč湥ąĮąĮčŗą╣ čüąĮą░čĆčāąČąĖ), ąĖ ą┐čĆąĖ čŹč鹊ą╝ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░ TX ą▒čŗą╗ ą┐čāčüčé. ąōąĄąĮąĄčĆą░čåąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖą╝ą┐čāą╗čīčüą░ TFS ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą┤ą░ą▓ą╗ąĄąĮą░ ą┐čĆąĖ ąŠą┐čāčüč鹊賹ĄąĮąĖąĖ SPORTx_TX ą┐čāč鹥ą╝ ąŠčćąĖčüčéą║ąĖ ą▒ąĖčéą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ DITFS ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ SPORT. ąæąĖčé čüąŠčüč鹊čÅąĮąĖčÅ TUVF čÅą▓ą╗čÅąĄčéčüčÅ sticky-ą▒ąĖč鹊ą╝, čĆą░ą▒ąŠčéą░čÄčēąĖą╝ ą┐ąŠ ą░ą╗ą│ąŠčĆąĖčéą╝čā write-1-to-clear (W1C, ąĘą░ą┐ąĖčłąĖč鹥 1 ą┤ą╗čÅ ąŠčćąĖčüčéą║ąĖ), ąĖ ąĄą│ąŠ ą╝ąŠąČąĮąŠ čéą░ą║ąČąĄ ąŠčćąĖčüčéąĖčéčī ą┐čāč鹥ą╝ ąĘą░ą┐čĆąĄčéą░ SPORT (ąĘą░ą┐ąĖčüčīčÄ TSPEN = 0).

ąĀąĖčü. 13-12. SPORTx Status Register.

ąöą╗čÅ ą┐čĆąŠą┤ąŠą╗ąČą░čÄčēąĄą╣čüčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (TFSR = 0) ą▒ąĖčé TUVF čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠ ąŠą║ąŠąĮčćą░ąĮąĖąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░, ąĄčüą╗ąĖ ąĮąĄčé ąĮąŠą▓ąŠą│ąŠ, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čüą╗ąŠą▓ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ čģčĆą░ąĮąĄąĮąĖčÅ TX.

ąæąĖčé TOVF čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ čüą╗ąŠą▓ąŠ ą▓ TX FIFO, ąĖ ąŠąĮ čāąČąĄ ą▒čŗą╗ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮ. ąŁč鹊 čéą░ą║ąČąĄ sticky W1C ą▒ąĖčé, ąĖ ąĄą│ąŠ čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąŠčćąĖčüčéąĖčéčī ąĘą░ą┐ąĖčüčīčÄ TSPEN = 0. ą×ą▒ą░ ą▒ąĖčéą░ TXF ąĖ TOVF ąŠą▒ąĮąŠą▓ą╗čÅčÄčéčüčÅ ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ SPORT ąĘą░ą┐čĆąĄčēąĄąĮ.

ąÜąŠą│ą┤ą░ čĆąĄą│ąĖčüčéčĆ čģčĆą░ąĮąĄąĮąĖčÅ RX ąĘą░ą┐ąŠą╗ąĮąĄąĮ, ąĖ ąĮąŠą▓ąŠąĄ ą┐čĆąĖąĮčÅč鹊ąĄ čüą╗ąŠą▓ą░ ą┐ąŠčüčéčāą┐ąĖą╗ąŠ ą▓ čĆąĄą│ąĖčüčéčĆ čüą┤ą▓ąĖą│ą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé čüąŠčüč鹊čÅąĮąĖčÅ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (receive overflow, ROVF). ą×čé čéą░ą║ąČąĄ čÅą▓ą╗čÅąĄčéčüčÅ sticky W1C ą▒ąĖč鹊ą╝, ąĖ čéą░ą║ąČąĄ ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐čĆąĄč鹊ą╝ SPORT (ąĘą░ą┐ąĖčüčīčÄ RSPEN = 0).

ąæąĖčé RUVF čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ čüą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ čćč鹥ąĮąĖčÅ ąĖąĘ RX FIFO, ą║ąŠą│ą┤ą░ ąŠąĮ čāąČąĄ ą▒čŗą╗ ą┐čāčüčé. ąŁč鹊 čéą░ą║ąČąĄ sticky W1C ą▒ąĖčé, ąĖ ąŠąĮ čéą░ą║ąČąĄ ąŠčćąĖčēą░ąĄčéčüčÅ ąĘą░ą┐ąĖčüčīčÄ RSPEN = 0. ąæąĖčé RUVF ąŠą▒ąĮąŠą▓ą╗čÅąĄčéčüčÅ ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ SPORT ąĘą░ą┐čĆąĄčēąĄąĮ.

ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ čüąŠčüč鹊čÅąĮąĖčÅ SPORT:

SPORT0_STAT ŌĆō 0xFFC0 0830

SPORT1_STAT ŌĆō 0xFFC0 0930

SPORT2_STAT ŌĆō 0xFFC0 2530

SPORT3_STAT ŌĆō 0xFFC0 2630

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ RX, TX ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ. ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPORT RX ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ RSPEN čĆą░ąĘčĆąĄčłąĄąĮ, ąĖ ąĖą╝ąĄąĄčéčüčÅ ą╗čÄą▒ąŠąĄ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮąŠąĄ čüą╗ąŠą▓ąŠ ą▓ RX FIFO. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ RX DMA, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPORT RX ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ, ąĖ č鹊ą│ą┤ą░ DMA ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ą┤ą░ąĮąĮčŗčģ ąĖąĘ RX FIFO.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPORT TX ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ TSPEN čĆą░ąĘčĆąĄčłąĄąĮ, ąĖ ą║ąŠą│ą┤ą░ ą▓ TX FIFO ąĄčüčéčī ą╝ąĄčüč鹊 ą┤ą╗čÅ ąĮąŠą▓čŗčģ čüą╗ąŠą▓. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮąŠ TX DMA, č鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ SPORT TX ą▓čŗą║ą╗čÄčćą░ąĄčéčüčÅ, ąĖ č鹊ą│ą┤ą░ DMA ąŠą▒čüą╗čāąČąĖą▓ą░ąĄčé ąĘą░ą┐ąŠą╗ąĮąĄąĮąĖąĄ TX FIFO.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąŠčłąĖą▒ą║ąĖ SPORT ą▓čŗčüčéą░ą▓ą╗čÅąĄčéčüčÅ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗čÄą▒ąŠą╣ ąĖąĘ sticky-ą▒ąĖč鹊ą▓ čüčéą░čéčāčüą░ (ROVF, RUVF, TOVF, TUVF). ąæąĖčéčŗ ROVF ąĖ RUVF ąŠčćąĖčēą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčīčÄ 0 ą▓ RSPEN (ąĘą░ą┐čĆąĄč鹊ą╝ SPORT ąĮą░ ą┐čĆąĖąĄą╝). ąæąĖčéčŗ TOVF ąĖ TUVF ąŠčćąĖčēą░čÄčéčüčÅ č鹊ą╗čīą║ąŠ ąĘą░ą┐ąĖčüčīčÄ 0 ą▓ TSPEN (ąĘą░ą┐čĆąĄč鹊ą╝ SPORT ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā).

ą×čłąĖą▒ą║ąĖ PAB. SPORT ą│ąĄąĮąĄčĆąĖčĆčāąĄčé ąŠčłąĖą▒ą║čā PAB ą┤ą╗čÅ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗčģ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ ąĖą╗ąĖ ąĘą░ą┐ąĖčüąĖ čĆąĄą│ąĖčüčéčĆąŠą▓. ąóą░ą║ąŠąĄ ą╝ąŠąČąĄčé ą┐čĆąŠąĖąĘąŠą╣čéąĖ, ąĄčüą╗ąĖ:

ŌĆó ą¤čĆąŠąĖąĘąŠčłą╗ąŠ čćč鹥ąĮąĖąĄ čĆąĄą│ąĖčüčéčĆą░, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮąŠą│ąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, SPORTx_TX).

ŌĆó ąæčŗą╗ą░ ąĘą░ą┐ąĖčüčī ą▓ čĆąĄą│ąĖčüčéčĆ, ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąĮčŗą╣ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, SPORTx_RX).

ŌĆó ą¤čĆąĖą╝ąĄąĮąĄąĮčŗ ąĘą░ą┐ąĖčüčī ąĖą╗ąĖ čćč鹥ąĮąĖąĄ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ čĆą░ąĘą╝ąĄčĆą░ (ąĮą░ą┐čĆąĖą╝ąĄčĆ, 32-ą▒ąĖčéąĮąŠąĄ čćč鹥ąĮąĖąĄ 16-ą▒ąĖčéąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░).

ŌĆó ąĪą┤ąĄą╗ą░ąĮą░ ą┐ąŠą┐čŗčéą║ą░ ą┤ąŠčüčéčāą┐ą░ ą║ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą░ą┤čĆąĄčüą░ą╝ čĆąĄą│ąĖčüčéčĆąŠą▓.

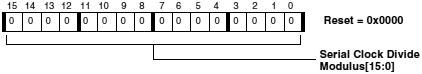

ą¦ą░čüč鹊čéčŗ ą▓čüąĄčģ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ą▓ąĮčāčéčĆąĖ čéą░ą║č鹊ą▓ čÅą▓ą╗čÅčÄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (ą║ąŠč鹊čĆą░čÅ ą┐čĆąĖčüčāčéčüčéą▓čāąĄčé ąĮą░ ą▓čŗą▓ąŠą┤ąĄ SCLK) ąĖ ąĘąĮą░č湥ąĮąĖčÅ 16-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ąŠą┤čāą╗čÅ ą┤ąĄą╗ąĖč鹥ą╗čÅ čéą░ą║č鹊ą▓ (čĆąĄą│ąĖčüčéčĆ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ SPORTx_TCLKDIV ąĖ čĆąĄą│ąĖčüčéčĆ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓ ą┐čĆąĖąĄą╝ą░ SPORTx_RCLKDIV).

ąĀąĖčü. 13-13. SPORTx Transmit Serial Clock Divider Register.

ąĀąĖčü. 13-14. SPORTx Receive Serial Clock Divider Register.

ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ ą┤ą╗čÅ čéą░ą║č鹊ą▓čŗčģ čćą░čüč鹊čé ą▒ąĖčé SPORT:

SPORT0_TCLKDIV ŌĆō 0xFFC0 0808 SPORT0_RCLKDIV ŌĆō 0xFFC0 0828

SPORT1_TCLKDIV ŌĆō 0xFFC0 0908 SPORT1_RCLKDIV ŌĆō 0xFFC0 0928

SPORT2_TCLKDIV ŌĆō 0xFFC0 2508 SPORT2_RCLKDIV ŌĆō 0xFFC0 2528

SPORT3_TCLKDIV ŌĆō 0xFFC0 2608 SPORT3_RCLKDIV ŌĆō 0xFFC0 2628

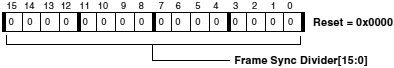

16-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ ą┤ąĄą╗ąĖč鹥ą╗čÅ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąĖą│ąĮą░ą╗ą░ čäčĆąĄą╣ą╝ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░ (SPORTx_TFSDIV ąĖ SPORTx_RFSDIV čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ) ąĘą░ą┤ą░čÄčé, čüą║ąŠą╗čīą║ąŠ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąŠą╣čéąĖ, ą┐ąĄčĆąĄą┤ ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ ąĖą╝ą┐čāą╗čīčüą░ TFSx ąĖ RFSx ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░ frame sync (ą║ąŠą│ą┤ą░ čŹčéąĖ ąĖą╝ą┐čāą╗čīčüčŗ ą│ąĄąĮąĄčĆąĖčĆčāčÄčéčüčÅ ą▓ąĮčāčéčĆąĖ SPORT). ąóą░ą║ąĖą╝ ą╝ąĄč鹊ą┤ąŠą╝ frame sync ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą┤ą╗čÅ ąĖąĮąĖčåąĖąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖčģ ą┐ąĄčĆąĄą┤ą░čć. ą¤ąŠą┤čüč湥čé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓ ą▒ąĖčé ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░ąĄčéčüčÅ ą╗ąĖą▒ąŠ ą║ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĄ, ą╗ąĖą▒ąŠ ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╝ čüąĮą░čĆčāąČąĖ čéą░ą║č鹊ą▓čŗą╝ čüąĖą│ąĮą░ą╗ą░ą╝.

ąÉą┤čĆąĄčüą░ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ąĄą╗ąĖč鹥ą╗ąĄą╣ SPORT:

SPORT0_TFSDIV ŌĆō 0xFFC0 080C SPORT0_RFSDIV ŌĆō 0xFFC0 082C

SPORT1_TFSDIV ŌĆō 0xFFC0 090C SPORT1_RFSDIV ŌĆō 0xFFC0 092C

SPORT2_TFSDIV ŌĆō 0xFFC0 250C SPORT2_RFSDIV ŌĆō 0xFFC0 252C

SPORT3_TFSDIV ŌĆō 0xFFC0 260C SPORT3_RFSDIV ŌĆō 0xFFC0 262C

ąĀąĖčü. 13-15. SPORTx Transmit Frame Sync Divider Register.

ąĀąĖčü. 13-16. SPORTx Receive Frame Sync Divider Register.

[ą¦ą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ąĖ čćą░čüč鹊čéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čäčĆąĄą╣ą╝ą░]

ą£ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ą░čÅ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ ą▒ąĖčé (ą╗ąĖą▒ąŠ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝ą░čÅ ą▓ąĮčāčéčĆąĖ, ą╗ąĖą▒ąŠ ą┐ąŠčüčéčāą┐ą░čÄčēą░čÅ čüąĮą░čĆčāąČąĖ) čĆą░ą▓ąĮą░ SCLK/2. ą¦ą░čüč鹊čéą░ ą┤ą╗čÅ čéą░ą║č鹊ą▓, ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗčģ ą▓ąĮčāčéčĆąĖ, čÅą▓ą╗čÅąĄčéčüčÅ čäčāąĮą║čåąĖąĄą╣ ąŠčé čüąĖčüč鹥ą╝ąĮąŠą╣ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ (system clock frequency, SCLK) ąĖ ąĘąĮą░č湥ąĮąĖčÅ, ąĘą░ą┐ąĖčüą░ąĮąĮčŗąĄ ą▓ 16-ą▒ąĖčéąĮčŗąĄ čĆąĄą│ąĖčüčéčĆčŗ SPORTx_TCLKDIV ąĖ SPORTx_RCLKDIV.

ą¦ą░čüč鹊čéą░ SPORTx_TCLK = (čćą░čüč鹊čéą░ SCLK)/(2 x (SPORTx_TCLKDIV + 1))

ą¦ą░čüč鹊čéą░ SPORTx_RCLK = (čćą░čüč鹊čéą░ SCLK)/(2 x (SPORTx_RCLKDIV + 1))

ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ SPORTx_TCLKDIV ąĖą╗ąĖ SPORTx_RCLKDIV ą▒čŗą╗ąŠ ąĖąĘą╝ąĄąĮąĄąĮąŠ ą┐čĆąĖ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓ ą▒ąĖčé, č鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čćą░čüč鹊čéčŗ TSCLK ąĖą╗ąĖ RSCLK ą▓čüčéčāą┐ąĖčé ą▓ čüąĖą╗čā ą▓ ąĮą░čćą░ą╗ąĄ ą░ą║čéąĖą▓ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┐ą░ą┤ą░ TSCLKx ąĖą╗ąĖ RSCLKx, ąĘą░ ą║ąŠč鹊čĆčŗą╝ čüą╗ąĄą┤čāąĄčé ą╗ąĖą┤ąĖčĆčāčÄčēąĖą╣ ą┐ąĄčĆąĄą┐ą░ą┤ TFSx ąĖą╗ąĖ RFSx.

ąÜąŠą│ą┤ą░ ą▓čŗą▒čĆą░ąĮą░ ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą│ąĄąĮąĄčĆą░čåąĖčÅ frame sync (ITFS = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPORTx_TCR1 ąĖą╗ąĖ IRFS = 1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPORTx_RCR1) ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ čäčĆąĄą╣ą╝ą░ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ, ą┐ąĄčĆą▓čŗą╣ frame sync ąĮąĄ ąŠą▒ąĮąŠą▓ąĖčé ą┤ąĄą╗ąĖč鹥ą╗čī čéą░ą║č鹊ą▓, ąĄčüą╗ąĖ ą▒čŗą╗ąŠ ąĖąĘą╝ąĄąĮąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ SPORTx_TCLKDIV ąĖą╗ąĖ SPORTx_RCLKDIV. ą×ą▒ąĮąŠą▓ą╗ąĄąĮąĖąĄ ą┐čĆąŠąĖąĘą▓ąĄą┤ąĄčé ą▓č鹊čĆąŠą╣ frame sync.

ąĀąĄą│ąĖčüčéčĆčŗ SPORTx_TFSDIV ąĖ SPORTx_RFSDIV ąĘą░ą┤ą░čÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ čéą░ą║č鹊ą▓čŗčģ čåąĖą║ą╗ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░, ą║ąŠč鹊čĆčŗąĄ ą▒čāą┤čāčé ą┐ąŠą┤čüčćąĖčéą░ąĮčŗ ą┐ąĄčĆąĄą┤ ą│ąĄąĮąĄčĆą░čåąĖąĄą╣ ąĖą╝ą┐čāą╗čīčüą░ TFSx ąĖą╗ąĖ RFSx (ą║ąŠą│ą┤ą░ frame sync ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą▓ąĮčāčéčĆąĖ). ąŁč鹊 čĆą░ąĘčĆąĄčłąĖčé frame sync ą┤ą╗čÅ ąĖąĮąĖčåąĖą░čåąĖąĖ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖčģ ą┐ąĄčĆąĄą┤ą░čć. ą¤ąŠą┤čüč湥čé ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą╗ąĖą▒ąŠ ą║ ą│ąĄąĮąĄčĆąĖčĆčāąĄą╝čŗą╝ ą▓ąĮčāčéčĆąĖ, ą╗ąĖą▒ąŠ ą┐ąŠčüčéčāą┐ą░čÄčēąĖą╝ čüąĮą░čĆčāąČąĖ čéą░ą║čéą░ą╝ ą▒ąĖčé.

ążąŠčĆą╝čāą╗ą░ ą┤ą╗čÅ ą║ąŠą╗ąĖč湥čüčéą▓ą░ čåąĖą║ą╗ąŠą▓ ą╝ąĄąČą┤čā ąĖą╝ą┐čāą╗čīčüą░ą╝ąĖ frame sync:

ą¦ąĖčüą╗ąŠ čéą░ą║č鹊ą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ ą╝ąĄąČą┤čā frame sync = TFSDIV + 1

ą¦ąĖčüą╗ąŠ čéą░ą║č鹊ą▓ ą┐čĆąĖąĄą╝ą░ ą╝ąĄąČą┤čā frame sync = RFSDIV + 1

ąśčüą┐ąŠą╗čīąĘčāą╣č鹥 čüą╗ąĄą┤čāčÄčēąĖąĄ ą▓čŗčĆą░ąČąĄąĮąĖčÅ ą┤ą╗čÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ą║ąŠčĆčĆąĄą║čéąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ TFSDIV ąĖą╗ąĖ RFSDIV ą┐ąŠ ąĖą╝ąĄčÄčēąĄą╣čüčÅ čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊č鹥 ąĖ ąČąĄą╗ą░ąĄą╝ąŠą╣ čćą░čüč鹊č鹥 frame sync:

ą¦ą░čüč鹊čéą░ SPORTxTFS = (čćą░čüč鹊čéą░ TSCLKx)/(SPORTx_TFSDIV + 1)

ą¦ą░čüč鹊čéą░ SPORTxRFS = (čćą░čüč鹊čéą░ RSCLKx)/(SPORTx_RFSDIV + 1)

ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąĖą╝ą┐čāą╗čīčüčŗ frame sync ą▒čŗą╗ąĖ ą▒čŗ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą░ą║čéąĖą▓ąĮčŗą╝ąĖ (ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĄčüą╗ąĖ TFSDIV = 0, ąĖą╗ąĖ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ ąĄčüą╗ąĖ RFSDIV = 0). ą×ą┤ąĮą░ą║ąŠ, ąĘąĮą░č湥ąĮąĖąĄ TFSDIV (ąĖą╗ąĖ RFSDIV) ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą╝ąĄąĮčīčłąĄ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓ą░ ą╝ąĖąĮčāčü 1 (ą╝ąĄąĮčīčłąĄ ąĘąĮą░č湥ąĮąĖčÅ ą┐ąŠą╗čÅ SLEN ą▓ SPORTx_TCR2 ąĖą╗ąĖ SPORTx_RCR2). ąĢčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé ą╝ąĄąĮčīčłąĄ, č鹊 čŹč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠą▒čĆčŗą▓čā č鹥ą║čāčēąĄą╣ ąŠą┐ąĄčĆą░čåąĖąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖą╗ąĖ ą┤čĆčāą│ąĖą╝ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝. ąĢčüą╗ąĖ SPORT ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, č鹊 ą┤ąĄą╗ąĖč鹥ą╗čī TFSDIV (ąĖą╗ąĖ RFSDIV) ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ čüč湥čéčćąĖą║ ą┤ą╗čÅ ą┤ąĄą╗ąĄąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą╣ čćą░čüč鹊čéčŗ ąĖą╗ąĖ ą┤ą╗čÅ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖčģ ąĖą╝ą┐čāą╗čīčüąŠą▓ ąĖą╗ąĖ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣. SPORT ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ą┤ą╗čÅ čŹč鹊ą│ąŠ čĆąĄąČąĖą╝ą░ čĆą░ą▒ąŠčéčŗ.

ą×ą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čćą░čüč鹊čéčā čéą░ą║č鹊ą▓. ąōąĄąĮąĄčĆąĖčĆčāąĄą╝čŗąĄ čüąĮą░čĆčāąČąĖ ąĘą░ą┤ąĄčƹȹ░ąĮąĮčŗąĄ čüąĖą│ąĮą░ą╗čŗ frame sync ą┐ąĄčĆąĄą┤ą░čćąĖ čéą░ą║ąČąĄ ą┐čĆąĖą▓ąĄą┤čāčé ą║ ąĘą░ą┤ąĄčƹȹ║ąĄ ą┤ąŠ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ąĮą░ ą▓čŗčģąŠą┤, ąĖ čŹč鹊 čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ąŠą│čĆą░ąĮąĖčćąĖčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčāčÄ čćą░čüč鹊čéčā ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ čéą░ą║č鹊ą▓. ąĪą╝. ą┤ą░čéą░čłąĖčé ąĮą░ ą┐čĆąŠčåąĄčüčüąŠčĆčŗ ADSP-BF538/ADSP-BF538F, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ąŠą│čĆą░ąĮąĖč湥ąĮąĖą╣ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ.

ąÆ čüą╗ąĄą┤čāčÄčēąĄą╝ ą║čāčüą║ąĄ ą║ąŠą┤ą░ ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą║čĆą░čéą║ąĖą╣ ą┐čĆąĖą╝ąĄčĆ ąĮą░čüčéčĆąŠą╣ą║ąĖ čćą░čüč鹊čéčŗ čéą░ą║č鹊ą▓ ą▒ąĖčé ąĖ čüąĖą│ąĮą░ą╗ą░ frame sync.

r0 = 0x00FF;

p0.l = SPORT0_RFSDIV & 0xFFFF;

p0.h = (SPORT0_RFSDIV >> 16) & 0xFFFF;

w[p0] = r0.l; ssync;

p0.l = SPORT0_TFSDIV & 0xFFFF;

w[p0] = r0.l; ssync;

ąöą╗ąĖąĮą░ čüą╗ąŠą▓ą░. ąÜą░ąČą┤čŗą╣ ą║ą░ąĮą░ą╗ SPORT (ą║ą░ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ąĖ ą║ą░ąĮą░ą╗ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ą┤čĆčāą│ ąŠčé ą┤čĆčāą│ą░ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓ą░ ąŠčé 3 ą┤ąŠ 32 ą▒ąĖčé. ąöą░ąĮąĮčŗąĄ ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ą▓ą┐čĆą░ą▓ąŠ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ą┤ą░ąĮąĮčŗčģ SPORT, ąĄčüą╗ąĖ ąŠąĮąĖ ą╝ąĄąĮčīčłąĄ č湥ą╝ 32 ą▒ąĖčéą░ ą┤ą╗ąĖąĮąŠą╣, čü ąŠčĆąĖąĄąĮčéą░čåąĖąĄą╣ ąĮą░ ąĮą░čģąŠąČą┤ąĄąĮąĖąĄ ą┐ąŠąĘąĖčåąĖą╣ LSB. ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠą╗čÅ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓ą░ (SLEN) ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPORTx_TCR2 ąĖ SPORTx_RCR2 ą║ą░ąČą┤ąŠą│ąŠ SPORT ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé ą┤ą╗ąĖąĮčā čüą╗ąŠą▓ą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü č乊čĆą╝čāą╗ąŠą╣:

ąöą╗ąĖąĮą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠą│ąŠ čüą╗ąŠą▓ą░ = SLEN + 1

ąŚąĮą░č湥ąĮąĖąĄ SLEN ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąŠ ą▓ 0 ąĖą╗ąĖ 1; ą┤ąŠą┐čāčüčéąĖą╝čŗ ąĘąĮą░č湥ąĮąĖčÅ 2 .. 31. ąØąĄą┐čĆąĄčĆčŗą▓ąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ (ąĘą░ ą║ąŠą│ą┤ą░ ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝ ą▒ąĖč鹊ą╝ č鹥ą║čāčēąĄą│ąŠ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░ čüčĆą░ąĘčā ą▒čāą┤ąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą┐ąĄčĆą▓čŗą╣ ą▒ąĖčé čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüą╗ąŠą▓ą░) ąŠą│čĆą░ąĮąĖč湥ąĮąŠ čĆą░ąĘą╝ąĄčĆą░ą╝ąĖ čüą╗ąŠą▓ ąĮąĄ ą╝ąĄąĮčīčłąĄ 4 (SLEN Ōēź 3).

ą¤ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé. ąśą╝ąĄąĄčéčüčÅ ą▓ ą▓ąĖą┤čā, ą║ą░ą║ąŠą╣ ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ąĖčé ą┐ąŠčÅą▓ąĖčéčüčÅ ą▓ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą╝ (ąĖą╗ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠą╝) čüą╗ąŠą▓ąĄ ą┐ąĄčĆą▓čŗą╝ - MSB ąĖą╗ąĖ LSB. ą¤ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé ą▓čŗą▒ąĖčĆą░ąĄčéčüčÅ ą▒ąĖčéą░ą╝ąĖ RLSBIT ąĖ TLSBIT ą▓ čĆąĄą│ąĖčüčéčĆą░čģ SPORTx_RCR1 ąĖ SPORTx_TCR1. ąÜąŠą│ą┤ą░ RLSBIT ąĖą╗ąĖ TLSBIT = 0, č鹊 čüą╗ąŠą▓ą░ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ čüčéą░čĆčłąĖą╝ ą▒ąĖč鹊ą╝ (MSB) ą▓ą┐ąĄčĆąĄą┤. ąś ąĮą░ąŠą▒ąŠčĆąŠčé, ą║ąŠą│ą┤ą░ When RLSBIT (ąĖą╗ąĖ TLSBIT) = 1, ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ čüą╗ąŠą▓ą░ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ (ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ) čéą░ą║, čćč鹊 ą┐ąĄčĆą▓čŗą╝ ąĖą┤ąĄčé LSB.

ąóąĖą┐ ą┤ą░ąĮąĮčŗčģ. ą¤ąŠą╗ąĄ TDTYPE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPORTx_TCR1 ąĖ ą┐ąŠą╗ąĄ RDTYPE ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPORTx_RCR1 čāą║ą░ąĘčŗą▓ą░ąĄčé ąŠą┤ąĖąĮ ąĖąĘ 4 ą▓ąŠąĘą╝ąŠąČąĮčŗčģ č乊čĆą╝ą░č鹊ą▓ ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ ąŠą┤ąĮąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ ąĖą╗ąĖ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖčÅ, čüą╝. čéą░ą▒ą╗ąĖčåčā 13-2.

ąóą░ą▒ą╗ąĖčåą░ 13-2. TDTYPE, RDTYPE ąĖ č乊čĆą╝ą░čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ.

| TDTYPE ąĖą╗ąĖ RDTYPE |

ążąŠčĆą╝ą░čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ SPORTx_TCR1 |

ążąŠčĆą╝ą░čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ SPORTx_RCR1 |

| 00 |

ą×ą▒čŗčćąĮąŠąĄ čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ |

Zero-fill (ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĮčāą╗čÅą╝ąĖ) |

| 01 |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

Sign-extended (ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ąĘąĮą░ą║ąŠą╝) |

| 10 |

ąÜąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ╬╝-law |

ąÜąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ╬╝-law |

| 11 |

ąÜąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ A-law |

ąÜąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ A-law |

[ąÜąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ]

Companding (č鹥čĆą╝ąĖąĮ čüąŠčüčéą░ą▓ą╗ąĄąĮ ąŠčé čüą╗ąŠą▓ COMpressing ąĖ exPANDing, čé. ąĄ. čüąČą░čéąĖąĄ ąĖ čĆą░čüčłąĖčĆąĄąĮąĖąĄ) čŹč鹊 ą┐čĆąŠčåąĄčüčü ą╗ąŠą│ą░čĆąĖčäą╝ąĖč湥čüą║ąŠą│ąŠ ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čü čåąĄą╗čīčÄ ą╝ąĖąĮąĖą╝ąĖąĘą░čåąĖąĖ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ąĖčé, ą║ąŠč鹊čĆąŠąĄ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ. SPORT-čŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé 2 ąĮą░ąĖą▒ąŠą╗ąĄąĄ čłąĖčĆąŠą║ąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ, ╬╝-law ąĖ A-law. ą¤čĆąŠčåąĄčüčüąŠčĆ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆčāąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čüąŠ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĄą╣ CCITT G.711. ąóąĖą┐ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą▒čĆą░ąĮ ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ SPORTx.

ąÜąŠą│ą┤ą░ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ, ą┤ąŠą┐čāčüčéąĖą╝čŗąĄ ą┤ą░ąĮąĮčŗąĄ ą▓ čĆąĄą│ąĖčüčéčĆąĄ SPORTx_RX ą▓čŗčĆąŠą▓ąĮąĄąĮčŗ ą▓ą┐čĆą░ą▓ąŠ, čĆą░čüą┐ą░ą║ąŠą▓ą░ąĮąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ 8 ą┐čĆąĖąĮčÅčéčŗčģ LSB čĆą░čüą┐ą░ą║ąŠą▓čŗą▓ą░ąĄčéčüčÅ čüąŠ ąĘąĮą░ą║ąŠą╝ ą▓ 16 ą▒ąĖčé. ąŚą░ą┐ąĖčüčī ą▓ SPORTx_TX ą┐čĆąĖą▓ąŠą┤ąĖčé ą║ č鹊ą╝čā, čćč鹊 16-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▒čāą┤ąĄčé ą║ąŠą╝ą┐čĆąĄčüčüąĖčĆąŠą▓ą░ąĮąŠ ą▓ 8 LSB (čĆą░čüčłąĖčĆąĄąĮąĮąŠąĄ ąĘąĮą░ą║ąŠą╝ ą┤ąŠ čłąĖčĆąĖąĮčŗ ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝ąŠą│ąŠ čüą╗ąŠą▓ą░) ąĖ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ąŠ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│ąĖčüčéčĆ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąźąŠčéčÅ čüčéą░ąĮą┤ą░čĆčéčŗ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé č鹊ą╗čīą║ąŠ 13-ą▒ąĖčéąĮčŗąĄ (A-law) ąĖą╗ąĖ 14-ą▒ąĖčéąĮčŗąĄ (╬╝-law) ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗąĄ ą┤ą╗ąĖąĮčŗ čüą╗ąŠą▓, ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čüą╗ąŠą▓ą░ ą┤ąŠ 16 ą▒ąĖčé ą┤ą╗ąĖąĮąŠą╣. ąĢčüą╗ąĖ ą░ą▒čüąŠą╗čÄčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ (ą░ą╝ą┐ą╗ąĖčéčāą┤ą░) čüą╗ąŠą▓ą░ ą▒ąŠą╗čīčłąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠą╣, ąĘąĮą░č湥ąĮąĖąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čüąČąĖą╝ą░ąĄčéčüčÅ ą┤ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ ąĖą╗ąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ.

ąöą╗ąĖąĮčŗ ą▒ąŠą╗čīčłąĄ 16 ą▒ąĖčé ąĮąĄ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčéčüčÅ ąŠą┐ąĄčĆą░čåąĖąĄą╣ ą║ąŠą╝ą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ.

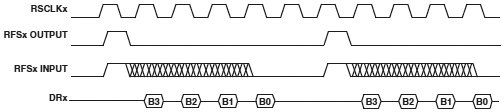

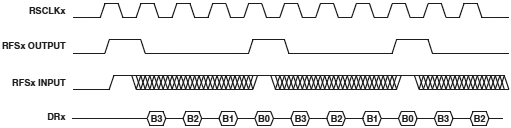

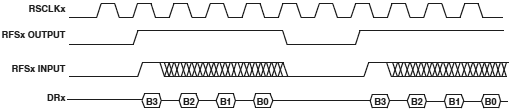

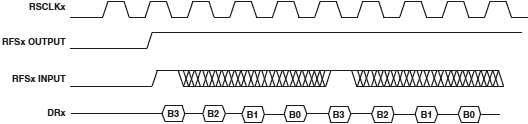

[ą×ą┐čåąĖąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé]