|

ą¤čĆąŠčåąĄčüčüąŠčĆčŗ ADSP-BF50x (ADSP-BF504, ADSP-BF504F, ADSP-BF506) ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN, ąŠą▒čüą╗čāąČąĖą▓ą░čÄčēąĖą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ ą┐ąŠ ą┐čĆąŠč鹊ą║ąŠą╗čā Controller Area Network (CAN) V2.0B. ąŁč鹊 ą░čüąĖąĮčģčĆąŠąĮąĮčŗą╣ ą┐čĆąŠč鹊ą║ąŠą╗ ą║ąŠą╝ą╝čāąĮąĖą║ą░čåąĖąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą▓ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ ąĖ ą░ą▓č鹊ą╝ąŠą▒ąĖą╗čīąĮčŗčģ čüąĖčüč鹥ą╝ą░čģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ. CAN čģąŠčĆąŠčłąŠ ą┐ąŠą┤čģąŠą┤ąĖčé ą┤ą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ą┐ąŠč鹊ą╝čā čćč鹊 ąŠąĮ čüą┐ąŠčüąŠą▒ąĄąĮ ąŠčüčāčēąĄčüčéą▓ąĖčéčī ąĮą░ą┤ąĄąČąĮčŗą╣ ąŠą▒ą╝ąĄąĮ ą┤ą░ąĮąĮčŗą╝ąĖ čüąŠ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐čĆąŠą▓ąĄčĆą║ąŠą╣ ąĖčģ čåąĄą╗ąŠčüčéąĮąŠčüčéąĖ ą║ąŠą┤ą░ą╝ąĖ CRC, čéčĆąĄą║ąĖąĮą│ąŠą╝ čüąŠąŠą▒čēąĄąĮąĖą╣ ąŠą▒ ąŠčłąĖą▒ą║ą░čģ ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄą╝ ąŠčéą║ą░ąĘą░ čāąĘą╗ą░ čüąĄčéąĖ.

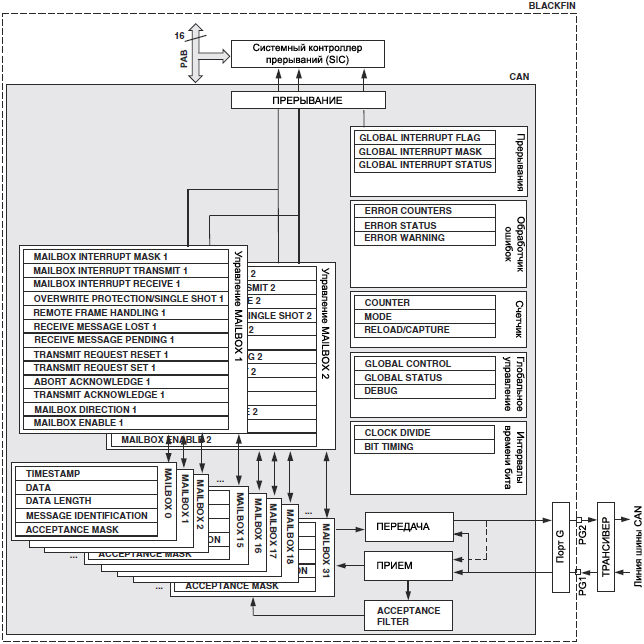

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ąŠčüąĮąŠą▓ą░ąĮ ąĮą░ ą×ąŚąŻ ą┐ąŠčćč鹊ą▓čŗčģ čÅčēąĖą║ąŠą▓ (mailbox RAM), čüąŠčüč鹊čÅčēąĄą╝ ąĖąĘ 32 čÅč湥ąĄą║ (8 čÅčēąĖą║ąŠą▓ č鹊ą╗čīą║ąŠ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā, 8 č鹊ą╗čīą║ąŠ ąĮą░ ą┐čĆąĖąĄą╝, ąĖ ąĄčēąĄ 16 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗčģ ą▓ ą╗čÄą▒ąŠą╝ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĖ), ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé č乊čĆą╝ą░čéčŗ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ (11 ą▒ąĖčé) ąĖ čĆą░čüčłąĖčĆąĄąĮąĮčŗčģ (29 ą▒ąĖčé) ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓ (ID) čüąŠąŠą▒čēąĄąĮąĖą╣, ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN revision 2.0 part B, ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čüą║ąŠčĆąŠčüčéąĖ ąŠą▒ą╝ąĄąĮą░ ą┤ą░ąĮąĮčŗčģ ą┤ąŠ 1 ą╝ąĄą│ą░ą▒ąĖčéą░/čüąĄą║. ąæą╗ą░ą│ąŠą┤ą░čĆčÅ čéą░ą║ąŠą╝čā ą▒ąŠą╗čīčłąŠą╝čā ą║ąŠą╗ąĖč湥čüčéą▓čā ą░ą┐ą┐ą░čĆą░čéąĮčŗčģ čÅčēąĖą║ąŠą▓ ąĖ ą▓čŗčüąŠą║ąŠą╣ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéąĖ Blackfin ą┐čĆą░ą║čéąĖč湥čüą║ąĖ ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąŠčéą┐ą░ą┤ą░ąĄčé ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ą▒čāč乥čĆąĖąĘą░čåąĖąĖ ą┐čĆąĖąĄą╝ą░ ąĖ/ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÜą░ąČą┤čŗą╣ mailbox čüąŠčüč鹊ąĖčé ąĖąĘ ą▓ąŠčüčīą╝ąĖ 16-ą▒ąĖčéąĮčŗčģ čüą╗ąŠą▓ą░ ą┤ą░ąĮąĮčŗčģ. ąöą░ąĮąĮčŗąĄ čĆą░ąĘą┤ąĄą╗ąĄąĮčŗ ąĮą░ ą┐ąŠą╗čÅ, ą║ąŠč鹊čĆčŗąĄ ą▓ą║ą╗čÄčćą░čÄčé ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čüąŠąŠą▒čēąĄąĮąĖčÅ (message identifier), ą╝ąĄčéą║čā ą▓čĆąĄą╝ąĄąĮąĖ (time stamp), čüč湥čéčćąĖą║ ą▒ą░ą╣čé (byte count), ą┤ąŠ 8 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą┐ąŠą╗ąĄąĘąĮąŠą╣ ąĮą░ą│čĆčāąĘą║ąĖ ąĖ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąÜą░ąČą┤čŗą╣ čāąĘąĄą╗ CAN ąŠčéčüą╗ąĄąČąĖą▓ą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖčÅ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗąĄ ą┐ąŠ čüąĄčéąĖ. ąÜą░ąČą┤čŗą╣ čÅčēąĖą║ ąĖą╝ąĄąĄčé ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮčāčÄ ą╝ą░čüą║čā ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ čüąŠąŠą▒čēąĄąĮąĖčÅ ą┐ąŠ ąĄą│ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā. ąĢčüą╗ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗą╣ ą▓ čüąŠąŠą▒čēąĄąĮąĖąĖ, čüąŠą▓ą┐ą░ą╗ čü ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą╝ ą▓ ąŠą┤ąĮąŠą╝ ąĖąĘ mailbox (ą┐ąŠą┐ą░ą╗ ą┐ąŠą┤ čāčüą╗ąŠą▓ąĖčÅ ą▓čŗą▒ąŠčĆą░, ąĘą░ą┤ą░ą▓ą░ąĄą╝ąŠąĄ ą╝ą░čüą║ąŠą╣), č鹊 ą╝ąŠą┤čāą╗čī ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, čćč鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąŠ ą┤ą╗čÅ ąĮąĄą│ąŠ, ą┐ąĄčĆąĄą┤ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ mailbox, ąĖ čü ą┐ąŠą╝ąŠčēčīčÄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ą░ąĄčé čüąĖą│ąĮą░ą╗ ą┐čĆąŠčåąĄčüčüąŠčĆčā ąŠ ą┐ąŠčüčéčāą┐ą╗ąĄąĮąĖąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ.

ąÆ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą▓čüčéčĆąŠąĄąĮą░ (ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą▓ą║ą╗čÄčćą░ąĄą╝ą░čÅ) čäąĖą╗čīčéčĆą░čåąĖčÅ čüąŠąŠą▒čēąĄąĮąĖą╣ ą┐ąŠ ą┐ąĄčĆą▓čŗą╝ 2 ą▒ą░ą╣čéą░ą╝ ą┤ą░ąĮąĮčŗčģ, čćč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąŠ ą┤ą╗čÅ čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐čĆąĖąĄą╝ą░ ą┐čĆąŠč鹊ą║ąŠą╗ą░ DeviceNetŌäó. ąĢčüčéčī čĆąĄą│ąĖčüčéčĆčŗ čüąŠčüč鹊čÅąĮąĖčÅ ąĖ čĆąĄą│ąĖčüčéčĆčŗ čüąŠąŠą▒čēąĄąĮąĖą╣ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ, čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮčŗą╣ ą╝ąŠą┤čāą╗čī čüč湥čéčćąĖą║ą░. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą╝ąŠąČąĄčé čüčćąĖčéčŗą▓ą░čéčī ą╗ąŠą│ąĖč湥čüą║ąĖąĄ čāčĆąŠą▓ąĮąĖ ąĮą░ ą▓čŗą▓ąŠą┤ą░čģ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ ą┐čĆąĖąĄą╝ą░.

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ą╝ąŠąČąĄčé čĆą░ąĘą▒čāą┤ąĖčéčī ą┐čĆąŠčåąĄčüčüąŠčĆ ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░ (sleep mode) ą┐čāč鹥ą╝ ą│ąĄąĮąĄčĆą░čåąĖąĖ čüąŠą▒čŗčéąĖčÅ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (wake-up event), čéą░ą║ čćč鹊 ą┐čĆąŠčåąĄčüčüąŠčĆ ą╝ąŠąČąĄčé ąĮą░čģąŠą┤ąĖčéčīčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą┐ąŠąĮąĖąČąĄąĮąĮąŠą│ąŠ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąŠąĮ ąČą┤ąĄčé ą┐čĆąĖčģąŠą┤ą░ čüąŠąŠą▒čēąĄąĮąĖčÅ CAN. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ CAN wake-up event ą╝ąŠąČąĄčé čĆą░ąĘą▒čāą┤ąĖčéčī ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą║čĆąĖčüčéą░ą╗ą╗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ čĆąĄą│čāą╗čÅč鹊čĆ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ, čćč鹊ą▒čŗ ą▓čŗą▓ąĄčüčéąĖ ąĄą│ąŠ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ "ą▓čŗą║ą╗čÄč湥ąĮąŠ" (powered-down hibernate state).

ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą║ą░ąČą┤ąŠą│ąŠ čüąĄč鹥ą▓ąŠą│ąŠ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą║ą░ą║ ą┐čĆą░ą▓ąĖą╗ąŠ ąŠč湥ąĮčī ąČąĄčüčéą║ąĖąĄ. ą¤ąŠčŹč鹊ą╝čā ąĖąĮč鹥čĆč乥ą╣čü CAN ąŠą▒čŗčćąĮąŠ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 2 čćą░čüčéąĖ: ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĖ čéčĆą░ąĮčüąĖą▓ąĄčĆ (ą┐čĆąĖąĄą╝ąŠą┐ąĄčĆąĄą┤ą░čéčćąĖą║). ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┤ąĮąŠą╝čā ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčī čĆą░ąĘąĮčŗąĄ ą┤čĆą░ą╣ą▓ąĄčĆčŗ ąĖ čéąĖą┐čŗ čüąĄč鹥ą╣ CAN. ą£ąŠą┤čāą╗čī CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF50x ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čćą░čüčéčī ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ąĢą│ąŠ čüąĄč鹥ą▓ąŠą╣ ąĖąĮč鹥čĆč乥ą╣čü ą▓ą▓ąŠą┤ą░/ą▓čŗą▓ąŠą┤ą░ čüąŠčüč鹊ąĖčé ąĖąĘ ąŠą┤ąĮąŠą│ąŠ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą│ąŠ ą▓čŗčģąŠą┤ą░ ąĖ ąŠą┤ąĮąŠą│ąŠ ą┐čĆąĖąĄą╝ąĮąŠą│ąŠ ą▓čģąŠą┤ą░, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠą┤ą║ą╗čÄčćą░čÄčéčüčÅ ą║ čéčĆą░ąĮčüąĖą▓ąĄčĆčā ą╗ąĖąĮąĖąĖ CAN.

ąóą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ CAN ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ąŠčé čéą░ą║č鹊ą▓ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ ą┐čĆąŠčåąĄčüčüąŠčĆą░ (SCLK) č湥čĆąĄąĘ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗą╣ ą┤ąĄą╗ąĖč鹥ą╗čī, čéą░ą║ čćč鹊 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ ą║ą▓ą░čĆčåąĄą▓čŗą╣ čĆąĄąĘąŠąĮą░č鹊čĆ ą┤ą╗čÅ čŹč鹊ą│ąŠ ąĮąĄ čéčĆąĄą▒čāąĄčéčüčÅ.

[ą×ą▒ąĘąŠčĆ ą╝ąŠą┤čāą╗čÅ ąĖąĮč鹥čĆč乥ą╣čüą░ CAN]

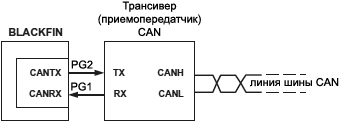

ąśąĮč鹥čĆč乥ą╣čü čü čłąĖąĮąŠą╣ CAN čŹč鹊 ą┐čĆąŠčüčéą░čÅ ą┤ą▓čāčģą┐čĆąŠą▓ąŠą┤ąĮą░čÅ ą╗ąĖąĮąĖčÅ. ąØą░ čĆąĖčü. 17-1 ą┐ąŠą║ą░ąĘą░ąĮąŠ čüąĖą╝ą▓ąŠą╗ąĖč湥čüą║ąŠąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮąĖąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ CAN čü čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą╝ CAN, ąĖ ąĮą░ čĆąĖčü. 17-2 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą╝ąŠą┤čāą╗čÅ CAN. ąÆčŗčģąŠą┤ (CANTX) ąĖ ą▓čģąŠą┤ (CANRX) ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin ą┐ąŠą┤ą║ą╗čÄčćą░čÄčéčüčÅ ą║ ą▓ąĮąĄčłąĮąĄą╝čā čéčĆą░ąĮčüąĖą▓ąĄčĆčā CAN čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ č湥čĆąĄąĘ ąĄą│ąŠ ą▓čŗą▓ąŠą┤čŗ TX and RX. ąÆčŗą▓ąŠą┤čŗ CANTX ąĖ CANRX čĆą░ą▒ąŠčéą░čÄčé ąĮą░ čāčĆąŠą▓ąĮčÅčģ TTL, ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ąĖą╝ ąŠą┐ąĄčĆą░čåąĖąĖ čéčĆą░ąĮčüąĖą▓ąĄčĆą░ ąĮą░ čäąĖąĘąĖč湥čüą║ąŠą╝ čüą╗ąŠąĄ čłąĖąĮčŗ CAN čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčé čüčéą░ąĮą┤ą░čĆčéčā ISO/DIS 11898.

ąĀąĖčü. 17-1. ą¤ąŠą┤ą║ą╗čÄč湥ąĮąĖąĄ ą╝ąŠą┤čāą╗čÅ CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF50x ą║ čéčĆą░ąĮčüąĖą▓ąĄčĆčā.

ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ, ąĄčüą╗ąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮ čéčĆą░ąĮčüąĖą▓ąĄčĆ: ą┤ą╗čÅ č鹊ą│ąŠ, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čłąĖąĮčŗ CAN ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą▓ čüą╗čāčćą░ąĄ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆą░, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ čüą┤ąĄą╗ą░čéčī ą┐ąŠą┤čéčÅąČą║čā PG2 (CANTX) ą║ čāčĆąŠą▓ąĮčÄ ą╗ąŠą│. 1. ą¤čĆąĖčćąĖąĮą░ ą▓ č鹊ą╝, ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░ PG2 ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ (ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ąĖą╗ąĖ ą▓ą║ą╗čÄč湥ąĮąĖčÅ ą┐ąĖčéą░ąĮąĖčÅ) ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ąĮą░čüčéčĆą░ąĖą▓ą░ąĄčéčüčÅ ą║ą░ą║ ąĮąŠąČą║ą░ ą┐ąŠčĆčéą░ GPIO, čĆą░ą▒ąŠčéą░čÄčēą░čÅ ąĮą░ ą▓čģąŠą┤, ą┐ąŠčŹč鹊ą╝čā ąĮą░ ą▓čģąŠą┤ąĄ TX čéčĆą░ąĮčüąĖą▓ąĄčĆą░ ą╝ąŠąČąĄčé ąŠą▒čĆą░ąĘąŠą▓ą░čéčīčüčÅ ą╗ąŠą│. 0 (ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī), čćč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą▓čĆąĄą╝ąĄąĮąĮąŠą╣ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĄ čłąĖąĮčŗ.

ą£ąŠąČąĮąŠ čéą░ą║ąČąĄ ą┐čĆąĄą┤čāčüą╝ąŠčéčĆąĄčéčī ą┤čĆčāą│ąŠą╣ čüą┐ąŠčüąŠą▒ ąŠčéą╝ąĄąĮčŗ ą▒ą╗ąŠą║ąĖčĆąŠą▓ą║ąĖ čłąĖąĮčŗ ą┐čĆąĖ čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░. ąØą░ą┐čĆąĖą╝ąĄčĆ, čéčĆą░ąĮčüąĖą▓ąĄčĆ PCA82C250 ą║ąŠą╝ą┐ą░ąĮąĖąĖ NXP ąĖą╝ąĄąĄčé čüą┐ąĄčåąĖą░ą╗čīąĮčŗą╣ ą▓čģąŠą┤ Rs ą┤ą╗čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéčīčÄ ą┐ąĄčĆąĄą║ą╗čÄč湥ąĮąĖčÅ ą▓čŗčģąŠą┤ą░ ąĖ ą┐ąĄčĆąĄą▓ąŠą┤ą░ čéčĆą░ąĮčüąĖą▓ąĄčĆą░ ą▓ čĆąĄąČąĖą╝ STANDBY. ąŁč鹊čé ą▓čģąŠą┤ ą╝ąŠąČąĮąŠ ą┐ąŠą┤čéčÅąĮčāčéčī ą║ ą╗ąŠą│. 1 čĆąĄąĘąĖčüč鹊čĆąŠą╝ pull-up, ąĖ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī ą║ ąĮąĄą╝čā ąŠą┤ąĖąĮ ąĖąĘ čüą▓ąŠą▒ąŠą┤ąĮčŗčģ ą┐ąŠčĆč鹊ą▓ GPIO ą┐čĆąŠčåąĄčüčüąŠčĆą░. ą¤čĆąĖ čüą▒čĆąŠčüąĄ ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ Rs ąŠą▒čĆą░ąĘčāąĄčéčüčÅ ą╗ąŠą│. 1, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐ąŠčĆčé GPIO ą▒čāą┤ąĄčé čĆą░ą▒ąŠčéą░čéčī ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą║ą░ą║ ą▓čģąŠą┤, čćč鹊 ąŠčéą║ą╗čÄčćąĖčé čéčĆą░ąĮčüąĖą▓ąĄčĆ ąŠčé čłąĖąĮčŗ CAN. ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▒čāą┤ąĄčé ą│ąŠč鹊ą▓ ą║ čĆą░ą▒ąŠč鹥, ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ąĮą░čüčéčĆąŠąĖčéčī čüą▓ąŠą╣ ą▓čŗą▓ąŠą┤ ą┐ąŠčĆčéą░, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ Rs, ą║ą░ą║ ą▓čŗčģąŠą┤, ąĖ ą┐ąŠą┤ą░čéčī ąĮą░ ąĮąĄą│ąŠ ą╗ąŠą│. 0. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ čéčĆą░ąĮčüąĖą▓ąĄčĆ ą░ą║čéąĖą▓ąĖčĆčāąĄčéčüčÅ ąĖ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčüčÅ ą║ čłąĖąĮąĄ CAN.

ąĀąĖčü. 17-2. ąæą╗ąŠą║-ą┤ąĖą░ą│čĆą░ą╝ą╝ą░ ą╝ąŠą┤čāą╗čÅ CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░ ADSP-BF50x.

ąĪąĖą│ąĮą░ą╗čŗ CANRX ąĖ CANTX ąĮą░čģąŠą┤čÅčéčüčÅ ąĮą░ GPIO Port G, ą▓čŗą▓ąŠą┤čŗ PG1 ąĖ PG2 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ. ąŻčĆąŠą▓ąĄąĮčī ą┤ą░ąĮąĮčŗčģ CAN ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮ ą╗ąĖą▒ąŠ ą║ą░ą║ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ (ą╗ąŠą│. 0), ą╗ąĖą▒ąŠ ą║ą░ą║ čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╣ (ą╗ąŠą│. 1). ąĪąŠčüč鹊čÅąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ CANTX - čĆąĄčåąĄčüčüąĖą▓ąĮąŠąĄ. ą¦č鹊 čéą░ą║ąŠąĄ "ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣" ąĖ "čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╣" čāčĆąŠą▓ąĮąĖ - ą┐ąŠą┤čĆąŠą▒ąĮąĄąĄ čüą╝. ąĮąĖąČąĄ ą▓ čĆą░ąĘą┤ąĄą╗ąĄ "ąæą░ąĘąŠą▓čŗąĄ čüą▓ąĄą┤ąĄąĮąĖčÅ ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ CAN".

ąÆčŗą▓ąŠą┤ PG1 (ą▓čģąŠą┤ CANRX) čéą░ą║ąČąĄ ą▓ąĮčāčéčĆąĖ čćąĖą┐ą░ čĆą░ąĘą▓ąĄą┤ąĄąĮ ąĮą░ ą░ą╗čīč鹥čĆąĮą░čéąĖą▓ąĮčŗą╣ ą▓čģąŠą┤ ąĘą░čģą▓ą░čéą░ čéą░ą╣ą╝ąĄčĆą░ ąŠą▒čēąĄą│ąŠ ąĮą░ąĘąĮą░č湥ąĮąĖčÅ 5 (alternated capture input TACI5 GP timer 5). ąŁč鹊 ą┤ą░ąĄčé čüą┐ąŠčüąŠą▒ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéą░ą╣ą╝ąĄčĆ 5 ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą│ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ čüą║ąŠčĆąŠčüčéąĖ ąĮą░ čłąĖąĮąĄ CAN ąĖ ąĄčæ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąĮą░čüčéčĆąŠą╣ą║ąĖ.

[ą×ą▒ą╗ą░čüčéčī CAN Mailbox]

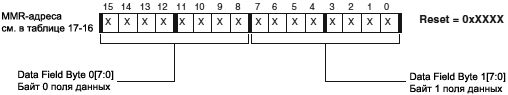

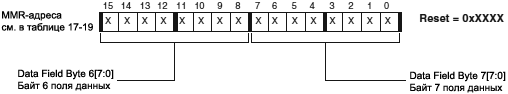

ą¤ąŠą╗ąĮąŠčäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ąĖą╝ąĄąĄčé ąĮą░ ą▒ąŠčĆčéčā 32 ą▒čāč乥čĆą░ ą┤ą╗čÅ čüąŠąŠą▒čēąĄąĮąĖą╣, ą║ąŠč鹊čĆčŗąĄ ąĮą░ąĘčŗą▓ą░čÄčé ą▓ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ CAN ą┐ąŠčćč鹊ą▓čŗą╝ąĖ čÅčēąĖą║ą░ą╝ąĖ (mailboxes). 8 čÅčēąĖą║ąŠą▓ ąČąĄčüčéą║ąŠ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮčŗ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĄčēąĄ 8 č鹊ą╗čīą║ąŠ ąĮą░ ą┐čĆąĖąĄą╝, ąĖ ąĄčēąĄ 16 ą╝ąŠąČąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī ą▓ ą╗čÄą▒ąŠąĄ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą░čĆčģąĖč鹥ą║čéčāčĆą░ ą╝ąŠą┤čāą╗čÅ CAN ąŠčüąĮąŠą▓ą░ąĮą░ ąĮą░ mailbox RAM ąĖąĘ 32 čÅč湥ąĄą║ ą┐ą░ą╝čÅčéąĖ. ąÜ čÅčēąĖą║ą░ą╝ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü CAN ąĖą╗ąĖ č湥čĆąĄąĘ ą┤ąŠčüčéčāą┐ čüąŠ čüč鹊čĆąŠąĮčŗ čÅą┤čĆą░ ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin. ąÜą░ąČą┤čŗą╣ čÅčēąĖą║ čüąŠčüč鹊ąĖčé ąĖąĘ ą▓ąŠčüčīą╝ąĖ 16-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą┤ą░ąĮąĮčŗčģ ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ąĖ ą┤ą▓čāčģ ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗčģ 16-ą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ą░čüą║ąĖ ą┐čĆąĖąĄą╝ą░ (acceptance mask registers), ą║ą░ąČą┤čŗą╣ ąĖąĘ ą║ąŠč鹊čĆčŗčģ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┐ąĄčĆąĄą┤ č鹥ą╝, ą║ą░ą║ čÅčēąĖą║ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮ. ą¤ąŠčüą║ąŠą╗čīą║čā ąŠą▒ą╗ą░čüčéčī čÅčēąĖą║ąŠą▓ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ ą║ą░ą║ RAM, ąĘąĮą░č湥ąĮąĖčÅ ą▓ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ ą┐ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ čÅą▓ą╗čÅąĄčéčüčÅ ąĮąĄąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╝. ąöą░ąĮąĮčŗąĄ ą┤ąĄą╗čÅčéčüčÅ ąĮą░ ą┐ąŠą╗čÅ, ą║ąŠč鹊čĆčŗąĄ ą▓ą║ą╗čÄčćą░čÄčé ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čüąŠąŠą▒čēąĄąĮąĖčÅ, ą╝ąĄčéą║čā ą▓čĆąĄą╝ąĄąĮąĖ, čüč湥čéčćąĖą║ ą▒ą░ą╣čé ąĖ ą┤ąŠ 8 ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ, ąĖ čéą░ą║ąČąĄ ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ąĖčé čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (čüą╝. čĆąĖčü. 17-3).

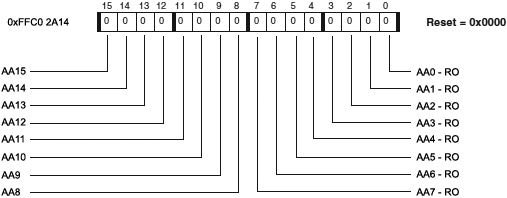

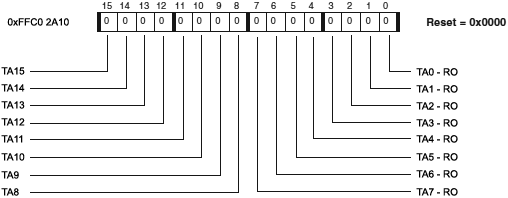

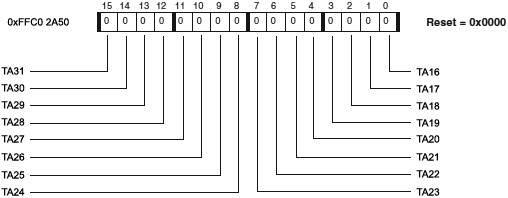

ąĀąĄą│ąĖčüčéčĆąŠą▓čŗąĄ ą┐ą░čĆčŗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čÅčēąĖą║ą░ (CAN mailbox identification, CAN_MBxx_ID0/CAN_MBxx_ID1) ą▓ą║ą╗čÄčćą░čÄčé:

ŌĆó 29-ą▒ąĖčéąĮčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ (ą▒ą░ąĘąŠą▓ą░čÅ čćą░čüčéčī ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ BASEID ą┐ą╗čÄčü čćą░čüčéčī, ąŠčéąĮąŠčüčÅčēą░čÅčüčÅ ą║ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╝čā ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā EXTID_LO/EXTID_HI).

ŌĆó ąæąĖčé čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą╝ą░čüą║ąĖ ą┐čĆąĖąĄą╝ą░ (acceptance mask enable, AME).

ŌĆó ąæąĖčé ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ čü ą┤ą░ą╗čīąĮąĄą│ąŠ čāąĘą╗ą░ čüąĄčéąĖ (remote transmission request, RTR).

ŌĆó ąæąĖčé čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ (identifier extension, IDE).

ąÆąĮąĖą╝ą░ąĮąĖąĄ: ąĮąĄ ąĘą░ą┐ąĖčüčŗą▓ą░ą╣č鹥 ą▓ ąŠą▒čŖąĄą║čé ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čüąŠąŠą▒čēąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ čÅčēąĖą║ čĆą░ąĘčĆąĄčłąĄąĮ (čé. ąĄ. ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé CAN_MCx).

ąĀąĖčü. 17-3. CAN Mailbox Area (čĆąĄą│ąĖčüčéčĆčŗ čÅčēąĖą║ą░ CAN).

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: xx ą▓ ąĖą╝ąĄąĮą░čģ čĆąĄą│ąĖčüčéčĆąŠą▓ (CAN_MBxx_ID0, CAN_MBxx_ID1 ąĖ ą┤čĆčāą│ąĖčģ) ąŠąĘąĮą░čćą░čÄčé ą┤ąĄčüčÅčéąĖčćąĮčŗą╣ ąĮąŠą╝ąĄčĆ čÅčēąĖą║ą░ ąŠčé 00 ą┤ąŠ 32.

ąöčĆčāą│ąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čÅčēąĖą║ą░ čüąŠą┤ąĄčƹȹ░čé:

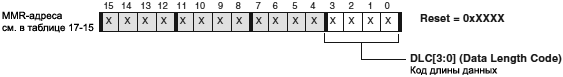

ŌĆó ąÜąŠą┤ ą┤ą╗ąĖąĮčŗ čüąŠąŠą▒čēąĄąĮąĖčÅ (data length code, DLC) ą▓ CAN_MBxx_LENGTH. ąĪčéą░čĆčłąĖąĄ 12 ą▒ąĖčé CAN_MBxx_LENGTH ą║ą░ąČą┤ąŠą│ąŠ mailbox ą┐ąŠą╝ąĄč湥ąĮčŗ ą║ą░ą║ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ. ąŁčéąĖ 12 ą▒ąĖčé ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 0. ąĢčüą╗ąĖ DLC ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ ąĘąĮą░č湥ąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ą┐čĆąĄą▓čŗčłą░ąĄčé 8, č鹊 ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ čüą▒čĆą░čüčŗą▓ą░ąĄčé ąĘąĮą░č湥ąĮąĖąĄ DLC ą▓ 8.

ŌĆó ąöąŠ 8 ą▒ą░ą╣čé ą┐ąŠą╗čÅ ą┤ą░ąĮąĮčŗčģ, ą║ąŠč鹊čĆčŗąĄ ą┐ąŠčüčŗą╗ą░čÄčéčüčÅ čüčéą░čĆčłąĖą╝ ą▒ą░ą╣č鹊ą╝ (MSB). ą×ąĮąĖ ąĮą░čģąŠą┤čÅčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ CAN_MBxx_DATA3, CAN_MBxx_DATA2, CAN_MBxx_DATA1, CAN_MBxx_DATA0, ą┤ą░ąĮąĮčŗąĄ čćąĖčéą░čÄčéčüčÅ ąŠčéčéčāą┤ą░ ąĮą░ ąŠčüąĮąŠą▓ąĄ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▒ą░ą╣č鹊ą▓, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą│ąŠ ą▓ ą┐ąŠą╗ąĄ DLC. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮ ąĖą╗ąĖ ą┐čĆąĖąĮčÅčé č鹊ą╗čīą║ąŠ 1 ą▒ą░ą╣čé (DLC=1), č鹊 ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮ ąĖąĘ čüčéą░čĆčłąĄą│ąŠ ą▒ą░ą╣čéą░ čĆąĄą│ąĖčüčéčĆą░ CAN_MBxx_DATA3.

ŌĆó 2 ą▒ą░ą╣čéą░ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (time stamp value, TSV) ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MBxx_TIMESTAMP.

ą×čüčéą░ą▓čłąĖąĄčüčÅ čĆąĄą│ąĖčüčéčĆčŗ ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ą╝ą░čüą║ąĄ ą┐čĆąĖąĄą╝ą░ (acceptance mask registers, CAN_AMxxH ąĖ CAN_AMxxL). ąĀą░ą▒ąŠčéą░ ą╝ą░čüą║ąĖ čĆą░ąĘčĆąĄčłą░ąĄčéčüčÅ, ą║ąŠą│ą┤ą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MBxx_ID1 čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé AME. ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░ ąŠą┐čåąĖčÅ čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠ ą▒ą░ą╣čéą░ą╝ ą┤ą░ąĮąĮčŗčģ "filtering on data field" (ą║ąŠą│ą┤ą░ DNM=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_CONTROL, ąĖ FDF=1 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą╝ą░čüą║ąĄ ą┐čĆąĖąĄą╝ą░), č鹊 ą▒ąĖčéčŗ EXTID_HI[15:0] čĆąĄą│ąĖčüčéčĆą░ CAN_MBxx_ID0 ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ ą║ąŠą┤ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (acceptance code, DFC) ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠ ą┤ą░ąĮąĮčŗą╝. ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ ą┐čĆąŠ čäąĖą╗čīčéčĆą░čåąĖčÄ ą┐ąŠ ID ąĖ ą┤ą░ąĮąĮčŗą╝ čüą╝. čĆą░ąĘą┤ąĄą╗ "ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĖąĄą╝".

[ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ CAN Mailbox]

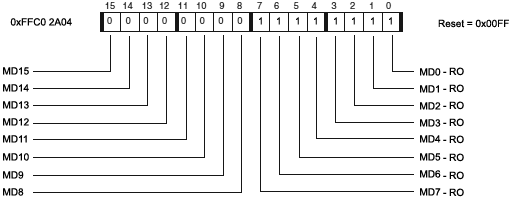

ą»čēąĖą║ąĖ čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ č湥čĆąĄąĘ MMR-čĆąĄą│ąĖčüčéčĆčŗ, ą║ąŠč鹊čĆčŗąĄ čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ čĆąĄą│ąĖčüčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ čüčéą░čéčāčüą░ ą┤ą╗čÅ 32 čÅčēąĖą║ąŠą▓. ąÜą░ąČą┤čŗą╣ ą▒ąĖčé ą▓ čŹčéąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ąŠą┤ąĖąĮ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čÅčēąĖą║. ą¤ąŠčüą║ąŠą╗čīą║čā MMR-čĆąĄą│ąĖčüčéčĆčŗ CAN ą▓čüąĄ 16-ą▒ąĖčéąĮčŗąĄ, č鹊 ą┤ą╗čÅ ąŠą▒ąĄčüą┐ąĄč湥ąĮąĖčÅ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéąĖ ą┤ą╗čÅ ą▓čüąĄčģ 32 čÅčēąĖą║ąŠą▓ čéčĆąĄą▒čāčÄčéčüčÅ ą┐ą░čĆčŗ čéą░ą║ąĖčģ čĆąĄą│ąĖčüčéčĆąŠą▓. ą»čēąĖą║ąĖ 0-15 ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāčÄčéčüčÅ / ą╝ąŠąĮąĖč鹊čĆčÅčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ, čā ą║ąŠč鹊čĆčŗčģ ąĖą╝ąĄąĮą░ čü čüčāčäčäąĖą║čüąŠą╝ 1. ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ čÅčēąĖą║ąĖ 16-31 ąĖčüą┐ąŠą╗čīąĘčāčÄčé č鹥 ąČąĄ ąĖą╝ąĄąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓, ąĮąŠ čü čüčāčäčäąĖą║čüąŠą╝ 2. ąØą░ą┐čĆąĖą╝ąĄčĆ, čĆąĄą│ąĖčüčéčĆčŗ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (CAN mailbox direction registers, CAN_MDx) ą┤ąŠą╗ąČąĮčŗ čāą┐čĆą░ą▓ą╗čÅčéčī čÅčēąĖą║ą░ą╝ąĖ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 17-4.

ąĀąĖčü. 17-4. ą¤ą░čĆčŗ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN.

ąśą╝ąĄčÄčéčüčÅ čüą╗ąĄą┤čāčÄčēąĖąĄ ą┐ą░čĆčŗ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čÅčēąĖą║ą░ą╝ąĖ:

CAN_MC1,

CAN_MC2 |

ąĀąĄą│ąĖčüčéčĆčŗ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ (mailbox enable registers). |

CAN_MD1,

CAN_MD2 |

ąĀąĄą│ąĖčüčéčĆčŗ ąĮą░ą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (mailbox direction registers). |

CAN_TA1,

CAN_TA2 |

ąĀąĄą│ąĖčüčéčĆčŗ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit acknowledge registers). |

CAN_AA1,

CAN_AA2 |

ąĀąĄą│ąĖčüčéčĆčŗ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąŠą▒čĆčŗą▓ą░ (abort acknowledge registers). |

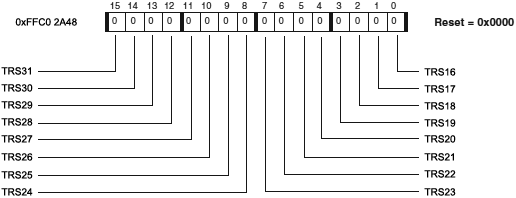

CAN_TRS1,

CAN_TRS2 |

ąĀąĄą│ąĖčüčéčĆčŗ čāčüčéą░ąĮąŠą▓ą║ąĖ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (transmit request set registers). |

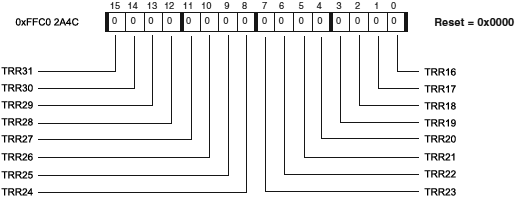

CAN_TRR1,

CAN_TRR2 |

ąĀąĄą│ąĖčüčéčĆčŗ čüą▒čĆąŠčüą░ ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā (transmit request reset registers). |

CAN_RMP1,

CAN_RMP2 |

ąĀąĄą│ąĖčüčéčĆčŗ ąŠąČąĖą┤ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ čüąŠąŠą▒čēąĄąĮąĖčÅ (receive message pending registers). |

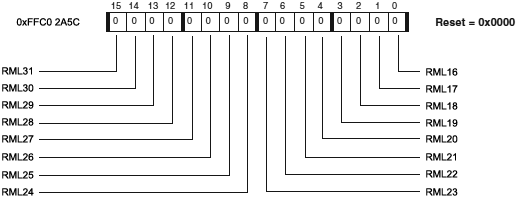

CAN_RML1,

CAN_RML2 |

ąĀąĄą│ąĖčüčéčĆčŗ ą┐ąŠč鹥čĆąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĮą░ ą┐čĆąĖąĄą╝ąĄ (receive message lost registers). |

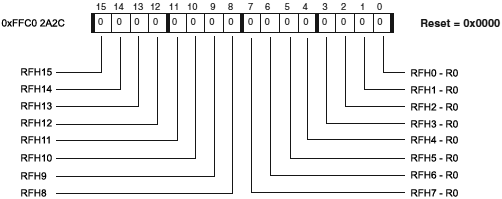

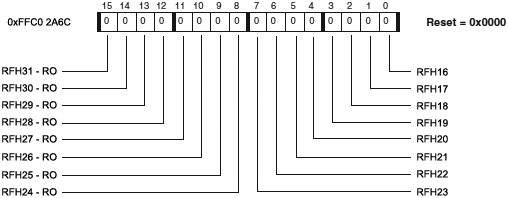

CAN_RFH1,

CAN_RFH2 |

ąĀąĄą│ąĖčüčéčĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ čäčĆąĄą╣ą╝ą░ RTR (remote frame handling registers). |

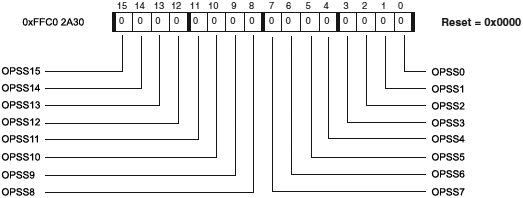

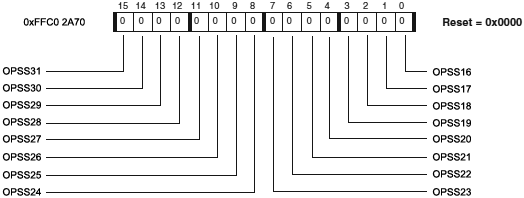

CAN_OPSS1,

CAN_OPSS2 |

ąĀąĄą│ąĖčüčéčĆčŗ ąĘą░čēąĖčéčŗ ąŠčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüąĖ / ąŠą┤ąĖąĮąŠčćąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ (overwrite protection/single shot transmission registers). |

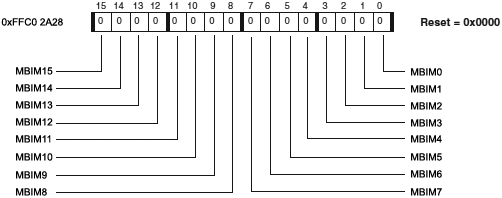

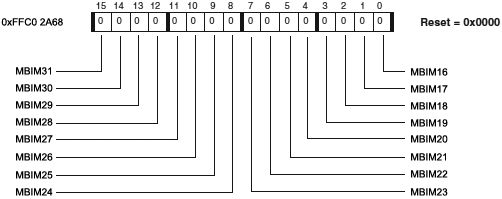

CAN_MBIM1,

CAN_MBIM2 |

ąĀąĄą│ąĖčüčéčĆčŗ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (mailbox interrupt mask registers). |

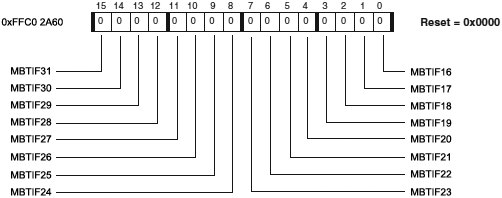

CAN_MBTIF1,

CAN_MBTIF2 |

ąĀąĄą│ąĖčüčéčĆčŗ čäą╗ą░ą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (mailbox transmit interrupt flag registers). |

CAN_MBRIF1,

CAN_MBRIF2 |

ąĀąĄą│ąĖčüčéčĆčŗ čäą╗ą░ą│ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (mailbox receive interrupt flag registers). |

ą¤ąŠčüą║ąŠą╗čīą║čā čÅčēąĖą║ąĖ 24ŌĆō31 čĆą░ą▒ąŠčéą░čÄčé č鹊ą╗čīą║ąŠ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā, ąĖ čÅčēąĖą║ąĖ 0ŌĆō7 č鹊ą╗čīą║ąŠ ąĮą░ ą┐čĆąĖąĄą╝, č鹊 ą╝ą╗ą░ą┤čłąĖąĄ 8 ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čü čüčāčäčäąĖą║čüąŠą╝ "1" ąĖ čüčéą░čĆčłąĖąĄ 8 ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čü čüčāčäčäąĖą║čüąŠą╝ "2" ąĖąĮąŠą│ą┤ą░ ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮčŗ, ąĖ ąĖčģ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčēąĄąĮąŠ.

[ąæą░ąĘąŠą▓čŗąĄ čüą▓ąĄą┤ąĄąĮąĖčÅ ąŠ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ CAN]

ąźąŠčéčÅ ą▓čŗą▓ąŠą┤čŗ CANRX ąĖ CANTX čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ TTL-čüąŠą▓ą╝ąĄčüčéąĖą╝čŗąĄ čüąĖą│ąĮą░ą╗čŗ, ą┤čĆą░ą╣ą▓ąĄčĆ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą░čüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗą╣ (čüą╝. čĆąĖčü. 17-1). ą¤ąŠą┤čéčÅąČą║ą░ ą║ ą╗ąŠą│. 0 (ąĮąĖąČąĮąĖą╣ ą║ą╗čÄčć ą┤čĆą░ą╣ą▓ąĄčĆą░) ą┤ą╗čÅ ą▓čŗčģąŠą┤ą░ CANTX ą╝ąŠčēąĮą░čÅ (ą▓čŗą┤ąĄčƹȹĖą▓ą░ąĄčé ą▒ąŠą╗čīčłąŠą╣ ą▓ąĮąĄčłąĮąĖą╣ ą▓č鹥ą║ą░čÄčēąĖą╣ č鹊ą║), ą░ ą┐ąŠą┤čéčÅąČą║ą░ ą║ ą╗ąŠą│. 1 (ą▓ąĄčĆčģąĮąĖą╣ ą║ą╗čÄčć ą┤čĆą░ą╣ą▓ąĄčĆą░) čüą╗ą░ą▒ą░čÅ (ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄą╝čŗą╣ ą▓čŗč鹥ą║ą░čÄčēąĖą╣ č鹊ą║ ą╝ą░ą╗). ąŁč鹊 čüą┤ąĄą╗ą░ąĮąŠ čüą┐ąĄčåąĖą░ą╗čīąĮąŠ ą┤ą╗čÅ ąŠčĆą│ą░ąĮąĖąĘą░čåąĖąĖ čéą░ą║ ąĮą░ąĘčŗą▓ą░ąĄą╝ąŠą│ąŠ ą╝ąŠąĮčéą░ąČąĮąŠą│ąŠ ąśąøąś ą┐čĆąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą╝ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĖ ą▓čŗčģąŠą┤ąŠą▓ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą░ą║čéąĖą▓ąĮčŗą╣ ą╗ąŠą│. 0 čüą▓čÅąĘčŗą▓ą░ąĄčéčüčÅ čü "ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╝" čüąŠčüč鹊čÅąĮąĖąĄą╝ ą▒ąĖčéą░, ą┐ąŠčüą║ąŠą╗čīą║čā ąŠąĮąŠ ąŠčéą╝ąĄąĮčÅąĄčé ą╗čÄą▒ąŠą╣ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1, ąĖ čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 1 čüą▓čÅąĘčŗą▓ą░ąĄčéčüčÅ čü "čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╝" čüąŠčüč鹊čÅąĮąĖąĄą╝, ą┐ąŠč鹊ą╝čā čćč鹊 ąĄą│ąŠ ą╝ąŠąČąĄčé ąŠčéą╝ąĄąĮąĖčéčī čāčĆąŠą▓ąĄąĮčī ą╗ąŠą│. 0. ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī CAN ą┐ą░čüčüąĖą▓ąĮčŗą╣, č鹊 ą▓čŗą▓ąŠą┤ CANTX ą▓čüąĄą│ą┤ą░ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čüąŠčüč鹊čÅąĮąĖąĖ ą╗ąŠą│. 1. ąĢčüą╗ąĖ 2 čāąĘą╗ą░ čłąĖąĮčŗ CAN ą┐ąĄčĆąĄą┤ą░čÄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ, č鹊 ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ ą▒ąĖčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░ąĄčé čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╣.

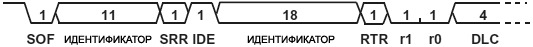

ą¤čĆąŠč鹊ą║ąŠą╗ CAN ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, čćč鹊 ą▓čüąĄ čāąĘą╗čŗ ą┐čŗčéą░čÄčéčüčÅ ąŠčéą┐čĆą░ą▓ąĖčéčī čüą▓ąŠą╣ čäčĆąĄą╣ą╝ čüąŠąŠą▒čēąĄąĮąĖčÅ ą┐ąŠ čłąĖąĮąĄ č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ ą▒čŗą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ, čćč鹊 čłąĖąĮą░ CAN čüčéą░ą╗ą░ čüą▓ąŠą▒ąŠą┤ąĮą░. ąśąĮą┤ąĖą║ą░č鹊čĆ start of frame (SOF) čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ąŠ ąĮą░čćą░ą╗ąĄ ąĮąŠą▓ąŠą│ąŠ čäčĆąĄą╣ą╝ą░. ąóąŠą│ą┤ą░ ą║ą░ąČą┤čŗą╣ čāąĘąĄą╗ CAN ąĮą░čćąĖąĮą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā čüą▓ąŠąĄą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ, ąĮą░čćąĖąĮą░čÅ čü ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ čüąŠąŠą▒čēąĄąĮąĖčÅ ID. ąÆąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą░ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ą▓čŗą▓ąŠą┤ CANRX, čćč鹊ą▒čŗ ą┐čĆąŠą▓ąĄčĆąĖčéčī, čćč鹊 ąĄą│ąŠ čāčĆąŠą▓ąĄąĮčī čéą░ą║ąŠą╣ ąČąĄ, ą║ą░ą║ ąĖą╝ ą▒čŗą╗ ą▓čŗčüčéą░ą▓ą╗ąĄąĮ ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CANTX. ąŁč鹊 ą║ą░ą║ čĆą░ąĘ č鹊 ą╝ąĄčüč鹊, ą│ą┤ąĄ ąŠą┐čĆą░ą▓ą┤čŗą▓ą░čÄčé čüą▓ąŠąĄ ąĮą░ąĘą▓ą░ąĮąĖąĄ ąĖą╝ąĄąĮą░ čāčĆąŠą▓ąĮąĄą╣. ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ čāąĘąĄą╗ ą┐ąŠą╝ąĄčēą░ąĄčé čĆąĄčåąĄčüčüąĖą▓ąĮčāčÄ ą╗ąŠą│. 1 ąĮą░ CANTX, ąĖ ą┐čĆąĖ čŹč鹊ą╝ ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ 0 ąĮą░ ą▓čŗą▓ąŠą┤ąĄ CANRX, č鹊 ąĄą╝čā ąĖąĘą▓ąĄčüčéąĮąŠ, čćč鹊 ą┤čĆčāą│ąŠą╣ čāąĘąĄą╗ ą┐ąŠą╝ąĄčüčéąĖą╗ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ ą▒ąĖčé ąĮą░ čłąĖąĮčā, ąĖ čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čā ą┤čĆčāą│ąŠą│ąŠ čāąĘą╗ą░ ą┐čĆąĖąŠčĆąĖč鹥čé ą▓čŗčłąĄ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ąĄčüą╗ąĖ čāąĘą╗ąŠą╝ ą▒čŗą╗ąŠ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ CANRX čéą░ą║ąŠąĄ ąČąĄ, ą║ą░ą║ ą▒čŗą╗ąŠ ąĖą╝ ą▓čŗčüčéą░ą▓ą╗ąĄąĮąŠ ąĮą░ CANTX, č鹊 čāąĘąĄą╗ ą┐čĆąŠą┤ąŠą╗ąČą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā, ąĖąĮą░č湥 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN čāąĘą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, čćč鹊 ąĮą░ čŹč鹊ą╝ čäčĆąĄą╣ą╝ąĄ ą░čĆą▒ąĖčéčĆą░ąČ ą┐ąŠč鹥čĆčÅąĮ, ą┐čĆąĄą║čĆą░čēą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā ąĖ ą┐čĆąĄą┤ą┐čĆąĖąĮąĖą╝ą░ąĄčé ą┤ąĄą╣čüčéą▓ąĖčÅ ą┐ąŠ ąŠąČąĖą┤ą░ąĮąĖčÄ ą┐ąŠą┐čŗčéą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ čüą▓ąŠąĄą│ąŠ čäčĆąĄą╣ą╝ą░ ą▓ čüą╗ąĄą┤čāčÄčēąĖą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čłąĖąĮą░ CAN ąŠčüą▓ąŠą▒ąŠą┤ąĖčéčüčÅ. ąĪą╝. čĆąĖčü. 17-5, ą│ą┤ąĄ ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą┐ąŠą║ą░ąĘą░ąĮą░ čüčéčĆčāą║čéčāčĆą░ čäčĆąĄą╣ą╝ą░ CAN.

ąĀąĖčü. 17-5. ąĪčéą░ąĮą┤ą░čĆčéąĮčŗą╣ čäčĆąĄą╣ą╝ CAN.

SOF Start Of Frame, čüąĖą│ąĮą░ą╗ ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (ąŠą┤ąĖąĮ ą▒ąĖčé = 0).

RTR Remote Transmission Request, ąĘą░ą┐čĆąŠčü ą┤ą░ą╗čīąĮąĄą│ąŠ čüąĄč鹥ą▓ąŠą│ąŠ čāąĘą╗ą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ą╗ąŠą║ą░ą╗čīąĮčŗą╝ čāąĘą╗ąŠą╝ (REMOTE FRAME = 1).

IDE IDentifier Extension (ą┤ą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░ = 1).

r0 ąĘą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ ą┤ą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĖčÅ ą▓ ą▒čāą┤čāčēąĄą╝.

DLC Data Length Control (ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą▒ą░ą╣čé ą┤ą░ąĮąĮčŗčģ ą▓ čäčĆąĄą╣ą╝ąĄ).

CRC ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ ą▒ąĖčé čäčĆąĄą╣ą╝ą░.

ACK ACKnowledge (ą┐čĆąĖąĄą╝ąĮąĖą║ ą┤ą╗čÅ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą▓čŗčüčéą░ą▓ą╗čÅąĄčé ąĘą┤ąĄčüčī ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ ą▒ąĖčé).

EOF End Of Frame, ą║ąŠąĮąĄčå čäčĆąĄą╣ą╝ą░ (ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī ąĖąĘ 7 čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčé = 1111111).

IFS InterFrame Space, ąĖąĮč鹥čĆą▓ą░ą╗ ą╝ąĄąČą┤čā čäčĆąĄą╣ą╝ą░ą╝ąĖ (3 čĆąĄčåąĄčüčüąĖą▓ąĮčŗčģ ą▒ąĖčéą░ = 111).

ąĀąĖčü. 17-5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▒ą░ąĘąŠą▓čŗą╣ čäčĆąĄą╣ą╝ čü 11-ą▒ąĖčéąĮčŗą╝ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą╝. ą¤ąŠčüą╗ąĄ SOF ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ ąĖą┤ąĄčé ą▒ąĖčé RTR, ą║ąŠč鹊čĆčŗą╣ ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čüąŠą┤ąĄčƹȹĖčé ą╗ąĖ čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗąĄ (data frame), ąĖą╗ąĖ ąČąĄ čŹč鹊 ąĘą░ą┐čĆąŠčü ąĮą░ ą┐ąŠą╗čāč湥ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, čüą▓čÅąĘą░ąĮąĮčŗčģ čü ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą╝ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ąŠ čäčĆąĄą╣ą╝ąĄ, ą║ąŠč鹊čĆčŗą╣ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ (remote frame).

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ąĖąĘ-ąĘą░ ąĮąĄąŠčéčŖąĄą╝ą╗ąĄą╝ąŠą╣ ą┐čĆąĖčĆąŠą┤čŗ ą┐čĆąŠč鹊ą║ąŠą╗ą░ CAN ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ ą▒ąĖčé ą▓ ą┐ąŠą╗ąĄ RTR ą▓čŗąĖą│čĆą░ąĄčé ą░čĆą▒ąĖčéčĆą░ąČ čā ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą░ą╗čīąĮąĄą│ąŠ čāąĘą╗ą░ (remote frame request, RTR=1) ą┤ą╗čÅ č鹊ą│ąŠ ąČąĄ čüą░ą╝ąŠą│ąŠ ID čüąŠąŠą▒čēąĄąĮąĖčÅ, čéą░ą║ čćč鹊 čäčĆąĄą╣ą╝ RTR ąĖą╝ąĄąĄčé ą┐čĆąĖąŠčĆąĖč鹥čé ąĮąĖąČąĄ, č湥ą╝ ąŠą▒čŗčćąĮčŗą╣ čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ.

ąĪą╗ąĄą┤čāčÄčēąĄąĄ ą┐ąŠą╗ąĄ čŹč鹊 IDE. ąÜąŠą│ą┤ą░ čŹč鹊čé ą▒ąĖčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čŹč鹊 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé, čćč鹊 ą┐ąĄčĆąĄą┤ą░ąĄčéčüčÅ čüąŠąŠą▒čēąĄąĮąĖąĄ čü čĆą░čüčłąĖčĆąĄąĮąĮčŗą╝ čäčĆąĄą╣ą╝ąŠą╝, čā ą║ąŠč鹊čĆąŠą│ąŠ ąĮąĄ 11-ą▒ąĖčéąĮčŗą╣, ą░ 29-ą▒ąĖčéąĮčŗą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ. ąÆ čĆą░čüčłąĖčĆąĄąĮąĮąŠą╝ čäčĆąĄą╣ą╝ąĄ (extended frame) ą┐ąĄčĆą▓ą░čÅ čćą░čüčéčī čüąŠąŠą▒čēąĄąĮąĖčÅ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 17-6.

ąĀąĖčü. 17-6. ąĀą░čüčłąĖčĆąĄąĮąĮčŗą╣ čäčĆąĄą╣ą╝ CAN čü 29-ą▒ąĖčéąĮčŗą╝ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą╝ (ą┐ąŠą║ą░ąĘą░ąĮą░ ą┐ąĄčĆą▓ą░čÅ čćą░čüčéčī čäčĆąĄą╣ą╝ą░, ąŠčéą╗ąĖčćą░čÄčēą░čÅčüčÅ ąŠčé čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░ čü 11-ą▒ąĖčéąĮčŗą╝ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą╝).

ąÜą░ą║ čŹč鹊 ą▒čŗą╗ąŠ čü ą┐ąŠą╗ąĄą╝ RTR, ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗą╣ ą▒ąĖčé ą▓ ą┐ąŠą╗ąĄ IDE ą▓čŗąĖą│čĆą░ąĄčé ą░čĆą▒ąĖčéčĆą░ąČ ą┐ąĄčĆąĄą┤ čĆą░čüčłąĖčĆąĄąĮąĮčŗą╝ čäčĆąĄą╣ą╝ąŠą╝. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čüčéą░ąĮą┤ą░čĆčéąĮčŗąĄ čäčĆąĄą╣ą╝čŗ ąĖą╝ąĄčÄčé ą┐čĆąĖąŠčĆąĖč鹥čé ą▓čŗčłąĄ, č湥ą╝ čĆą░čüčłąĖčĆąĄąĮąĮčŗąĄ čäčĆąĄą╣ą╝čŗ. ąæąĖčé, ąĘą░ą╝ąĄąĮčÅčÄčēąĖą╣ ą▒ąĖčé RTR (substitute remote request, SRR, ą║ąŠč鹊čĆčŗą╣ ą▓čüąĄą│ą┤ą░ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą║ą░ą║ čĆąĄčåąĄčüčüąĖą▓ąĮčŗą╣), čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąĮčŗąĄ ą▒ąĖčéčŗ r0 ąĖ r1 (ą▓čüąĄą│ą┤ą░ ąŠčéą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ ą║ą░ą║ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮčŗąĄ) ąĖ ą║ąŠąĮčéčĆąŠą╗čīąĮą░čÅ čüčāą╝ą╝ą░ (CRC) ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣.

[ąĀą░ą▒ąŠčéą░ CAN]

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠčåąĄčüčüąŠčĆ ą▓čŗčģąŠą┤ąĖčé ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░ ąĖą╗ąĖ ą│ąĖą▒ąĄčĆąĮą░čåąĖąĖ. ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą░ą┐ą┐ą░čĆą░čéčāčĆčŗ ą╝ąŠąČąĮąŠ ą┐ąŠą╝ąĄąĮčÅčéčī č鹊ą╗čīą║ąŠ č鹊ą│ą┤ą░, ą║ąŠą│ą┤ą░ CAN ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ čŹč鹊ą╝ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ą¤ąĄčĆąĄą┤ ąĖąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖąĄą╣ čüą░ą╝ąĖčģ čÅčēąĖą║ąŠą▓ ąĮčāąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒ąĖčéą░ CAN, čćč鹊ą▒čŗ čüą║ąŠčĆąŠčüčéčī čĆą░ą▒ąŠčéčŗ CAN ą▒čŗą╗ą░ ąŠąČąĖą┤ą░ąĄą╝ąŠą╣, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą┤čĆčāą│ąĖą╝ čāąĘą╗ą░ą╝, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╝ ą║ čłąĖąĮąĄ CAN.

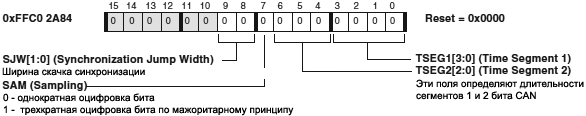

ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒ąĖčéą░. ąŻ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ CAN ąĮąĄčé čüą▓ąŠąĄą│ąŠ čüąŠą▒čüčéą▓ąĄąĮąĮąŠą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąÆą╝ąĄčüč鹊 čŹč鹊ą│ąŠ čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ CAN ą┐ąŠą╗čāčćą░ąĄčéčüčÅ ąĖąĘ čćą░čüč鹊čéčŗ čüąĖčüč鹥ą╝ąĮąŠą╣ čłąĖąĮčŗ (SCLK) ąĮą░ ąŠčüąĮąŠą▓ą░ąĮąĖąĖ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝ąŠą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą║ą▓ą░ąĮč鹊ą▓ ą▓čĆąĄą╝ąĄąĮąĖ (time quanta). ą¤ą░čĆą░ą╝ąĄčéčĆ Time Quantum (TQ) ą▓čŗčćąĖčüą╗čÅąĄčéčüčÅ ą┐ąŠ č乊čĆą╝čāą╗ąĄ TQ = (BRP+1)/SCLK, ą│ą┤ąĄ BRP čŹč鹊 10-ą▒ąĖčéąĮąŠąĄ ą┐ąŠą╗ąĄ BRP čĆąĄą│ąĖčüčéčĆą░ CAN_CLOCK. ąźąŠčéčÅ ą┐ąŠą╗ąĄ BRP ą╝ąŠąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą▓ ą╗čÄą▒ąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ, čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąŠą╗čīčłąĄąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠąĄ 4, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮą░ą║ą╗ą░ą┤čŗą▓ą░čÄčéčüčÅ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąĮą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéąĖ ą▒ąĖčéą░, ą║ąŠą│ą┤ą░ BRP ą╝ąĄąĮčīčłąĄ 4.

ąĀąĄą│ąĖčüčéčĆ CAN_CLOCK ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé ąĘąĮą░č湥ąĮąĖąĄ TQ, ąĖ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ą║ą▓ą░ąĮč鹊ą▓ ą▓čĆąĄą╝ąĄąĮąĖ čüąŠčüčéą░ą▓ą╗čÅčÄčé ą┤ą╗ąĖč鹥ą╗čīąĮąŠčüčéčī ą▒ąĖčéą░ ąĮą░ čłąĖąĮąĄ CAN. ąĀąĄą│ąĖčüčéčĆ CAN_TIMING čāą┐čĆą░ą▓ą╗čÅąĄčé ąĮąŠą╝ąĖąĮą░ą╗čīąĮčŗą╝ ą▓čĆąĄą╝ąĄąĮąĄą╝ ą▒ąĖčéą░ ąĖ č鹊čćą║čā ą▓čŗą▒ąŠčĆą║ąĖ ąŠčéą┤ąĄą╗čīąĮčŗčģ ą▒ąĖčé ą▓ ą┐čĆąŠč鹊ą║ąŠą╗ąĄ CAN. ąĀąĖčü. 17-7 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé 3 čäą░ąĘčŗ ą▒ąĖčéą░ CAN - čüąĄą│ą╝ąĄąĮčé čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, čüąĄą│ą╝ąĄąĮčé ą┐ąĄčĆąĄą┤ č鹊čćą║ąŠą╣ ą▓čŗą▒ąŠčĆą║ąĖ ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ ąĖ čüąĄą│ą╝ąĄąĮčé ą┐ąŠčüą╗ąĄ č鹊čćą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ.

ąĀąĖčü. 17-7. ąóčĆąĖ čäą░ąĘčŗ ą▒ąĖčéą░ CAN.

ąöą╗ąĖč鹥ą╗čīąĮąŠčüčéčī čüąĄą│ą╝ąĄąĮčéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą▓čüąĄą│ą┤ą░ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąŠ čĆą░ą▓ąĮą░ 1 TQ. ąŁč鹊 čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ čāąĘą╗ąŠą▓ ąĮą░ čłąĖąĮąĄ CAN. ąÆčüąĄ ą┐ąĄčĆąĄą┐ą░ą┤čŗ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ąŠą▓ ąŠąČąĖą┤ą░čÄčéčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ čŹč鹊ą│ąŠ čüąĄą│ą╝ąĄąĮčéą░.

ą¤ąŠą╗čÅ TSEG1 ąĖ TSEG2 čĆąĄą│ąĖčüčéčĆą░ CAN_TIMING čāą┐čĆą░ą▓ą╗čÅčÄčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ TQ, ą║ąŠč鹊čĆčŗąĄ ą▓čģąŠą┤čÅčé ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ąĖąĮč鹥čĆą▓ą░ą╗čŗ ą▒ąĖčé CAN, ąĖ ąŠčé čŹč鹊ą│ąŠ ąĘą░ą▓ąĖčüąĖčé ą┐ąŠą╗čāč湥ąĮąĮą░čÅ čüą║ąŠčĆąŠčüčéčī ą▒ąĖčé CAN. ąØąŠą╝ąĖąĮą░ą╗čīąĮąŠąĄ ą▓čĆąĄą╝čÅ ą▒ąĖčéą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗čāč湥ąĮą░ ą┐ąŠ č乊čĆą╝čāą╗ąĄ:

tBIT = TQ * (1 + (1 + TSEG1) + (1 + TSEG2))

ąöą╗čÅ ą▒ąĄąĘąŠą┐ą░čüąĮąŠą│ąŠ ą┐čĆąĖąĄą╝ą░ ą▓ čäąĖąĘąĖč湥čüą║ąĖčģ čüąĄčéčÅčģ č鹊čćą║ą░ ą▓čŗą▒ąŠčĆą║ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄčéčüčÅ ą┐ąŠą╗ąĄą╝ TSEG1. ą¤ąŠą╗ąĄ TSEG2 čüąŠą┤ąĄčƹȹĖčé ą║ąŠą╗ąĖč湥čüčéą▓ąŠ TQ, čéčĆąĄą▒čāąĄą╝ąŠąĄ ą┤ą╗čÅ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░. ą¦ą░čüč鹊 čüą░ą╝ą░čÅ ą╗čāčćčłą░čÅ ąĮą░ą┤ąĄąČąĮąŠčüčéčī ą┤ąŠčüčéąĖąČąĖą╝ą░ čü č鹊čćą║ą░ą╝ąĖ ą▓čŗą▒ąŠčĆą║ąĖ, čĆą░čüą┐ąŠą╗ąŠąČąĄąĮąĮčŗą╝ąĖ ą▓ ą▓ąĄčĆčģąĮąĄą╝ 80% ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░. ąØąĄ ąĖčüą┐ąŠą╗čīąĘčāą╣č鹥 č鹊čćą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ ą╝ąĄąĮčīčłąĄ 50%. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, TSEG1 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▓čüąĄą│ą┤ą░ ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮčŗą╝ TSEG2.

ą£ąŠą┤čāą╗čī CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░ ąĮąĄ čĆą░ąĘą╗ąĖčćą░ąĄčé čüąĄą│ą╝ąĄąĮčé čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ (propagation segment) ąĖ čüąĄą│ą╝ąĄąĮčé čäą░ąĘčŗ 1 (phase segment 2), ą║ą░ą║ čŹč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąŠ ą▓ čüčéą░ąĮą┤ą░čĆč鹥. ąŚąĮą░č湥ąĮąĖąĄ TSEG1 ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąŠ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čŹčéąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓. ąŚąĮą░č湥ąĮąĖąĄ TSEG2 ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮąŠ ą┤ą╗čÅ ąĮą░čüčéčĆąŠą╣ą║ąĖ čüąĄą│ą╝ąĄąĮčéą░ čäą░ąĘčŗ 2 (phase segment 2).

ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī CAN ąŠą┐čĆąĄą┤ąĄą╗ąĖą╗ ą┐ąĄčĆąĄčģąŠą┤ ąŠčé čĆąĄčåąĄčüčüąĖą▓ąĮąŠą│ąŠ ą║ ą┤ąŠą╝ąĖąĮą░ąĮčéąĮąŠą╝čā ą▒ąĖčéčā ą▓ąĮąĄ čüąĄą│ą╝ąĄąĮčéą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ, č鹊 ąŠąĮ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą┐ąĄčĆąĄąĮąŠčüąĖčé č鹊čćą║čā ą▓čŗą▒ąŠčĆą║ąĖ čéą░ą║, čćč鹊 ą▒čāą┤ąĄčé ą▓čüąĄ ąĄčēąĄ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčīčüčÅ ą▒ąĖčé CAN. ą¤ąŠą╗ąĄ čłąĖčĆąĖąĮčŗ ą┐čĆčŗąČą║ą░ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ (synchronization jump width, SJW) ąĘą░ą┤ą░ąĄčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ą║ąŠą╗ąĖč湥čüčéą▓ąŠ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ TQ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ąŠčé 1 ą┤ąŠ 4 (SJW + 1), č湥ą╝ čĆą░ąĘčĆąĄčłą░čÄčéčüčÅ ą┐ąŠą┐čŗčéą║ąĖ ą┐ąŠą▓č鹊čĆąĮąŠą╣ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ. ąŚąĮą░č湥ąĮąĖąĄ SJW ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą┐čĆąĄą▓čŗčłą░čéčī TSEG2 ąĖą╗ąĖ TSEG1. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, čäčāąĮą┤ą░ą╝ąĄąĮčéą░ą╗čīąĮąŠąĄ ą┐čĆą░ą▓ąĖą╗ąŠ ą┤ą╗čÅ ąĘą░ą┐ąĖčüąĖ ą▓ CAN_TIMING čüą╗ąĄą┤čāčÄčēąĄąĄ:

SJW Ōēż TSEG2 Ōēż TSEG1

ąÆ ą┤ąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ ą║ čŹč鹊ą╝čā čäčāąĮą┤ą░ą╝ąĄąĮčéą░ą╗čīąĮąŠą╝čā ą┐čĆą░ą▓ąĖą╗čā čüąĄą│ą╝ąĄąĮčé čäą░ąĘčŗ 2 čéą░ą║ąČąĄ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĄąĮ ą▓čĆąĄą╝ąĄąĮąĖ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ ąĖąĮč乊čĆą╝ą░čåąĖąĖ (Information Processing Time, IPT). ąŁč鹊 ą▓čĆąĄą╝čÅ, čéčĆąĄą▒čāąĄą╝ąŠąĄ ą╗ąŠą│ąĖą║ąŠą╣ ą┤ą╗čÅ ąŠčåąĖčäčĆąŠą▓ą║ąĖ ą▓čģąŠą┤ą░ CANRX. ąØą░ ą╝ąŠą┤čāą╗ąĄ CAN ą┐čĆąŠčåąĄčüčüąŠčĆą░ Blackfin čŹč鹊 ą▓čĆąĄą╝čÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé 3 čéą░ą║čéą░ SCLK. ą¤ąŠ čŹč鹊ą╣ ą┐čĆąĖčćąĖąĮąĄ ąĮą░ą║ą╗ą░ą┤čŗą▓ą░čÄčéčüčÅ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąĮą░ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ TSEG2, ąĄčüą╗ąĖ čā ą┐čĆąĄčüą║ą░ą╗ąĄčĆą░ čéą░ą║č鹊ą▓ BRP ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄąĮčīčłąĄ 2. ąĢčüą╗ąĖ BRP čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 0, ą┐ąŠą╗ąĄ TSEG2 ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ą▒ąŠą╗čīčłąĄ ąĖą╗ąĖ čĆą░ą▓ąĮąŠ 2. ąĢčüą╗ąĖ ą┐čĆąĄčüą║ą░ą╗ąĄčĆ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ 1, č鹊 ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ą┤ą╗čÅ TSEG2 ą▒čāą┤ąĄčé 1.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ą▓čüąĄ čāąĘą╗čŗ ąĮą░ čłąĖąĮąĄ CAN ą┤ąŠą╗ąČąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ ąĮąŠą╝ąĖąĮą░ą╗čīąĮčāčÄ čüą║ąŠčĆąŠčüčéčī ą▒ąĖčé.

ąÜąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓čüąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ąĖąĮč鹥čĆą▓ą░ą╗ąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ, čéčĆąĄą▒čāąĄčéčüčÅ ą┐ąŠčüą╗ąĄą┤ąĮąĄąĄ čüąŠąŠą▒čĆą░ąČąĄąĮąĖąĄ ąŠ č鹊ą╝, ą║ą░ą║ ą▓čŗą┐ąŠą╗ąĮčÅčéčī ą▓čŗą▒ąŠčĆą║čā ąĘąĮą░č湥ąĮąĖčÅ ą▒ąĖčéą░ (ąŠčåąĖčäčĆąŠą▓ą║ą░, sampling). ą¤ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ čüąŠčüč鹊ąĖčé ą▓ č鹊ą╝, čćč鹊 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ą┤ąĄą╗ą░ąĄčé ą▓čŗą▒ąŠčĆą║čā ą▒ąĖčéą░ CAN ąŠą┤ąĖąĮ čĆą░ąĘ ą▓ č鹊čćą║ąĄ ą▓čŗą▒ąŠčĆą║ąĖ, ąŠą┐ąĖčüą░ąĮąĮąŠą╣ čĆąĄą│ąĖčüčéčĆąŠą╝ CAN_TIMING, čćč鹊 čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▒ąĖč鹊ą╝ SAM. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ ą▒ąĖčé SAM čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┐ąĄčĆąĄą┤ąĖčüą║čĆąĄčéąĖąĘąĖčĆčāąĄčéčüčÅ čéčĆąĄčģą║čĆą░čéąĮąŠą╣ ą▓čŗą▒ąŠčĆą║ąŠą╣ čü čćą░čüč鹊č鹊ą╣ SCLK čĆąĄąĘčāą╗čīčéąĖčĆčāčÄčēąĄąĄ ąĘąĮą░č湥ąĮąĖąĄ ą│ąĄąĮąĄčĆąĖčĆčāąĄčéčüčÅ ą┐ąŠ ą┐čĆąĖąĮčåąĖą┐čā ąĮą░ąĖą▒ąŠą╗čīčłąĄą│ąŠ ą║ąŠą╗ąĖč湥čüčéą▓ą░ ą▓čŗą▒ąŠčĆąŠą║ ą▓ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝ čāčĆąŠą▓ąĮąĄ (ąĄčüą╗ąĖ ąĖąĘ čŹčéąĖčģ čéčĆąĄčģ ą▓čŗą▒ąŠčĆąŠą║ ą▒čŗą╗ąŠ ą▒ąŠą╗čīčłąĄ ąĄą┤ąĖąĮąĖčå, č鹊 čüčćąĖčéą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄ ą▒ąĖčéą░ ąĘą░ ąĄą┤ąĖąĮąĖčåčā, ąĄčüą╗ąĖ ą▒ąŠą╗čīčłąĄ ąĮčāą╗ąĄą╣, č鹊 ąĮąŠą╗čī). ąÆčüąĄą│ą┤ą░ ąŠčüčéą░ą▓ą╗čÅą╣č鹥 ą▒ąĖčé SAM čüą▒čĆąŠčłąĄąĮąĮčŗą╝, ąĄčüą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ BRP ą╝ąĄąĮčīčłąĄ 4.

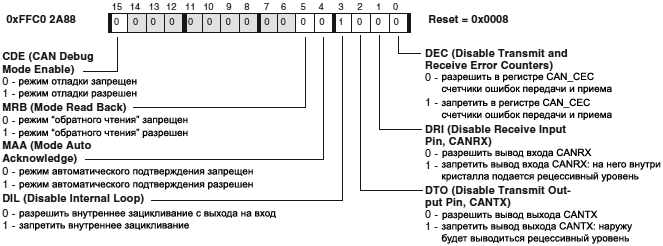

ąÆąŠ ą▓čĆąĄą╝čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ąĮąĄ ą┐čŗčéą░ą╣č鹥čüčī ą╝ąĄąĮčÅčéčī čĆąĄą│ąĖčüčéčĆčŗ CAN_CLOCK ąĖą╗ąĖ CAN_TIMING. ąöą╗čÅ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą▓čüąĄą│ą┤ą░ čüąĮą░čćą░ą╗ą░ ą▓čģąŠą┤ąĖč鹥 ą▓ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ. ąŚą░ą┐ąĖčüčī ą▓ čŹčéąĖ čĆąĄą│ąĖčüčéčĆčŗ ąĮąĄ ą┤ą░čüčé čŹčäč乥ą║čéą░, ąĄčüą╗ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ąĮą░čģąŠą┤ąĖčéčüčÅ ąĮąĄ ą▓ čĆąĄąČąĖą╝ąĄ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖą╗ąĖ ąŠčéą╗ą░ą┤ą║ąĖ. ąĢčüą╗ąĖ ą┐čĆąŠčåąĄčüčüąŠčĆ ąĮąĄ ą▓čŗčģąŠą┤ąĖą╗ ąĖąĘ čüąŠčüč鹊čÅąĮąĖčÅ čüą▒čĆąŠčüą░ ąĖą╗ąĖ ą│ąĖą▒ąĄčĆąĮą░čåąĖąĖ, č鹊 ą▓ą▓ąĄą┤ąĖč鹥 ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ą▓ čĆąĄąČąĖą╝ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ CCR ą▓ ą│ą╗ą░ą▓ąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ (master control, CAN_CONTROL) ąĖ ąŠą┐čĆą░čłąĖą▓ą░ą╣č鹥 čĆąĄą│ąĖčüčéčĆ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čüčéą░čéčāčüą░ CAN (CAN_STATUS) ą▓ ąŠąČąĖą┤ą░ąĮąĖąĖ čāčüčéą░ąĮąŠą▓ą║ąĖ ą▒ąĖčéą░ CCA.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐ąŠą╗ąĄ TSEG1 ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąŠ ą▓ 0, č鹊 ą╝ąŠą┤čāą╗čī CAN ąĮąĄ ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ.

ąÆąŠ ą▓čĆąĄą╝čÅ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ą╝ąŠą┤čāą╗čī ąĮąĄ ą░ą║čéąĖą▓ąĄąĮ ąĮą░ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN. ąÆčŗą▓ąŠą┤ ą▓čŗčģąŠą┤ą░ CANTX ąŠčüčéą░ąĄčéčüčÅ ą▓ čĆąĄčåąĄčüčüąĖą▓ąĮąŠą╝ čüąŠčüč鹊čÅąĮąĖąĖ ąĖ ą╝ąŠą┤čāą╗čī ąĮąĄ ą┐ąĄčĆąĄą┤ą░ąĄčé ąĖ ąĮąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖčÅ ąĖą╗ąĖ čäčĆąĄą╣ą╝čŗ ąŠčłąĖą▒ą║ąĖ (error frames). ą¤ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą▓čŗčģąŠą┤ ąĖąĘ čĆąĄąČąĖą╝ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ, ą▓čüąĄ ą▓ąĮčāčéčĆąĄąĮąĮąĖąĄ čĆąĄą│ąĖčüčéčĆčŗ čÅą┤čĆą░ CAN ąĖ čüč湥čéčćąĖą║ąĖ ąŠčłąĖą▒ąŠą║ CAN čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▓ čüą▓ąŠąĄ ą┐ąĄčĆą▓ąŠąĮą░čćą░ą╗čīąĮąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü (software reset) ąĮąĄ ą╝ąĄąĮčÅąĄčé ąĘąĮą░č湥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ CAN_CLOCK ąĖ CAN_TIMING. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐čĆąŠąĖčüčģąŠą┤čÅčēą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ č湥čĆąĄąĘ čłąĖąĮčā CAN ąĮąĄ ą▒čāą┤ąĄčé ą┐ąŠą▓čĆąĄąČą┤ąĄąĮą░ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄą╝ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą▓čĆąĄą╝ąĄąĮąĖ ą▒ąĖčéą░ ąĖą╗ąĖ ąĖąĮąĖčåąĖą░čåąĖąĄą╣ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ (SRS=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_CONTROL).

[ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćą░]

ąĀąĖčü. 17-8 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čäčāąĮą║čåąĖąŠąĮąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ CAN. ą»čēąĖą║ąĖ 24-31 ąĮą░ąĘąĮą░č湥ąĮčŗ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╝ąĖ. ą»čēąĖą║ąĖ 8-23 ą╝ąŠąČąĮąŠ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čÄčēąĖąĄ ąĘą░ą┐ąĖčüčīčÄ 0 ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ CAN_MDx. ą¤ąŠčüą╗ąĄ ąĘą░ą┐ąĖčüąĖ ą┤ą░ąĮąĮčŗčģ ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ ą▓ ąŠą▒ą╗ą░čüčéčī čÅčēąĖą║ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤ąĄčé čĆą░ąĘčĆąĄčłąĄąĮ čÅčēąĖą║ n (MCn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MCx) ąĖ ą▓ą┐ąŠčüą╗ąĄą┤čüčéą▓ąĖąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit request, TRSn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TRSx).

ąÜąŠą│ą┤ą░ ą┐ąĄčĆąĄą┤ą░čćą░ ąĘą░ą▓ąĄčĆčłąĄąĮą░, ąŠčćąĖčēą░čÄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĖ čĆąĄą│ąĖčüčéčĆąĄ čüą▒čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit request reset, TRRn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TRRx). ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čŗą╗ą░ čāčüą┐ąĄčłąĮą░, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ (transmit acknowledge, TAn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TAx). ąĢčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čŗą╗ą░ ąŠą▒ąŠčĆą▓ą░ąĮą░ ąĖąĘ-ąĘą░ ą┐čĆąŠąĖą│čĆčŗčłą░ ą░čĆą▒ąĖčéčĆą░ąČą░ ą┐ąŠ ą┐čĆąĖąŠčĆąĖč鹥čéčā ąĖą╗ąĖ ąŠčłąĖą▒ą║ąĖ CAN, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąŠą▒čĆčŗą▓ą░ (abort acknowledge, AAn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_AAx). ąŚą░ą┐čĆąŠčłąĄąĮąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠą▒ąŠčĆą▓ą░ąĮą░ ą▓čĆčāčćąĮčāčÄ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ TRRn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TRRx.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ą╝ąŠąČąĮąŠ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ą▒ąĖčé CAN_TRSx, ąĖ čŹčéąĖ ą▒ąĖčéčŗ čüą▒čĆą░čüčŗą▓ą░čÄčéčüčÅ ą╗ąĖą▒ąŠ ą┐ąŠčüą╗ąĄ čāčüą┐ąĄčłąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą╗ąĖą▒ąŠ ą┐ąŠčüą╗ąĄ ąŠą▒ąŠčĆą▓ą░ąĮąĮąŠą╣. ąæąĖčéčŗ TRSn čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą░ą┐ą┐ą░čĆą░čéčāčĆąŠą╣ CAN, ą║ąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čĆąĄąČąĖą╝ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ (auto-transmit mode) čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░, ą║ąŠą│ą┤ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐čĆąŠąĖą│čĆą░ą╗ąŠ ą░čĆą▒ąĖčéčĆą░ąČ ąĖ ą▒ąĖčé ąŠą┤ąĖąĮąŠčćąĮąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ (single-shot bit, OPSSn=0 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_OPSSx), ąĖą╗ąĖ ą▓ čüąŠą▒čŗčéąĖąĖ RTR (remote frame request). ą¤ąŠčüą╗ąĄą┤ąĮąĄąĄ ą▓ąŠąĘą╝ąŠąČąĮąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čÅčēąĖą║ąŠą▓ ą┐čĆąĖąĄą╝ą░/ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĄčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ remote frame (RFHn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RFHx).

ąĪą┐ąĄčåąĖą░ą╗čīąĮąŠąĄ ą▓ąĮąĖą╝ą░ąĮąĖąĄ ą┤ąŠą╗ąČąĮąŠ čāą┤ąĄą╗čÅčéčīčüčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĄ ąŠą▒ą╗ą░čüčéąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ čÅčēąĖą║ą░, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TRSn. ąöąŠčüčéčāą┐ ąĮą░ ąĘą░ą┐ąĖčüčī ą║ čÅčēąĖą║čā čü čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ TRSn čĆą░ąĘčĆąĄčłąĄąĮ, ąĮąŠ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą▓ čéą░ą║ąŠą╝ čÅčēąĖą║ąĄ ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ ą┤ą░ąĮąĮčŗą╝ ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ąÆą║ą╗čÄč湥ąĮąĖąĄ ąĖ ąŠčéą║ą╗čÄč湥ąĮąĖąĄ čÅčēąĖą║ąŠą▓ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ą╗ąĖčÅąĮąĖąĄ ąĮą░ ąĘą░ą┐čĆąŠčüčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąŻčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ TRSn, čüą▓čÅąĘą░ąĮąĮąŠą│ąŠ čü ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗą╝ čÅčēąĖą║ąŠą╝, ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąŠčłąĖą▒ąŠčćąĮąŠą╝čā ą┐ąŠą▓ąĄą┤ąĄąĮąĖčÄ. ąóąŠčćąĮąŠ čéą░ą║ ąČąĄ ąĘą░ą┐čĆąĄčé čÅčēąĖą║ą░ ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣ ą▒čāą┤ąĄčé čüą▒čĆąŠčłąĄąĮ ą▒ąĖčé TRSn, ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ čĆąĄąĘčāą╗čīčéą░čéą░ą╝.

Retransmission (ą┐ąŠą▓č鹊čĆąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░). ą×ą▒čŗčćąĮąŠ č鹥ą║čāčēąĖą╣ ąŠą▒čŖąĄą║čé čüąŠąŠą▒čēąĄąĮąĖčÅ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čüąĮąŠą▓ą░ ą┐ąŠčüą╗ąĄ ą┐čĆąŠąĖą│čĆčŗčłą░ ą░čĆą▒ąĖčéčĆą░ąČą░, ąĖą╗ąĖ ą┐ąŠčüą╗ąĄ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĖčÅ ąŠčłąĖą▒ąŠčćąĮąŠą│ąŠ čäčĆąĄą╣ą╝ą░ ąĮą░ čłąĖąĮąĄ CAN. ąĢčüą╗ąĖ ąŠąČąĖą┤ą░ąĄčé čüą▓ąŠąĄą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▒ąŠą╗čīčłąĄ ąŠą┤ąĮąŠą│ąŠ ąŠą▒čŖąĄą║čéą░ čüąŠąŠą▒čēąĄąĮąĖčÅ, č鹊 ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ č鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ, čÅčēąĖą║ ą║ąŠč鹊čĆąŠą│ąŠ ąĖą╝ąĄąĄčé ą▒ąŠą╗čīčłąĖą╣ ąĮąŠą╝ąĄčĆ (čüą╝. čĆąĖčü. 17-8). ą×ą▒ąŠčĆą▓ą░ąĮąĮą░čÅ ą▓ ąĮą░čüč鹊čÅčēąĖą╣ ą╝ąŠą╝ąĄąĮčé ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ąĄčĆąĄąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą▒čāą┤čāčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮčŗ ą╗čÄą▒čŗąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ čü ą▒ąŠą╗ąĄąĄ ą▓čŗčüąŠą║ąĖą╝ ą┐čĆąĖąŠčĆąĖč鹥č鹊ą╝.

ąĀąĖčü. 17-8. ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ ą┐ąĄčĆąĄą┤ą░čćąĖ CAN.

ąĪąŠąŠą▒čēąĄąĮąĖąĄ, ą║ąŠč鹊čĆąŠąĄ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐ąŠą┤ą│ąŠč鹊ą▓ą║ąĖ, ąĮąĄ ąĘą░ą╝ąĄąĮčÅąĄčéčüčÅ ą┤čĆčāą│ąĖą╝ čüąŠąŠą▒čēąĄąĮąĖąĄą╝, ą║ąŠč鹊čĆąŠąĄ ąĘą░ą┐ąĖčüą░ąĮąŠ ą▓ ą┐ąŠčćč鹊ą▓čŗą╣ čÅčēąĖą║. ą¤ąŠą┤ą│ąŠčéą░ą▓ą╗ąĖą▓ą░ąĄą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ - č鹊, ą║ąŠč鹊čĆąŠąĄ čüą║ąŠą┐ąĖčĆąŠą▓ą░ąĮąŠ ą▓ąŠ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ą▒čāč乥čĆ, ą║ąŠą│ą┤ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąĘą░ą┐čĆąŠčü ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ ą╝ąŠą┤čāą╗čÅ čÅą┤čĆą░ CAN. ąĪąŠąŠą▒čēąĄąĮąĖąĄ ą▓ ą▒čāč乥čĆąĄ ąĮąĄ ą▒čāą┤ąĄčé ąĘą░ą╝ąĄąĮąĄąĮąŠ ą┐ąŠą║ą░ ąŠąĮąŠ ąĮąĄ ą▒čāą┤ąĄčé čāčüą┐ąĄčłąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ, ą┐čĆąŠąĖą│čĆą░ąĮ ą░čĆą▒ąĖčéčĆą░ąČ ąĮą░ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN, ąĖą╗ąĖ ą┐ąŠčÅą▓ąĖčéčüčÅ čäčĆąĄą╣ą╝ ąŠčłąĖą▒ą║ąĖ ąĮą░ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN.

ą×ą┤ąĖąĮąŠčćąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ (Single Shot Transmission). ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čäčāąĮą║čåąĖčÅ ąŠą┤ąĮąŠą║čĆą░čéąĮąŠą╣ ąŠčéą┐čĆą░ą▓ą║ąĖ (OPSSn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_OPSSx), č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé TRSn ąŠčćąĖčēą░ąĄčéčüčÅ ą┐ąŠčüą╗ąĄ čāčüą┐ąĄčłąĮąŠą╣ ąŠčéą┐čĆą░ą▓ą║ąĖ čüąŠąŠą▒čēąĄąĮąĖčÅ, ąĖą╗ąĖ ąĄčüą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćą░ ą▒čŗą╗ą░ ąŠą▒ąŠčĆą▓ą░ąĮą░ ąĖąĘ-ąĘą░ ą┐čĆąŠąĖą│čĆčŗčłą░ ą░čĆą▒ąĖčéčĆą░ąČą░ ąĖą╗ąĖ ą┐ąŠčÅą▓ą╗ąĄąĮąĖčÅ čäčĆąĄą╣ą╝ą░ ąŠčłąĖą▒ą║ąĖ ąĮą░ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒ąŠą╗čīčłąĄ ąĮąĄ ą▒čāą┤ąĄčé ą┐ąŠą┐čŗč鹊ą║ čüąĮąŠą▓ą░ ą┐ąĄčĆąĄą┤ą░čéčī čŹč鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ, ąĄčüą╗ąĖ ą┐ąĄčĆą▓ą░čÅ ą┐ąŠą┐čŗčéą║ą░ ą▒čŗą╗ą░ ąĮąĄčāą┤ą░čćąĮąŠą╣, ąĖ ąŠą▒ čŹč鹊ą╝ čüąŠąŠą▒čēą░ąĄčéčüčÅ čäą╗ą░ą│ąŠą╝ ąŠčłąĖą▒ą║ąĖ ąŠą▒čĆčŗą▓ą░ (abort error, AAn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_AAx).

ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░ (Auto-Transmission). ąÆ čĆąĄąČąĖą╝ąĄ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓ čÅčēąĖą║ąĄ 11 ą╝ąŠąČąĄčé ąŠčéą┐čĆą░ą▓ą╗čÅčéčīčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░. ąŁč鹊čé čĆąĄąČąĖą╝ čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ čłąĖčĆąŠą║ąŠą▓ąĄčēą░č鹥ą╗čīąĮčŗčģ čüąŠąŠą▒čēąĄąĮąĖą╣ čüąĄčĆą┤čåąĄą▒ąĖąĄąĮąĖčÅ (broadcast heartbeats), ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗčģ ąĮą░ ą▓čüąĄ čāąĘą╗čŗ CAN. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąŠčéą┐čĆą░ą▓ą╗čÅąĄą╝čŗąĄ čéą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ čüąŠąŠą▒čēąĄąĮąĖčÅ ąŠą▒čŗčćąĮąŠ ąĖą╝ąĄčÄčé ą▓čŗčüąŠą║ąĖą╣ ą┐čĆąĖąŠčĆąĖč鹥čé.

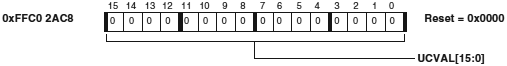

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąĄčĆąĖąŠą┤ą░ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ CAN_UCRC. ąÜąŠą│ą┤ą░ čŹč鹊čé čĆąĄąČąĖą╝ čĆą░ąĘčĆąĄčłąĄąĮ (čāčüčéą░ąĮąŠą▓ą║ąŠą╣ UCCNF[3:0]=0x3 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_UCCNF), č鹊 čüč湥čéčćąĖą║ (čĆąĄą│ąĖčüčéčĆ CAN_UCCNT) ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ CAN_UCRC. ąĪč湥čéčćąĖą║ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čü čćą░čüč鹊č鹊ą╣ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ąĖčé CAN ą┤ąŠ 0, ąĖ ąĘą░č鹥ą╝ ą┐ąĄčĆąĄąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ CAN_UCRC. ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ą░ąĄčé ąĘąĮą░č湥ąĮąĖčÅ 0, ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ čāčüčéą░ąĮą░ą▓ą╗ąĖą▓ą░ąĄčéčüčÅ ą▒ąĖčé TRS11, ąĖ ąŠčéą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ąĖąĘ čÅčēąĖą║ą░ 11.

ąöą╗čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ čÅčēąĖą║ 11 ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣, ąĖ ą┤ąŠą╗ąČąĄąĮ čüąŠą┤ąĄčƹȹ░čéčī ą┐čĆą░ą▓ąĖą╗čīąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ (ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ, ą▒ąĖčéčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąĖ ą┤ą░ąĮąĮčŗąĄ) ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čüč湥čéčćąĖą║ ą┐ąĄčĆą▓čŗą╣ čĆą░ąĘ ą┤ąŠčüčćąĖčéą░ąĄčé ą┤ąŠ 0, ą║ąŠą│ą┤ą░ čŹč鹊čé čĆąĄąČąĖą╝ čĆą░ąĘčĆąĄčłąĄąĮ.

[ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé ą┐čĆąĖąĄą╝]

ąÉą┐ą┐ą░čĆą░čéčāčĆą░ CAN ą░ą▓č鹊ąĮąŠą╝ąĮąŠ ą┐čĆąĖąĮąĖą╝ą░ąĄčé čüąŠąŠą▒čēąĄąĮąĖčÅ, ąŠčéą▒čĆą░čüčŗą▓ą░čÅ ą┐čĆąĖ čŹč鹊ą╝ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝čŗąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ. ąÜą░ą║ č鹊ą╗čīą║ąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ čāčüą┐ąĄčłąĮąŠ ą┐čĆąĖąĮčÅč鹊, ą╗ąŠą│ąĖą║ą░ ą┐čĆąĖąĄą╝ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ ąŠą┐čĆą░čłąĖą▓ą░ąĄčé ą▓čüąĄ čĆą░ąĘčĆąĄčłąĄąĮąĮčŗąĄ ąĮą░ ą┐čĆąĖąĄą╝ čÅčēąĖą║ąĖ ąŠčé čÅčēąĖą║ą░ 23 ą▓ąĮąĖąĘ, ą┤ąŠ čÅčēąĖą║ą░ 0, ąĖ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčé, ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé ą╗ąĖ čüąŠąŠą▒čēąĄąĮąĖąĄ ąĖąĮč鹥čĆąĄčü ą┤ą╗čÅ ą╗ąŠą║ą░ą╗čīąĮąŠą│ąŠ čāąĘą╗ą░, ąĖą╗ąĖ ąĮąĄčé.

ąÜą░ąČą┤čŗą╣ ą▓čģąŠą┤čÅčēąĖą╣ čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčéčüčÅ čüąŠ ą▓čüąĄą╝ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ą╝ąĖ, čüąŠčģčĆą░ąĮąĄąĮąĮčŗą╝ąĖ ą▓ ą░ą║čéąĖą▓ąĮčŗčģ čÅčēąĖą║ą░čģ ą┐čĆąĖąĄą╝ą░ (MDn=1 ąĖ MCn=1), ąĖ ą┤ą╗čÅ ą▓čüąĄčģ ą░ą║čéąĖą▓ąĮčŗčģ ą┐ąĄčĆąĄą┤ą░čÄčēąĖčģ čÅčēąĖą║ą░čģ, čā ą║ąŠč鹊čĆčŗčģ čĆą░ąĘčĆąĄčłąĄąĮą░ čäčāąĮą║čåąĖčÅ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ remote frame (RFHn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RFHx).

ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ą╝ąĄčüč鹥 čü ą▒ąĖč鹊ą╝ čĆą░čüčłąĖčĆąĄąĮąĖčÅ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ (identifier extension, IDE) ąĖ ą▒ąĖč鹊ą╝ ąĘą░ą┐čĆąŠčüą░ remote transmission (RTR) čüčĆą░ą▓ąĮąĖą▓ą░čÄčéčüčÅ čü ąĮą░čüčéčĆąŠą╣ą║ą░ą╝ąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą║ą░ąČą┤ąŠą│ąŠ čÅčēąĖą║ą░. ąĢčüą╗ąĖ ą▒ąĖčé AME ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ č鹊ą╗čīą║ąŠ ą┐ąŠ ą▒ąĖčéą░ą╝ IDE, RTR ąĖ ą▓čüąĄą╝ ą▒ąĖčéą░ą╝ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓. ą×ą┤ąĮą░ą║ąŠ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé AME, č鹊 čĆąĄą│ąĖčüčéčĆčŗ ą╝ą░čüą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ (acceptance mask) ąŠą┐čĆąĄą┤ąĄą╗čÅčÄčé, ą║ą░ą║ąŠą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ąĖ ą▒ąĖčéčŗ IDE ąĖ RTR ąĮčāąČą┤ą░čÄčéčüčÅ ą▓ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ. ąØą░ą║ą╗ą░ą┤čŗą▓ą░ąĄą╝ą░čÅ ą╗ąŠą│ąĖą║ą░: Received Message XNOR CAN_IDx ąĖą╗ąĖ AME AND CAN_AMx. ąĢą┤ąĖąĮąĖčåą░ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ą▒ąĖč鹊ą▓ąŠą╣ ą┐ąŠąĘąĖčåąĖąĖ čĆąĄą│ąĖčüčéčĆąŠą▓ ą╝ą░čüą║ąĖ CAN_AMxx ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 čŹč鹊čé ą▒ąĖčé ąĮąĄ ąĮčāąČą┤ą░ąĄčéčüčÅ ą▓ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ, ą║ąŠą│ą┤ą░ AME=1. ąóą░ą║ąĖą╝ čüą┐ąŠčüąŠą▒ąŠą╝ čÅčēąĖą║ ą┐ąŠą╗čāčćą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┐čĆąĖąĮąĖą╝ą░čéčī ą│čĆčāą┐ą┐čŗ čüąŠąŠą▒čēąĄąĮąĖą╣ ą┐ąŠ ąĖčģ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ą╝.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ą▓ ą║ąŠąĮč鹥ą║čüč鹥 čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠ ID čüąŠąŠą▒čēąĄąĮąĖčÅ ąĄčüčéčī ąĖčüą║ą╗čÄč湥ąĮąĖąĄ, ą┐ąŠč湥ą╝čā-č鹊 ąĮąĄ ąŠą┐ąĖčüą░ąĮąĮąŠąĄ ą▓ ą┤ą░čéą░čłąĖč鹥 ąĮą░ ą░ą┐ą┐ą░čĆą░čéčāčĆčā ADSP-BF50x. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ ą▒ąĖčéčŗ ą╝ą░čüą║ąĖ, čüąŠąŠą▒čēąĄąĮąĖąĄ čü ąĮčāą╗ąĄą▓čŗą╝ ID ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅč鹊 ą▓čüąĄą│ą┤ą░.

ąóą░ą▒ą╗ąĖčåą░ 17-1. ą»čēąĖą║ąĖ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗąĄ ą┤ą╗čÅ ą▓čģąŠą┤ąĮąŠą╣ čäąĖą╗čīčéčĆą░čåąĖąĖ čüąŠąŠą▒čēąĄąĮąĖą╣ ą┐ąŠ ą╝ą░čüą║ąĄ (Acceptance Mask Filtering).

| MCn |

MDn |

RFHn |

ą»čēąĖą║ n |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖą╣ |

| 0 |

x |

x |

ąśą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ |

ą»čēąĖą║ n ąĘą░ą┐čĆąĄčēąĄąĮ |

| 1 |

0 |

0 |

ąśą│ąĮąŠčĆąĖčĆčāąĄčéčüčÅ |

ą»čēąĖą║ n čĆą░ąĘčĆąĄčłąĄąĮ

ą»čēąĖą║ n čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

ą×ą▒čĆą░ą▒ąŠčéą║ą░ čäčĆąĄą╣ą╝ą░ remote ąĘą░ą┐čĆąĄčēąĄąĮą░ |

| 1 |

0 |

1 |

ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

ą»čēąĖą║ n čĆą░ąĘčĆąĄčłąĄąĮ

ą»čēąĖą║ n čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ

ą×ą▒čĆą░ą▒ąŠčéą║ą░ čäčĆąĄą╣ą╝ą░ remote čĆą░ąĘčĆąĄčłąĄąĮą░ |

| 1 |

1 |

x |

ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ |

ą»čēąĖą║ n čĆą░ąĘčĆąĄčłąĄąĮ

ą»čēąĖą║ n čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ |

ąĢčüą╗ąĖ čäąĖą╗čīčéčĆ ą┐čĆąĖąĄą╝ą░ ąĮą░ą╣ą┤ąĄčé ą┐ąŠą┤čģąŠą┤čÅčēąĖą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ, č鹊 čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ąĄą│ąŠ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čÅčēąĖą║ąĄ. ą¤čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮąŠ č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆą░ąĘ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą┤ą╗čÅ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┐čĆąĖąĄą╝ąĮčŗčģ čÅčēąĖą║ąŠą▓ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą▒čāą┤ąĄčé ą┐ąŠą┤čģąŠą┤čÅčēąĖą╝. ąĢčüą╗ąĖ č鹥ą║čāčēąĖą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĮąĄ ą┐ąŠą┤čģąŠą┤ąĖčé ąĮąĖ ą┤ą╗čÅ ą║ą░ą║ąŠą│ąŠ čÅčēąĖą║ą░, č鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮąŠ.

ąĀąĖčü. 17-9 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ąĄčĆąĄą▓ąŠ ą┐čĆąĖąĮčÅčéąĖčÅ čĆąĄčłąĄąĮąĖčÅ ą╗ąŠą│ąĖą║ąĖ ą┐čĆąĖąĄą╝ą░, ą║ąŠą│ą┤ą░ ąĖą┤ąĄčé ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąŠčéą┤ąĄą╗čīąĮčŗčģ čÅčēąĖą║ąŠą▓.

ąĀąĖčü. 17-9. ąÉą╗ą│ąŠčĆąĖčéą╝ čĆą░ą▒ąŠčéčŗ ą┐čĆąĖąĄą╝ą░ CAN.

ąĢčüą╗ąĖ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊 ą┤ą╗čÅ čÅčēąĖą║ą░, ąĖ čŹč鹊čé čÅčēąĖą║ ą▓čüąĄ ąĄčēąĄ čüąŠą┤ąĄčƹȹĖčé ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ (RMPn=1), č鹊 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī čĆąĄčłą░ąĄčé, ą┤ąŠą╗ąČąĮąŠ ą╗ąĖ ą▒čŗčéčī čüčéą░čĆąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮąŠ ąĮąŠą▓čŗą╝, ąĖą╗ąĖ ąĮąĄčé. ąĢčüą╗ąĖ OPSSn=0, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ą┐ąŠč鹥čĆąĖ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ (receive message lost, ą▒ąĖčé RMLn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RMLx), ąĖ čüčéą░čĆąŠąĄ čüąŠčģčĆą░ąĮąĄąĮąĮąŠąĄ ą▓ čÅčēąĖą║ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĘą░ą┐ąĖčüą░ąĮąŠ. ąŁč鹊 ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąŠč鹥čĆąĖ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN (RMLIS=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_GIS). ąĢčüą╗ąĖ OPSSn=1, č鹊 ą▒čāą┤čāčé ą┐čĆąŠą▓ąĄčĆąĄąĮčŗ čüą╗ąĄą┤čāčÄčēąĖąĄ čÅčēąĖą║ąĖ ąĮą░ ą┐čĆąĄą┤ą╝ąĄčé čüąŠą▓ą┐ą░ą┤ąĄąĮąĖčÅ ą┐ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā. ąĢčüą╗ąĖ čéą░ą║ąŠąĄ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ ąĮąĄ ą▒čŗą╗ąŠ ąĮą░ą╣ą┤ąĄąĮąŠ, č鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé ąŠčéą▒čĆąŠčłąĄąĮąŠ, ąĖ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐ąĄčĆąĄčģąŠą┤ ą║ ą┐čĆąŠą▓ąĄčĆą║ąĄ čüą╗ąĄą┤čāčÄčēąĄą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ.

ąÆą░ąČąĮąŠąĄ ąĘą░ą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ čÅčēąĖą║ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐čĆąĄčēąĄąĮ, č鹊 ą┐čĆąĖčłąĄą┤čłąĄąĄ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┤ą╗čÅ čŹč鹊ą│ąŠ čÅčēąĖą║ą░ ą▒čāą┤ąĄčé ą┐ąŠč鹥čĆčÅąĮąŠ, ą┤ą░ąČąĄ ąĄčüą╗ąĖ ą▓č鹊čĆąŠą╣ čÅčēąĖą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ č鹊ą│ąŠ ąČąĄ čüą░ą╝ąŠą│ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░.

ążąĖą╗čīčéčĆ ą┐ąŠ ą┤ą░ąĮąĮčŗą╝ (Data Acceptance Filter). ąĢčüą╗ąĖ čĆą░ąĘčĆąĄčłąĄąĮ čĆąĄąČąĖą╝ DeviceNet (DNM=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_CONTROL), ąĖ čÅčēąĖą║ ąĮą░čüčéčĆąŠąĄąĮ ąĮą░ čäąĖą╗čīčéčĆą░čåąĖčÄ ą┐ąŠ ą┐ąŠą╗čÄ ą┤ą░ąĮąĮčŗčģ, čäąĖą╗čīčéčĆą░čåąĖčÅ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąŠ ą┐ąŠą╗čÄ čüčéą░ąĮą┤ą░čĆčéąĮąŠą│ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ ID ąĖ ą┐ąŠ ą┐ąŠą╗čÄ ą┤ą░ąĮąĮčŗčģ čüąŠąŠą▒čēąĄąĮąĖčÅ. ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠ ą┐ąŠą╗čÄ ą┤ą░ąĮąĮčŗčģ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮą░ ą╗ąĖą▒ąŠ č鹊ą╗čīą║ąŠ ą┐ąŠ ą┐ąĄčĆą▓ąŠą╝čā ą▒ą░ą╣čéčā, ą╗ąĖą▒ąŠ ą┐ąŠ ą┐ąĄčĆą▓čŗą╝ ą┤ą▓čāą╝ ą▒ą░ą╣čéą░ą╝, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 17-2.

ąóą░ą▒ą╗ąĖčåą░ 17-2. ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠ ą┐ąŠą╗čÄ ą┤ą░ąĮąĮčŗčģ čüąŠąŠą▒čēąĄąĮąĖčÅ (Data Field Filtering).

FDF

ążąĖą╗čīčéčĆ ą┐ąŠ ą┐ąŠą╗čÄ ą┤ą░ąĮąĮčŗčģ |

FMD

ą¤ąŠą╗ąĮą░čÅ ą╝ą░čüą║ą░ ą┐ąŠ ą┐ąŠą╗čÄ ą┤ą░ąĮąĮčŗčģ |

ą×ą┐ąĖčüą░ąĮąĖąĄ |

| 0 |

0 |

ążąĖą╗čīčéčĆą░čåąĖčÅ ą┐ąŠ ą┐ąŠą╗čÄ ą┤ą░ąĮąĮčŗčģ ąĮąĄ čĆą░ąĘčĆąĄčłąĄąĮą░. |

| 0 |

1 |

ąØąĄ čĆą░ąĘčĆąĄčłąĄąĮąŠ. FMD ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī 0, ąĄčüą╗ąĖ FDF=0. |

| 1 |

0 |

ążąĖą╗čīčéčĆ č鹊ą╗čīą║ąŠ ą┐ąŠ ą┐ąĄčĆą▓ąŠą╝čā ą▒ą░ą╣čéčā ą┤ą░ąĮąĮčŗčģ. |

| 1 |

1 |

ążąĖą╗čīčéčĆ ą┐ąŠ ą┤ą▓čāą╝ ą▒ą░ą╣čéą░ą╝ ą┤ą░ąĮąĮčŗčģ. |

ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé FDF ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ CAN_AMxxH, č鹊 čĆąĄą│ąĖčüčéčĆ CAN_AMxxL čüąŠą┤ąĄčƹȹĖčé ą╝ą░čüą║čā čäąĖą╗čīčéčĆą░čåąĖąĖ ą┐ąŠ ą┤ą░ąĮąĮčŗą╝ (data field mask, DFM[15:0]). ąĢčüą╗ąĖ ą▒ąĖčé FDF ąŠčćąĖčēąĄąĮ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╝ čĆąĄą│ąĖčüčéčĆąĄ CAN_AMxxH, č鹊 čĆąĄą│ąĖčüčéčĆ CAN_AMxxL čüąŠą┤ąĄčƹȹĖčé ą╝ą░čüą║čā ą┤ą╗čÅ čĆą░čüčłąĖčĆąĄąĮąĮąŠą│ąŠ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░ (extended identifier mask, EXTID_HI[15:0]).

ą×ą▒čĆą░ą▒ąŠčéą║ą░ RTR (Remote Frame Handling). ąÉą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ čäčĆąĄą╣ą╝ąŠą▓ remote ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮą░/ąĘą░ą┐čĆąĄčēąĄąĮą░ ą┐čāč鹥ą╝ čāčüčéą░ąĮąŠą▓ą║ąĖ/ąŠčćąĖčüčéą║ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ remote frame (CAN_RFHx) ą┐ąĄčĆąĄą┤ą░čÄčēąĄą│ąŠ čÅčēąĖą║ą░.

ążčĆąĄą╣ą╝čŗ remote čŹč鹊 čäčĆąĄą╣ą╝čŗ ą┤ą░ąĮąĮčŗčģ, čā ą║ąŠč鹊čĆčŗčģ ąĮąĄčé ą┐ąŠą╗čÅ ą┤ą░ąĮąĮčŗčģ, ąĖ čā ą║ąŠč鹊čĆčŗčģ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé RTR. ąÜąŠą┤ ą┤ą╗ąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ (data length code, DLC) ąŠčéą▓ąĄčćą░čÄčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ ą░ąĮąĮčāą╗ąĖčĆčāąĄčéčüčÅ ą║ąŠą┤ąŠą╝ DLC ąĘą░ą┐čĆą░čłąĖą▓ą░čÄčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░ remote. ąÜąŠą┤ DLC ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ ąŠčé 0 ą┤ąŠ 15, ąĮąŠ ąĘąĮą░č湥ąĮąĖčÅ DLC ą▒ąŠą╗čīčłąĄ 8 čüčćąĖčéą░čÄčéčüčÅ ą║ą░ą║ ąĘąĮą░č湥ąĮąĖąĄ 8. ążčĆąĄą╣ą╝ remote čüąŠą┤ąĄčƹȹĖčé:

ŌĆó ąæąĖčéčŗ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆą░.

ŌĆó ąŻą┐čĆą░ą▓ą╗čÅčÄčēąĄąĄ ą┐ąŠą╗ąĄ DLC.

ŌĆó ąæąĖčé ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā čü ą┤ą░ą╗čīąĮąĄą│ąŠ čāąĘą╗ą░ (remote transmission request, RTR).

ążčĆąĄą╣ą╝čŗ remote ą╝ąŠą│čāčé ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░čéčī č鹊ą╗čīą║ąŠ ą║ąŠąĮčäąĖą│čāčĆąĖčĆčāąĄą╝čŗąĄ čÅčēąĖą║ąĖ 8ŌĆō23, ąĮąŠ ą▓čüąĄ čÅčēąĖą║ąĖ ą╝ąŠą│čāčé ą┐čĆąĖąĮąĖą╝ą░čéčī ąĖ ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčī ąĘą░ą┐čĆąŠčüčŗ remote frame. ąÜąŠą│ą┤ą░ ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮą░ ąĮą░čüčéčĆąŠą╣ą║ą░ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ remote frame, čĆąĄą│ąĖčüčéčĆ CAN_OPSSx ąĮąĄ ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą▓ą╗ąĖčÅąĮąĖčÅ. ąÆčüąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čÅčēąĖą║ą░ ą▓čüąĄą│ą┤ą░ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓čģąŠą┤čÅčēąĖą╝ čüąŠąŠą▒čēąĄąĮąĖąĄą╝.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ąĄčüą╗ąĖ ą┐čĆąĖąĮčÅčé čäčĆąĄą╣ą╝ remote, č鹊 DLC čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čÅčēąĖą║ą░ ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┐čĆąĖąĮčÅčéčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝.

ą£ąŠąČąĄčé ą▒čŗčéčī ąŠčłąĖą▒ąŠčćąĮąŠąĄ ą┐ąŠą▓ąĄą┤ąĄąĮąĖąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░, ą║ąŠą│ą┤ą░ ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ ą▒ąĖčé ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čäčĆąĄą╣ą╝ą░ remote (RFHn), ąĖ ą▓ ąĮą░čüč鹊čÅčēąĄąĄ ą▓čĆąĄą╝čÅ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čÅčēąĖą║. ąĪą╝. ą┤ą░ą╗ąĄąĄ čĆą░ąĘą┤ąĄą╗ "ąÆčĆąĄą╝ąĄąĮąĮčŗą╣ ąĘą░ą┐čĆąĄčé čÅčēąĖą║ąŠą▓" ą┤ą╗čÅ ą▒ąĄąĘąŠą┐ą░čüąĮąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čÅčēąĖą║ą░.

ąĪč鹊čĆąŠąČąĄą▓ąŠą╣ čĆąĄąČąĖą╝ (Watchdog Mode). ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą│ą░čĆą░ąĮčéąĖąĖ, čćč鹊 čüąŠąŠą▒čēąĄąĮąĖčÅ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ą┐ąĄčĆąĖąŠą┤ąĖč湥čüą║ąĖ. ąŁč鹊 čćą░čüč鹊 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, čćč鹊ą▒čŗ ąŠčéčüą╗ąĄąČąĖą▓ą░čéčī, čćč鹊 ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗą╣ čāąĘąĄą╗ ą▓ čüąĄčéąĖ čĆą░ą▒ąŠčéą░ąĄčé ą┐čĆą░ą▓ąĖą╗čīąĮąŠ, ąĖ ąĄčüą╗ąĖ čŹč鹊 ąĮąĄ čéą░ą║, č鹊 ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░čéčī čŹč鹊 ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ ąŠą▒čĆą░ą▒ąŠčéą░čéčī čéą░ą║ąŠą╣ čüą╗čāčćą░ą╣ ąŠčéą║ą░ąĘą░.

ąĪąŠą│ą╗ą░čüąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÄ čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ ą▓ čüč鹊čĆąŠąČąĄą▓ąŠą╣ čĆąĄąČąĖą╝ (čāčüčéą░ąĮąŠą▓ą║ą░ UCCNF[3:0]=0x2 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_UCCNF), čüč湥čéčćąĖą║ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_UCCNT ąĘą░ą│čĆčāąČą░ąĄčéčüčÅ ąĘą░čĆą░ąĮąĄąĄ ąĘą░ą┤ą░ąĮąĮąŠą╣ ą▓ąĄą╗ąĖčćąĖąĮąŠą╣, čüąŠą┤ąĄčƹȹ░čēąĄą╣čüčÅ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĖ/ąĘą░čģą▓ą░čéą░ čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ CAN (universal counter reload/capture, CAN_UCRC). ąŚą░č鹥ą╝ čŹč鹊čé čüč湥čéčćąĖą║ ą┤ąĄą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ čü čćą░čüč鹊č鹊ą╣ ą▒ąĖčé CAN. ąĢčüą╗ąĖ ą▒ąĖčéčŗ UCCT ąĖ UCRC ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_UCCNF čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ, ąĖ ą▒čāą┤ąĄčé ą┐čĆąĖąĮčÅč鹊 čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓ čÅčēąĖą║ 4 ą┤ąŠ č鹊ą│ąŠ, ą║ą░ą║ čüč湥čéčćąĖą║ ą┤ąŠčüčćąĖčéą░ąĄčé ą▓ąĮąĖąĘ ą┤ąŠ 0, čüč湥čéčćąĖą║ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘąĖčéčüčÅ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ čĆąĄą│ąĖčüčéčĆą░ CAN_UCRC ąĖ ą┐čĆąŠą┤ąŠą╗ąČąĖčé čüč湥čé ą▓ąĮąĖąĘ. ąĢčüą╗ąĖ ąČąĄ čüč湥čéčćąĖą║ ą┤ąŠčüčćąĖčéą░ą╗ ą┤ąŠ 0 ą▒ąĄąĘ ą┐čĆąĖąĄą╝ą░ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ čÅčēąĖą║ 4, č鹊 čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé UCEIS ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN (CAN_GIS), ąĖ čüč湥čéčćąĖą║ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąĖ ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĘą░ą│čĆčāąČąĄąĮ ąĘąĮą░č湥ąĮąĖąĄą╝ ąĖąĘ čĆąĄą│ąĖčüčéčĆą░ CAN_UCRC. ąĢčüą╗ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ąĮčāąČąĮą░ ą│ąĄąĮąĄčĆą░čåąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé UCEIM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_GIM. ąĪ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ ą▒ąĖč鹊ą╝ ą╝ą░čüą║ąĖ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, č鹊 čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé UCEIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_GIF.

ąĪč湥čéčćąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄąĘą░ą│čĆčāąČąĄąĮ čüąŠą┤ąĄčƹȹĖą╝čŗą╝ CAN_UCRC ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ CAN_UCCNF.

ą¤ąĄčĆąĖąŠą┤ ą▓čĆąĄą╝ąĄąĮąĖ ą┤ąŠ ą▓ąŠąĘąĮąĖą║ąĮąŠą▓ąĄąĮąĖčÅ čüč鹊čĆąŠąČąĄą▓ąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čāą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ąĘąĮą░č湥ąĮąĖąĄą╝, ąĘą░ą┐ąĖčüą░ąĮąĮčŗą╝ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╝ ą▓ čĆąĄą│ąĖčüčéčĆ CAN_UCRC.

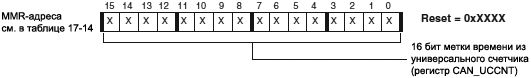

[ą£ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ]

ą¦č鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ąĖąĮą┤ąĖą║ą░čåąĖčÄ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĖąĄą╝ą░ ąĖą╗ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ, ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāčÄčé čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮčŗą╣ čüč湥čéčćąĖą║ CAN ą▓ čĆąĄąČąĖą╝ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ (time stamp mode, čāčüčéą░ąĮąŠą▓ą║ą░ UCCNF[3:0]=0x1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_UCCNF). ąóąŠą│ą┤ą░ 16-ą▒ąĖčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ąĖąĘ čüą▓ąŠą▒ąŠą┤ąĮąŠ čüčćąĖčéą░čÄčēąĄą│ąŠ čüč湥čéčćąĖą║ą░ (čĆąĄą│ąĖčüčéčĆ CAN_UCCNT) ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ CAN_MBxx_TIMESTAMP čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čÅčēąĖą║ą░, ą║ąŠą│ą┤ą░ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ čüąŠčģčĆą░ąĮąĄąĮąŠ ąĖą╗ąĖ ą║ąŠą│ą┤ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą┐ąĄčĆąĄą┤ą░ąĮąŠ.

ąŚąĮą░č湥ąĮąĖąĄ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░čģą▓ą░čéčŗą▓ą░ąĄčéčüčÅ ą▓ ą╝ąŠą╝ąĄąĮčé č鹊čćą║ąĖ ą▓čŗą▒ąŠčĆą║ąĖ ą▒ąĖčéą░ ąĮą░čćą░ą╗ą░ čäčĆąĄą╣ą╝ą░ (start of frame, SOF) ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐čĆąĖčģąŠą┤čÅčēąĄą│ąŠ ąĖą╗ąĖ čāčģąŠą┤čÅčēąĄą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ. ą¤ąŠąĘąČąĄ čŹč鹊 ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ą║ąŠą┐ąĖčĆčāąĄčéčüčÅ ą▓ čĆąĄą│ąĖčüčéčĆ CAN_MBxx_TIMESTAMP čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čÅčēąĖą║ą░.

ąĢčüą╗ąĖ čÅčēąĖą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čäčĆąĄą╣ą╝ąŠą▓ remote, č鹊 ąĘąĮą░č湥ąĮąĖąĄ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ (ą▓ čÅčēąĖą║, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ) ąĖą╗ąĖ ą┐čĆąĖąĄą╝ą░ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝ąŠą│ąŠ čäčĆąĄą╣ą╝ą░ ą┤ą░ąĮąĮčŗčģ (čÅčēąĖą║, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░).

ąĪč湥čéčćąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčćąĖčēąĄąĮ (čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ 1 ą▒ąĖčéą░ UCRC) ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ (čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▓ 0 ą▒ąĖčéą░ UCE) ąĘą░ą┐ąĖčüčīčÄ ą▓ čĆąĄą│ąĖčüčéčĆ CAN_UCCNF. ąĪč湥čéčćąĖą║ čéą░ą║ąČąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą│čĆčāąČąĄąĮ ąĘąĮą░č湥ąĮąĖąĄą╝ ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ čüą░ą╝ čĆąĄą│ąĖčüčéčĆ čüč湥čéčćąĖą║ą░ (CAN_UCCNT).

ąóą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ąŠčćąĖčüčéąĖčéčī čüč湥čéčćąĖą║ (CAN_UCCNT) ą┐čĆąĖ ą┐čĆąĖąĄą╝ąĄ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▓ čÅčēąĖą║ 4 (čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖčÅ ą▓čüąĄčģ čüč湥čéčćąĖą║ąŠą▓ ą╝ąĄč鹊ą║ ą▓čĆąĄą╝ąĄąĮąĖ ą▓ čüąĖčüč鹥ą╝ąĄ). ąŁč鹊 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą║ąŠą╣ ą▒ąĖčéą░ UCCT ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_UCCNF.

ą¤ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ čüč湥čéčćąĖą║ą░ čāčüčéą░ąĮąŠą▓ąĖčé ą▒ąĖčé ą▓ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN (ą▒ąĖčé UCEIS ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_GIS). ąōą╗ąŠą▒ą░ą╗čīąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CAN ą╝ąŠąČąĄčé ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ ą┐čĆąŠąĖąĘąŠą╣čéąĖ ą┐čāč鹥ą╝ ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▒ąĖčéą░ ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą╝ą░čüą║ąĖ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN (ą▒ąĖčé UCEIM ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_GIM). ąĢčüą╗ąĖ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąĄą╝ą░čüą║ąĖčĆąŠą▓ą░ąĮ, č鹊 čéą░ą║ąČąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ą▓ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ čäą╗ą░ą│ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN (ą▒ąĖčé UCEIF ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_GIF).

[ąÆčĆąĄą╝ąĄąĮąĮčŗą╣ ąĘą░ą┐čĆąĄčé čÅčēąĖą║ąŠą▓]

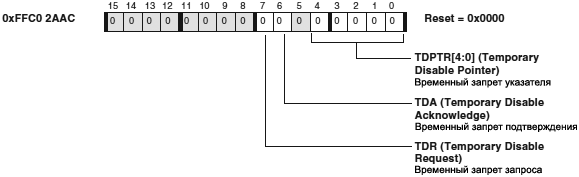

ąĢčüą╗ąĖ čŹč鹊čé čÅčēąĖą║ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠą╣ ąŠą▒čĆą░ą▒ąŠčéą║ąĖ čäčĆąĄą╣ą╝ąŠą▓ remote, č鹊 ą┐ąŠą╗ąĄ ą┤ą░ąĮąĮčŗčģ ą▓ ąĮąĄą╝ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠą▒ąĮąŠą▓ą╗ąĄąĮąŠ ą▒ąĄąĘ ą┐ąŠč鹥čĆąĖ ą▓čģąŠą┤čÅčēąĄą│ąŠ ąĘą░ą┐čĆą░čłąĖą▓ą░čÄčēąĄą│ąŠ čäčĆąĄą╣ą╝ą░ remote, ąĖ ą▒ąĄąĘ ąŠčéą┐čĆą░ą▓ą║ąĖ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮčŗčģ ą┤ą░ąĮąĮčŗčģ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ CAN ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčéąĖčéčī čÅčēąĖą║, čćč鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠčüčāčēąĄčüčéą▓ą╗ąĄąĮąŠ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖąĄą╝ čĆąĄą│ąĖčüčéčĆą░ ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čĆąĄčéą░ čÅčēąĖą║ą░ (mailbox temporary disable, čĆąĄą│ąĖčüčéčĆ CAN_MBTD).

ąŻą║ą░ąĘą░č鹥ą╗čī ąĮą░ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝čŗą╣ čÅčēąĖą║ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ąĘą░ą┐ąĖčüą░ąĮ ą▓ ą▒ąĖčéčŗ TDPTR[4:0] čĆąĄą│ąĖčüčéčĆą░ CAN_MBTD, ąĖ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ąĘą░ą┐čĆąŠčüą░ ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čĆąĄčéą░ čÅčēąĖą║ą░ (temporary disable request, TDR). ąÆąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣ ą▒čāą┤ąĄčé ą▓ą┐ąŠčüą╗ąĄą┤čüčéą▓ąĖąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čĆąĄčéą░ čÅčēąĖą║ą░ (temporary disable, TDA).

ąĢčüą╗ąĖ čÅčēąĖą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ą║ą░ą║ ą┐ąĄčĆąĄą┤ą░čÄčēąĖą╣ (MDn=0), ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą▒ąĖčé TDA, č鹊 čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą┐ąŠą╗čÅ ą┤ą░ąĮąĮčŗčģ čŹč鹊ą│ąŠ čÅčēąĖą║ą░ ą╝ąŠąČąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī. ąĢčüą╗ąĖ ą▓ čŹč鹊čé ą╝ąŠą╝ąĄąĮčé ą┐čĆąĖą┤ąĄčé ąĘą░ą┐čĆąŠčü čäčĆąĄą╣ą╝ą░ remote, ą┐ąŠą║ą░ čÅčēąĖą║ ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮ, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé ąĘą░ą┐čĆąŠčüą░ ą┐ąĄčĆąĄą┤ą░čćąĖ (TRSn) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣, ąĖ ą║ąŠą┤ DLC ą┐čĆąĖčłąĄą┤čłąĄą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ ąĘą░ą┐ąĖčłąĄčéčüčÅ ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čÅčēąĖą║. ą×ą┤ąĮą░ą║ąŠ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝ąŠąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ąĮąĄ ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ, ą┐ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄčé ąŠčćąĖčēąĄąĮ ąĘą░ą┐čĆąŠčü ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čĆąĄčéą░ (TDR=0). ą¤ąŠą┤ąŠą▒ąĮčŗą╝ ąŠą▒čĆą░ąĘąŠą╝ ą▓čüąĄ ąĘą░ą┐čĆąŠčüčŗ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą╗čÅ ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮąĮčŗčģ čÅčēąĖą║ąŠą▓ ą▒čāą┤čāčé ąĖą│ąĮąŠčĆąĖčĆąŠą▓ą░čéčīčüčÅ ą┤ąŠ ą╝ąŠą╝ąĄąĮčéą░ ąŠčćąĖčüčéą║ąĖ TDR. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą┐ąĄčĆąĄą┤ą░čćą░ čüąŠąŠą▒čēąĄąĮąĖčÅ ą▒čāą┤ąĄčé ąĮąĄą╝ąĄą┤ą╗ąĄąĮąĮąŠ ąŠą▒ąŠčĆą▓ą░ąĮą░, ąĄčüą╗ąĖ čÅčēąĖą║ ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮ, ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé TRRn ą┤ą╗čÅ čŹč鹊ą│ąŠ čÅčēąĖą║ą░.

ąĢčüą╗ąĖ čÅčēąĖą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą┐čĆąĖąĄą╝ (MDn=1), čäą╗ą░ą│ ą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ ąĘą░ą┐čĆąŠčüą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ąĖ čŹč鹊čé čÅčēąĖą║ ąĮąĄ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ. ąĢčüą╗ąĖ ą┐čĆąĖčłą╗ąŠ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┤ą╗čÅ čÅčēąĖą║ą░ n, ą║ąŠč鹊čĆčŗą╣ ą▓čĆąĄą╝ąĄąĮąĮąŠ ąĘą░ą┐čĆąĄčēąĄąĮ, č鹊 ą▓ąĮčāčéčĆąĄąĮąĮčÅčÅ ą╗ąŠą│ąĖą║ą░ ąČą┤ąĄčé ą┤ąŠ ąĘą░ą▓ąĄčĆčłąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ ąĖą╗ąĖ ąĄčüčéčī ąŠčłąĖą▒ą║ą░ čłąĖąĮčŗ CAN ą┤ą╗čÅ čāčüčéą░ąĮąŠą▓ą║ąĖ TDA. ąÜą░ą║ č鹊ą╗čīą║ąŠ TDA čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, čÅčēąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╗ąĮąŠčüčéčīčÄ ąĘą░ą┐čĆąĄčēąĄąĮ (MCn=0) ą▒ąĄąĘ čĆąĖčüą║ą░ ą┐ąŠč鹥čĆąĖ ą▓čģąŠą┤čÅčēąĄą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ. ąæąĖčé ąĘą░ą┐čĆąŠčüą░ ąĮą░ ą▓čĆąĄą╝ąĄąĮąĮčŗą╣ ąĘą░ą┐čĆąĄčé (TDR) ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüą▒čĆąŠčłąĄąĮ čéą░ą║ ą▒čŗčüčéčĆąŠ, ą║ą░ą║ čŹč鹊 č鹊ą╗čīą║ąŠ ą▓ąŠąĘą╝ąŠąČąĮąŠ.

ąÜąŠą│ą┤ą░ ą▒ąĖčé TDA čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą┤ą╗čÅ ąĖą╝ąĄčÄčēąĄą│ąŠčüčÅ čÅčēąĖą║ą░, ą╝ąŠąČąĮąŠ ąŠą▒ąĮąŠą▓ą╗čÅčéčī č鹊ą╗čīą║ąŠ ą┐ąŠą╗ąĄ ą┤ą░ąĮąĮčŗčģ čŹč鹊ą│ąŠ čÅčēąĖą║ą░. ąöąŠčüčéčāą┐ ą║ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ ą▒ąĖčéą░ą╝ ąĖ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆčā ąĘą░ą┐čĆąĄčēąĄąĮ.

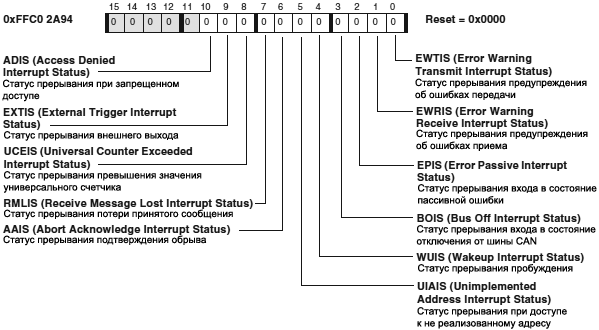

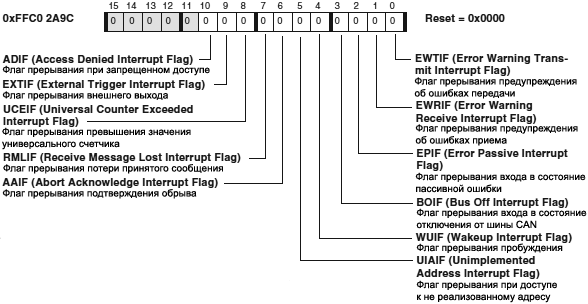

[ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CAN]

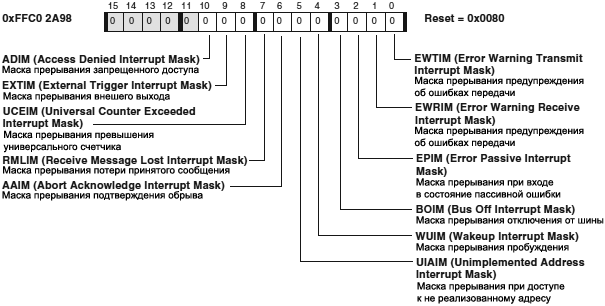

ą£ąŠą┤čāą╗čī CAN ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé 3 ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ: 2 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čÅčēąĖą║ą░ (ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ čÅčēąĖą║ą░ MBRIRQ ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ čÅčēąĖą║ą░ MBTIRQ), ąĖ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ CAN GIRQ. ąŚąĮą░č湥ąĮąĖčÅ čŹčéąĖčģ čéčĆąĄčģ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ą╝ąŠą│čāčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣.

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čÅčēąĖą║ą░. ąÜą░ąČą┤čŗą╣ ąĖąĘ 32 čÅčēąĖą║ąŠą▓ ą╝ąŠą┤čāą╗čÅ CAN ą╝ąŠąČąĄčé ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĖąĄą╝ą░ ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ čÅčēąĖą║ą░. ą¦č鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čÅčēąĖą║čā ą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░čéčī ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ, čāčüčéą░ąĮąŠą▓ąĖč鹥 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé MBIMn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MBIMx.

ąĢčüą╗ąĖ čÅčēąĖą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą┐čĆąĖąĄą╝, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ (MBRIFn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MBRIFx) ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ čÅčēąĖą║ n (RMPn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_RMPx). ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ čäčĆąĄą╣ą╝ą░ remote, č鹊 čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝čŗą╣ čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé čüąŠčģčĆą░ąĮąĄąĮ ą▓ čÅčēąĖą║. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗čÄą▒ąŠą╣ ą▒ąĖčé MBRIFn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MBRIFx, č鹊 ą▓čŗčģąŠą┤ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ MBRIRQ ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_INTR. ą¦č鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ MBRIRQ, ą▓čüąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗąĄ ą▒ąĖčéčŗ MBRIFn ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ 1 ą▓ čŹčéąĖ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CAN_MBRIFx.

ąĢčüą╗ąĖ čÅčēąĖą║ čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā, čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (MBTIFn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MBTIFx) ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▓ čÅčēąĖą║ąĄ n ą▒čāą┤ąĄčé čāčüą┐ąĄčłąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ (TAn=1 ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_TAx). ąæąĖčéčŗ TAn čüąŠčģčĆą░ąĮčÅčé čüąŠčüč鹊čÅąĮąĖąĄ ą┤ą░ąČąĄ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ čÅčēąĖą║ n ąĘą░ą┐čĆąĄčēąĄąĮ (MCn=0). ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ą░čÅ ąŠą▒čĆą░ą▒ąŠčéą║ą░ čäčĆąĄą╣ą╝ą░ remote, čäą╗ą░ą│ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą┐ąŠčüą╗ąĄ č鹊ą│ąŠ, ą║ą░ą║ ąĘą░ą┐čĆą░čłąĖą▓ą░ąĄą╝čŗą╣ čäčĆąĄą╣ą╝ ą┤ą░ąĮąĮčŗčģ ą▒čāą┤ąĄčé ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ ąĖąĘ čŹč鹊ą│ąŠ čÅčēąĖą║ą░. ąĢčüą╗ąĖ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ ą╗čÄą▒ąŠą╣ ą▒ąĖčé MBTIFn ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_MBTIFx, ą▒čāą┤ąĄčé čüą│ąĄąĮąĄčĆąĖčĆąŠą▓ą░ąĮ ą▓čŗčģąŠą┤ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ MBTIRQ ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_INTR. ą¦č鹊ą▒čŗ ąŠčćąĖčüčéąĖčéčī ąĘą░ą┐čĆąŠčü ąĮą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ MBTIRQ, ą▓čüąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗąĄ ą▒ąĖčéčŗ MBTIFn ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠčćąĖčēąĄąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ ąĘą░ą┐ąĖčüčīčÄ 1 ą▓ čŹčéąĖ ą▒ąĖčéčŗ čĆąĄą│ąĖčüčéčĆą░ CAN_MBTIFx.

ąōą╗ąŠą▒ą░ą╗čīąĮąŠąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüčéą░čéčāčüą░ CAN. ąøąŠą│ąĖą║ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ čüąŠčüč鹊čÅąĮąĖčÅ CAN (global CAN status interrupt) čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮą░ čü čéčĆąĄą╝čÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ - čĆąĄą│ąĖčüčéčĆ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą╣ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN (global CAN interrupt mask, CAN_GIM), ą│ą┤ąĄ ą║ą░ąČą┤čŗą╣ ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆąĄčłąĄąĮ ąĖą╗ąĖ ąĘą░ą┐čĆąĄčēąĄąĮ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠ; ą│ą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čüąŠčüč鹊čÅąĮąĖčÅ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CAN (global CAN interrupt status, CAN_GIS); ąĖ ą│ą╗ąŠą▒ą░ą╗čīąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ čäą╗ą░ą│ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CAN (global CAN interrupt flag, CAN_GIF). ąæąĖčéčŗ ą╝ą░čüą║ąĖ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą▓ą╗ąĖčÅčÄčé č鹊ą╗čīą║ąŠ ąĮą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ čäą╗ą░ą│ąŠą▓ CAN (CAN_GIF). ąĢčüą╗ąĖ ą▒ąĖčé ą╝ą░čüą║ąĖ ąĮąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čäą╗ą░ą│ą░ ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čüąŠą▒čŗčéąĖąĄ. ą×ą┤ąĮą░ą║ąŠ ą▒ąĖčéčŗ čüąŠčüč鹊čÅąĮąĖčÅ ą▓ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą╝ čĆąĄą│ąĖčüčéčĆąĄ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ (CAN_GIS) ą▓čüąĄ čĆą░ą▓ąĮąŠ čāčüčéą░ąĮąŠą▓čÅčéčüčÅ, ąĄčüą╗ąĖ ą┐čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄąĄ čüąŠą▒čŗčéąĖąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čüąŠčüč鹊čÅąĮąĖčÅ ą▒ąĖčé ą╝ą░čüą║ąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą▒ąĖčéčŗ čüčéą░čéčāčüą░ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤ą╗čÅ ąŠą┐čĆąŠčüą░ ąĮą░ą╗ąĖčćąĖčÅ čüąŠą▒čŗčéąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ.

ąæąĖčé ą▓čŗčģąŠą┤ą░ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ CAN (global CAN status interrupt output, GIRQ) ą▓ čĆąĄą│ąĖčüčéčĆąĄ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠą│ąŠ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ CAN (čĆąĄą│ąĖčüčéčĆ CAN_GIS) čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ CAN_GIF. ąæąĖčé GIRQ ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝, ą┐ąŠą║ą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čģąŠčéčÅ ą▒čŗ ąŠą┤ąĖąĮ ą▒ąĖčé ą▓ čĆąĄą│ąĖčüčéčĆąĄ čäą╗ą░ą│ąŠą▓ CAN_GIF. ąÆčüąĄ ą▒ąĖčéčŗ ą▓ čĆąĄą│ąĖčüčéčĆą░čģ čüčéą░čéčāčüą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ čäą╗ą░ą│ąŠą▓ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąŠčüčéą░ąĮčāčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝ąĖ, ą┐ąŠą║ą░ ąŠąĮąĖ ąĮąĄ ą▒čāą┤čāčé ąŠčćąĖčēąĄąĮčŗ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠ, ąĖą╗ąĖ ą┐ąŠą║ą░ ąĮąĄ ą┐čĆąŠąĖąĘąŠą╣ą┤ąĄčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĮčŗą╣ čüą▒čĆąŠčü.

ąŚą░ą╝ąĄčćą░ąĮąĖąĄ: ą▓ ąŠą▒čĆą░ą▒ąŠčéčćąĖą║ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ (ISR) ąĘą░čēąĄą╗ą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąŠčćąĖčēąĄąĮą░ ąŠą┐ąĄčĆą░čåąĖąĄą╣ ąĘą░ą┐ąĖčüąĖ W1C ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╣ ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ CAN_GIS. ąŁč鹊 ąŠčćąĖčüčéąĖčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą▒ąĖčéčŗ ą▓ ąŠą▒ąŠąĖčģ čĆąĄą│ąĖčüčéčĆą░čģ CAN_GIS ąĖ CAN_GIF.

ąØąĄčüą║ąŠą╗čīą║ąŠ čüąŠą▒čŗčéąĖą╣ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą╝ąŠą│čāčé ą░ą║čéąĖą▓ąĖčĆąŠą▓ą░čéčī čŹč鹊 ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ GIRQ:

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ąĘą░ą┐čĆąĄčéą░ ą┤ąŠčüčéčāą┐ą░ (access denied interrupt, ADIM, ADIS, ADIF). ąÜą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą┤ąŠčüčéčāą┐ ą║ RAM čÅčēąĖą║ą░ ą┐čĆąŠąĖąĘąŠčłąĄą╗ ą▓ąŠ ą▓čĆąĄą╝čÅ ąŠą▒ąĮąŠą▓ą╗ąĄąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą▓ąĮčāčéčĆąĄąĮąĮąĄą╣ ą╗ąŠą│ąĖą║ąŠą╣.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ čüčĆą░ą▒ą░čéčŗą▓ą░ąĮąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓čŗčģąŠą┤ą░ (external trigger output interrupt, EXTIM, EXTIS, EXTIF). ą¤čĆąŠąĖąĘąŠčłą╗ąŠ čüąŠą▒čŗčéąĖąĄ ą▓ąĮąĄčłąĮąĄą│ąŠ čéčĆąĖą│ą│ąĄčĆą░.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄą▓čŗčłąĄąĮąĖčÅ ąĘąĮą░č湥ąĮąĖčÅ čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ (universal counter exceeded interrupt, UCEIM, UCEIS, UCEIF). ąæčŗą╗ąŠ ą┐ąĄčĆąĄą┐ąŠą╗ąĮąĄąĮąĖąĄ čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮąŠą│ąŠ čüč湥čéčćąĖą║ą░ (ą▓ čĆąĄąČąĖą╝ąĄ ą╝ąĄčéą║ąĖ ą▓čĆąĄą╝ąĄąĮąĖ time stamp ąĖą╗ąĖ ą▓ čĆąĄąČąĖą╝ąĄ ą┐ąŠą┤čüč湥čéą░ čüąŠą▒čŗčéąĖą╣ event counter) ąĖą╗ąĖ čüč湥čéčćąĖą║ ą┤ąŠčüčéąĖą│ ąĘąĮą░č湥ąĮąĖčÅ 0x0000 (ą▓ čüč鹊čĆąŠąČąĄą▓ąŠą╝ čĆąĄąČąĖą╝ąĄ, watchdog mode).

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠč鹥čĆąĖ ą┐čĆąĖąĮčÅč鹊ą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ (receive message lost interrupt, RMLIM, RMLIS, RMLIF). ąĪąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ą┤ą╗čÅ čÅčēąĖą║ą░, ą║ąŠč鹊čĆčŗą╣ čüąŠą┤ąĄčƹȹ░ą╗ ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ. ąŻčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ 1 ą▒ąĖčé čĆąĄą│ąĖčüčéčĆą░ ą┐ąŠč鹥čĆčÅąĮąĮąŠą│ąŠ čüąŠąŠą▒čēąĄąĮąĖčÅ ą┐čĆąĖąĄą╝ą░ (receive message lost, CAN_RMLx). ąĢčüą╗ąĖ ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) čüą▒čĆąŠčłąĄąĮ, ąĖ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą▒ąĖčé ą▓ CAN_RMLx ą▓čüąĄ ąĄčēąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĮąŠą▓ą░. ąĪąĖą│ąĮą░ą╗ ą▓ąĮčāčéčĆąĄąĮąĮąĄą│ąŠ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą░ą║čéąĖą▓ąĄąĮ č鹊ą╗čīą║ąŠ ąĄčüą╗ąĖ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ąĮąŠą▓čŗą╣ ą▒ąĖčé ą▓ CAN_RMLx.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąŠą▒čĆčŗą▓ą░ (abort acknowledge interrupt, AAIM, AAIS, AAIF). ąŻčüčéą░ąĮąŠą▓ąĖą╗čüčÅ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą▒ąĖčé AAn ą▓ čĆąĄą│ąĖčüčéčĆą░čģ ą┐ąŠą┤čéą▓ąĄčƹȹ┤ąĄąĮąĖčÅ ąŠą▒čĆčŗą▓ą░ (abort acknowledge, CAN_AAx). ąĢčüą╗ąĖ ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) čüą▒čĆąŠčłąĄąĮ, ąĖ ą║ą░ą║ ą╝ąĖąĮąĖą╝čāą╝ ąŠą┤ąĖąĮ ą▒ąĖčé ą▓ CAN_AAx ą▓čüąĄ ąĄčēąĄ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ, č鹊 ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĮąŠą▓ą░. ąÆąĮčāčéčĆąĄąĮąĮąĖą╣ čüąĖą│ąĮą░ą╗ ąĖčüč鹊čćąĮąĖą║ą░ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą░ą║čéąĖą▓ąĄąĮ č鹊ą╗čīą║ąŠ ą┐čĆąĖ čāčüčéą░ąĮąŠą▓ą║ąĄ ąĮąŠą▓ąŠą│ąŠ ą▒ąĖčéą░ ą▓ CAN_AAx. ąæąĖčéčŗ AAn čüąŠčģčĆą░ąĮčÅčé čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ą┤ą░ąČąĄ ą┐ąŠčüą╗ąĄ ąĘą░ą┐čĆąĄčéą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čÅčēąĖą║ą░ n (MCn=0).

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą┐čĆąĖ ą┐ąŠą┐čŗčéą║ąĄ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąĮąŠą╝čā ą░ą┤čĆąĄčüčā (access to unimplemented address interrupt, UIAIM, UIAIS, UIAIF). ąæčŗą╗ ą┤ąŠčüčéčāą┐ čüąŠ čüč鹊čĆąŠąĮčŗ CPU ą║ ą░ą┤čĆąĄčüčā, ą║ąŠč鹊čĆčŗą╣ ąĮąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮ ą▓ ą╝ąŠą┤čāą╗ąĄ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąŠą▒čāąČą┤ąĄąĮąĖčÅ (wakeup interrupt, WUIM, WUIS, WUIF). ą£ąŠą┤čāą╗čī CAN ą▓čŗčłąĄą╗ ąĖąĘ čĆąĄąČąĖą╝ą░ čüąĮą░, ą┐ąŠč鹊ą╝čā čćč鹊 ą▒čŗą╗ą░ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮą░ ą░ą║čéąĖą▓ąĮąŠčüčéčī ąĮą░ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą▓čŗą║ą╗čÄč湥ąĮąĖčÅ čłąĖąĮčŗ (Bus-Off interrupt, BOIM, BOIS, BOIF). ą£ąŠą┤čāą╗čī CAN ą▓ąŠčłąĄą╗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ bus-off. ąŁč鹊čé ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ą░ą║čéąĖą▓ąĄąĮ, ąĄčüą╗ąĖ čüčéą░čéčāčü čÅą┤čĆą░ CAN ą┐ąŠą╝ąĄąĮčÅą╗ąŠčüčī ąŠčé ąĮąŠčĆą╝ą░ą╗čīąĮąŠą│ąŠ čĆą░ą▒ąŠč湥ą│ąŠ čĆąĄąČąĖą╝ą░ (normal operation mode) ą║ čĆąĄąČąĖą╝čā ąŠčéą║ą╗čÄč湥ąĮąĖčÅ čłąĖąĮčŗ (bus-off mode). ąĢčüą╗ąĖ ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) čüą▒čĆąŠčłąĄąĮ, ąĖ čüąŠčüč鹊čÅąĮąĖąĄ čĆąĄąČąĖą╝ą░ bus-off ą▓čüąĄ ąĄčēąĄ ą░ą║čéąĖą▓ąĮąŠ, č鹊 čŹč鹊čé ą▒ąĖčé ąĮąĄ ą▒čāą┤ąĄčé čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ čüąĮąŠą▓ą░. ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ bus-off, č鹊 ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐ą░čüčüąĖą▓ąĮąŠą╣ ąŠčłąĖą▒ą║ąĖ (Error-Passive interrupt, EPIM, EPIS, EPIF). ą£ąŠą┤čāą╗čī CAN ą▓ąŠčłąĄą╗ ą▓ čüąŠčüč鹊čÅąĮąĖąĄ error-passive. ąŁč鹊čé ąĖčüč鹊čćąĮąĖą║ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą░ą║čéąĖą▓ąĄąĮ, ąĄčüą╗ąĖ ą╝ąŠą┤čāą╗čī CAN ą┐ąŠą╝ąĄąĮčÅą╗ čüą▓ąŠąĄ čüąŠčüč鹊čÅąĮąĖąĄ ąŠčé čĆąĄąČąĖą╝ą░ ą░ą║čéąĖą▓ąĮąŠą╣ ąŠčłąĖą▒ą║ąĖ (error-active mode) ąĮą░ čĆąĄąČąĖą╝ ą┐ą░čüčüąĖą▓ąĮąŠą╣ ąŠčłąĖą▒ą║ąĖ (error-passive mode). ąĢčüą╗ąĖ ą▒ąĖčé CAN_GIS (ąĖ CAN_GIF) čüą▒čĆąŠčłąĄąĮ, ąĖ čĆąĄąČąĖą╝ error-passive ą▓čüąĄ ąĄčēąĄ ą░ą║čéąĖą▓ąĄąĮ, č鹊 čŹč鹊čé ą▒ąĖčé ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĮąŠą▓ą░. ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ error-passive, ą▒ąĖčé CAN_GIS (ąĖ CAN_GIF) ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ ą┐čĆąĖąĄą╝ą░ (Error warning receive interrupt, EWRIM, EWRIS, EWRIF). ąĪč湥čéčćąĖą║ ąŠčłąĖą▒ąŠą║ CAN (CAN receive error counter, RXECNT) ą┤ąŠčüčéąĖą│ ą┐čĆąĄą┤ąĄą╗ą░ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ. ąĢčüą╗ąĖ ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) čüą▒čĆąŠčłąĄąĮ, ąĖ čĆąĄąČąĖą╝ error warning ą▓čüąĄ ąĄčēąĄ ą░ą║čéąĖą▓ąĄąĮ, č鹊 čŹč鹊čé ą▒ąĖčé ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĮąŠą▓ą░. ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ error warning, č鹊 ą▒ąĖčé CAN_GIS (ąĖ CAN_GIF) ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝.

ŌĆó ą¤čĆąĄčĆčŗą▓ą░ąĮąĖąĄ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ ąŠčłąĖą▒ą║ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (Error warning transmit interrupt, EWTIM, EWTIS, EWTIF). ąĪč湥čéčćąĖą║ ąŠčłąĖą▒ąŠą║ ą┐ąĄčĆąĄą┤ą░čćąĖ CAN (CAN transmit error counter, TXECNT) ą┤ąŠčüčéąĖą│ ą┐čĆąĄą┤ąĄą╗ą░ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ. ąĢčüą╗ąĖ ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) čüą▒čĆąŠčłąĄąĮ, ąĖ čĆąĄąČąĖą╝ error warning ą▓čüąĄ ąĄčēąĄ ą░ą║čéąĖą▓ąĄąĮ, čŹč鹊čé ą▒ąĖčé ąĮąĄ čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ čüąĮąŠą▓ą░. ąĢčüą╗ąĖ ą╝ąŠą┤čāą╗čī ą▓čŗą╣ą┤ąĄčé ąĖąĘ čĆąĄąČąĖą╝ą░ error warning, ą▒ąĖčé ą▓ CAN_GIS (ąĖ CAN_GIF) ąŠčüčéą░ąĮąĄčéčüčÅ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮčŗą╝.

[ąĪč湥čéčćąĖą║ čüąŠą▒čŗčéąĖą╣]

ąöą╗čÅ ą┤ąĖą░ą│ąĮąŠčüčéąĖč湥čüą║ąĖčģ čäčāąĮą║čåąĖą╣ ą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čāąĮąĖą▓ąĄčĆčüą░ą╗čīąĮčŗą╣ čüč湥čéčćąĖą║ CAN ą║ą░ą║ čüč湥čéčćąĖą║ čüąŠą▒čŗčéąĖą╣ (event counter). ąĪč湥čéčćąĖą║ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮ 4-ą▒ąĖčéąĮčŗą╝ ą┐ąŠą╗ąĄą╝ UCCNF[3:0] čĆąĄą│ąĖčüčéčĆą░ CAN_UCCNF čćč鹊ą▒čŗ ąŠąĮ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆąŠą▓ą░ą╗čüčÅ ą┐čĆąĖ ąŠą┤ąĮąŠą╝ ąĖąĘ čŹčéąĖčģ čüąŠą▒čŗčéąĖą╣:

ŌĆó UCCNF[3:0] = 0x6 ŌĆō CAN error frame. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ, ąĄčüą╗ąĖ ąĮą░ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ čäčĆąĄą╣ą╝ ąŠčłąĖą▒ą║ąĖ.

ŌĆó UCCNF[3:0] = 0x7 ŌĆō CAN overload frame. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ, ąĄčüą╗ąĖ ąĮą░ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN ą┐ąŠčÅą▓ą╗čÅąĄčéčüčÅ čäčĆąĄą╣ą╝ ą┐ąĄčĆąĄą│čĆčāąĘą║ąĖ (overload frame).

ŌĆó UCCNF[3:0] = 0x8 ŌĆō Lost arbitration. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąŠąĖą│čĆčŗčł ą░čĆą▒ąĖčéčĆą░ąČą░ ąĮą░ ą╗ąĖąĮąĖąĖ CAN ą▓ąŠ ą▓čĆąĄą╝čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ŌĆó UCCNF[3:0] = 0x9 ŌĆō Transmission aborted. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐čĆąŠąĖą│čĆčŗčł ą░čĆą▒ąĖčéčĆą░ąČą░ ąĖą╗ąĖ ąĘą░ą┐čĆąŠčü ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ąŠčéą╝ąĄąĮąĄąĮ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ AAn).

ŌĆó UCCNF[3:0] = 0xA ŌĆō Transmission succeeded. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮąŠ ą▒ąĄąĘ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąŠčłąĖą▒ąŠą║ (čāčüą┐ąĄčłąĮą░čÅ ą┐ąĄčĆąĄą┤ą░čćą░, čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ TAn).

ŌĆó UCCNF[3:0] = 0xB ŌĆō Receive message rejected. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊 ą▒ąĄąĘ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ąŠą║, ąĮąŠ ąŠąĮąŠ ąĮąĄ ą▒čŗą╗ąŠ čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ čÅčēąĖą║ąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 ąĮąĄ ą▒čŗą╗ąŠ ąĮą░ą╣ą┤ąĄąĮąŠ čüąŠą▓ą┐ą░ą┤ą░čÄčēąĖčģ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆąŠą▓.

ŌĆó UCCNF[3:0] = 0xC ŌĆō Receive message lost. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ą┐čĆąĖąĮčÅč鹊 ą▒ąĄąĘ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčłąĖą▒ąŠą║, ąĮąŠ ąŠąĮąŠ ąĮąĄ ą▒čŗą╗ąŠ čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ čÅčēąĖą║ąĄ, ą┐ąŠč鹊ą╝čā čćč鹊 čÅčēąĖą║ čüąŠą┤ąĄčƹȹĖčé ąĮąĄ ą┐čĆąŠčćąĖčéą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ RMLn).

ŌĆó UCCNF[3:0] = 0xD ŌĆō Message received. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ą▒ąĄąĘ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąŠčłąĖą▒ąŠą║, ą▒čŗą╗ąŠ ą╗ąĖ ąŠąĮąŠ ąŠčéą▒čĆąŠčłąĄąĮąŠ ąĖą╗ąĖ čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ čÅčēąĖą║ąĄ.

ŌĆó UCCNF[3:0] = 0xE ŌĆō Message stored. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čüąŠąŠą▒čēąĄąĮąĖąĄ ą▒čŗą╗ąŠ ą┐čĆąĖąĮčÅč鹊 ą▒ąĄąĘ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąŠčłąĖą▒ąŠą║, ąĖą╝ąĄąĄčéčüčÅ čüąŠą▓ą┐ą░ą┤ą░čÄčēąĖą╣ ąĖą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ąĮą░ čĆą░ąĘčĆąĄčłąĄąĮąĮąŠą╝ čÅčēąĖą║ąĄ, ąĖ čüąŠąŠą▒čēąĄąĮąĖąĄ čüąŠčģčĆą░ąĮąĄąĮąŠ ą▓ ą┐čĆąĖąĄą╝ąĮąŠą╝ čÅčēąĖą║ąĄ (čāčüčéą░ąĮąŠą▓ą╗ąĄąĮ RMPn).

ŌĆó UCCNF[3:0] = 0xF ŌĆō Valid message. ąĪč湥čéčćąĖą║ ąĖąĮą║čĆąĄą╝ąĄąĮčéąĖčĆčāąĄčéčüčÅ ą║ą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ ąĮą░ ą╗ąĖąĮąĖąĖ čłąĖąĮčŗ CAN ą▒čŗą╗ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝ąŠąĄ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠąĄ ąĖą╗ąĖ ą┐čĆąĖąĮčÅč鹊ąĄ čüąŠąŠą▒čēąĄąĮąĖąĄ.

[ą¤čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ ąĖ ąŠčłąĖą▒ą║ąĖ CAN]

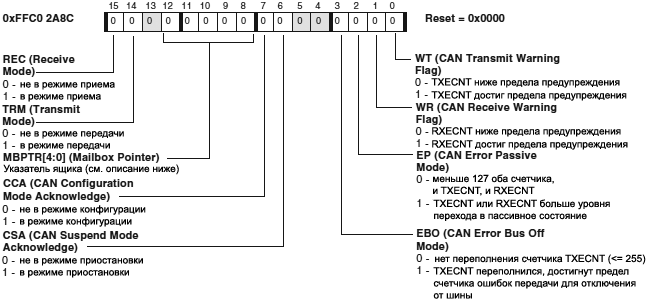

ą¤čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ ąĖ ąŠčłąĖą▒ą║ąĖ CAN čāą┐čĆą░ą▓ą╗čÅčÄčéčüčÅ čĆąĄą│ąĖčüčéčĆą░ą╝ąĖ CAN_CEC, CAN_ESR ąĖ CAN_EWR.

ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝čŗąĄ ą┐čĆąĄą┤ąĄą╗čŗ ą│ąĄąĮąĄčĆą░čåąĖąĖ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖą╣ (Programmable Warning Limits). ą£ąŠąČąĮąŠ ąĘą░ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī čāčĆąŠą▓ąĄąĮčī ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖą╣ čĆą░ąĘą┤ąĄą╗čīąĮąŠ ą┤ą╗čÅ EWTIS (error warning transmit interrupt status) ąĖ EWRIS (error warning receive interrupt status) ą┐čāč鹥ą╝ ąĘą░ą┐ąĖčüąĖ ą▓ ą┐ąŠą╗čÅ čāčĆąŠą▓ąĮčÅ čüč湥čéčćąĖą║ą░ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖą╣ ąŠą▒ ąŠčłąĖą▒ą║ą░čģ ą┤ą╗čÅ ą┐čĆąĖąĄą╝ą░ (EWLREC) ąĖ ą┐ąĄčĆąĄą┤ą░čćąĖ (EWLTEC) ą▓ čĆąĄą│ąĖčüčéčĆąĄ čāčĆąŠą▓ąĮčÅ ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖčÅ čüč湥čéčćąĖą║ą░ ąŠčłąĖą▒ąŠą║ CAN (CAN_EWR). ą¤ąŠčüą╗ąĄ čüą▒čĆąŠčüą░ ą┐čĆąĖ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆ CAN_EWR čāčüčéą░ąĮąŠą▓ąĖčéčüčÅ ą▓ čüą▓ąŠą╣ čāčĆąŠą▓ąĄąĮčī ą┐čĆąĄą┤čāą┐čĆąĄąČą┤ąĄąĮąĖą╣ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ 96 ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čüč湥čéčćąĖą║ąŠą▓ ąŠčłąĖą▒ąŠą║. ą¤ąŠčüą╗ąĄ ą┐čĆąŠą│čĆą░ą╝ą╝ąĮąŠą│ąŠ čüą▒čĆąŠčüą░ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ čŹč鹊ą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ąĮąĄ ąĖąĘą╝ąĄąĮčÅąĄčéčüčÅ.

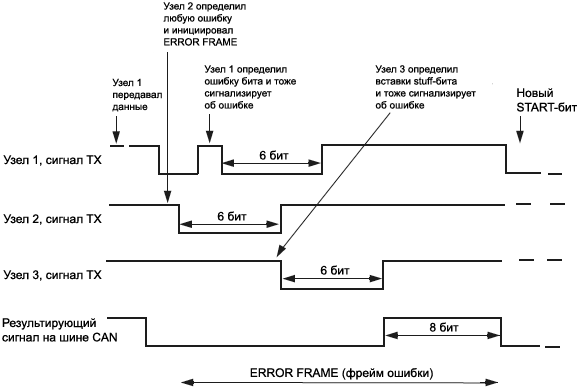

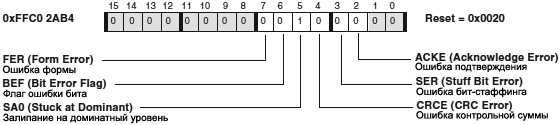

CAN Error Handling (ąŠą▒čĆą░ą▒ąŠčéą║ą░ ąŠčłąĖą▒ąŠą║ CAN). ąŻą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ ąŠčłąĖą▒ą║ą░ą╝ąĖ čÅą▓ą╗čÅąĄčéčüčÅ ąĖąĮč鹥ą│čĆą░ą╗čīąĮąŠą╣ čćą░čüčéčīčÄ čüčéą░ąĮą┤ą░čĆčéą░ CAN. ą¤čĆąĖ ą┐ąĄčĆąĄą┤ą░čćą░čģ ą╝ąŠą│čāčé ą▓ąŠąĘąĮąĖą║ą░čéčī 5 čĆą░ąĘąĮčŗčģ ą▓ąĖą┤ąŠą▓ ąŠčłąĖą▒ąŠą║:

ŌĆó Bit error (ąŠčłąĖą▒ą║ą░ ą▒ąĖčéą░). ąŁčéą░ ąŠčłąĖą▒ą║ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮą░ č鹊ą╗čīą║ąŠ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą╝ čāąĘą╗ąŠą╝. ąÜą░ąČą┤čŗą╣ čĆą░ąĘ, ą║ąŠą│ą┤ą░ čāąĘąĄą╗ ą┐ąĄčĆąĄą┤ą░ąĄčé, ąŠąĮ ą┐ąŠčüč鹊čÅąĮąĮąŠ ą╝ąŠąĮąĖč鹊čĆąĖčé ą▓čŗą▓ąŠą┤ ą┐čĆąĖąĄą╝ą░ (CANRX) ąĖ čüčĆą░ą▓ąĮąĖą▓ą░ąĄčé ą┐čĆąĖąĮčÅčéčŗąĄ ą┤ą░ąĮąĮčŗąĄ čü ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗą╝ąĖ. ąÆąŠ ą▓čĆąĄą╝čÅ čäą░ąĘčŗ ą░čĆą▒ąĖčéčĆą░ąČą░ čāąĘąĄą╗ ą┐čĆąŠčüč鹊 ąŠčéą║ą╗ą░ą┤čŗą▓ą░ąĄčé ą┐ąĄčĆąĄą┤ą░čćčā, ąĄčüą╗ąĖ ą┐čĆąĖąĮčÅčéčŗąĄ ąĖ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ ąĮąĄ čüąŠą▓ą┐ą░ą┤ą░čÄčé (ą┐čĆąĖ ąĮąĄčüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĖ ą┐čĆąĄą┤ą┐ąŠą╗ą░ą│ą░ąĄčéčüčÅ ą┐ąŠč鹥čĆčÅ ą░čĆą▒ąĖčéčĆą░ąČą░). ą×ą┤ąĮą░ą║ąŠ ą┐ąŠčüą╗ąĄ čäą░ąĘčŗ ą░čĆą▒ąĖčéčĆą░ąČą░ (čé. ąĄ. ą║ą░ą║ č鹊ą╗čīą║ąŠ ą▒ąĖčé RTR ą▒čŗą╗ čāčüą┐ąĄčłąĮąŠ ąŠčéą┐čĆą░ą▓ą╗ąĄąĮ), ąŠčłąĖą▒ą║ą░ ą▒ąĖčéą░ čüąĖą│ąĮą░ą╗ąĖąĘąĖčĆčāąĄčé ą▓ ą╗čÄą▒ąŠąĄ ą▓čĆąĄą╝čÅ ąŠčé č鹊ą╝, čćč鹊 ąĘąĮą░č湥ąĮąĖąĄ ąĮą░ CANRX ąĮąĄ čĆą░ą▓ąĮąŠ ą┐ąĄčĆąĄą┤ą░ąĮąĮąŠą╝čā č湥čĆąĄąĘ CANTX.