|

ESP32 čŹč鹊 ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ, ąŠčüąĮąŠą▓ą░ąĮąĮčŗą╣ ą┤ą▓čāčģ ąĮą░ čÅą┤čĆą░čģ Xtensa LX6 CPU čü ąōą░čĆą▓ą░čĆą┤čüą║ąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆąŠą╣ (ą┐ą░ą╝čÅčéčī ąĖąĮčüčéčĆčāą║čåąĖą╣ ąĖ ą┐ą░ą╝čÅčéčī ą┤ą░ąĮąĮčŗčģ čäąĖąĘąĖč湥čüą║ąĖ čĆą░ąĘą┤ąĄą╗ąĄąĮčŗ). ąÆčüčÅ ą▓čüčéčĆąŠąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī, ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čĆą░čüą┐ąŠą╗ąŠąČąĄąĮčŗ ąĮą░ čłąĖąĮąĄ ą┤ą░ąĮąĮčŗčģ ąĖ/ąĖą╗ąĖ ą║ąŠą╝ą░ąĮą┤ čŹčéąĖčģ CPU.

ą¤čĆąĖą╝ąĄčćą░ąĮąĖąĄ: ąĘą┤ąĄčüčī ą┐čĆąĖą▓ąĄą┤ąĄąĮ ą┐ąĄčĆąĄą▓ąŠą┤ čĆą░ąĘą┤ąĄą╗ą░ "System and Memory" č鹥čģąĮąĖč湥čüą║ąŠą│ąŠ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ą░ esp32_technical_reference_manual_en.pdf [1]. ąØąĄąĘąĮą░ą║ąŠą╝čŗąĄ č鹥čĆą╝ąĖąĮčŗ ąĖ čüąŠą║čĆą░čēąĄąĮąĖčÅ čüą╝. ą▓ ąĪą╗ąŠą▓ą░čĆąĖą║ąĄ, ą▓ ą║ąŠąĮčåąĄ čüčéą░čéčīąĖ.

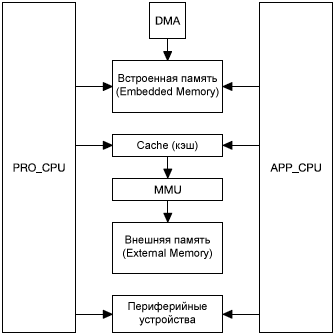

ąĪ ąĮąĄą║ąŠč鹊čĆčŗą╝ąĖ ąĮąĄą▒ąŠą╗čīčłąĖą╝ąĖ ąĖčüą║ą╗čÄč湥ąĮąĖčÅą╝ąĖ (čüą╝. ąŠą┐ąĖčüą░ąĮąĖąĄ ą┤ą░ą╗ąĄąĄ) ą║ą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ čŹčéąĖčģ ą┤ą▓čāčģ CPU čüąĖą╝ą╝ąĄčéčĆąĖčćąĮą░, čé. ąĄ. ąŠąĮąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąŠą┤ąĮąŠ ąĖ č鹊 ąČąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ąŠą┤ąĮąŠą╣ ąĖ č鹊ą╣ ąČąĄ ą┐ą░ą╝čÅčéąĖ. ąØąĄčüą║ąŠą╗čīą║ąŠ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą▓ čüąĖčüč鹥ą╝ąĄ ą╝ąŠą│čāčé ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ ą┐ą░ą╝čÅčéąĖ č湥čĆąĄąĘ DMA [2]. ąÆ čŹč鹊ą╝ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąĄ ąŠą▒ą░ CPU čāčüą╗ąŠą▓ąĮąŠ ąĖą╝ąĄąĮčāčÄčéčüčÅ ą║ą░ą║ PRO_CPU ąĖ APP_CPU (čé. ąĄ. ąŠą┤ąĖąĮ ą┐čĆąĄą┤ąĮą░ąĘąĮą░č湥ąĮ ą┤ą╗čÅ "ą┐čĆąŠč鹊ą║ąŠą╗ąŠą▓", ąĖ ą┤čĆčāą│ąŠą╣ ą┤ą╗čÅ "ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ"), ąŠą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖą╣ ąŠąĮąĖ čĆą░ą▓ąĮąŠą┐čĆą░ą▓ąĮčŗ ąĖ ą▓ąĘą░ąĖą╝ąŠąĘą░ą╝ąĄąĮčÅąĄą╝čŗ.

ą×čüąŠą▒ąĄąĮąĮąŠčüčéąĖ ą░ą┤čĆąĄčüą░čåąĖąĖ:

ŌĆō ąĪąĖą╝ą╝ąĄčéčĆąĖčćąĮąŠąĄ ą┤ą╗čÅ ą┤ą▓čāčģ CPU ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ąĮą░ ą║ą░čĆčéčā ą┐ą░ą╝čÅčéąĖ ą▒ą╗ąŠą║ąŠą▓ RAM ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

ŌĆō 4 GB ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ (čĆą░ąĘčĆčÅą┤ąĮąŠčüčéčī ą░ą┤čĆąĄčüą░ 32 ą▒ąĖčéą░) ą┤ą╗čÅ ąŠą▒ąŠąĖčģ čłąĖąĮ ą┤ą░ąĮąĮčŗčģ ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ŌĆō 1296 KB ą░ą┤čĆąĄčüąŠą▓ ą┤ą╗čÅ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆō 19704 KB ą░ą┤čĆąĄčüąŠą▓ ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ.

ŌĆō 512 KB ą░ą┤čĆąĄčüąŠą▓ ą┤ą╗čÅ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ (ą▓čüąĄą│ąŠ ąĖą╝ąĄąĄčéčüčÅ 41 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓).

ŌĆō ąÜ ąĮąĄą║ąŠč鹊čĆčŗą╝ čĆąĄą│ąĖąŠąĮą░ą╝ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ąĖ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą╗ąĖą▒ąŠ č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ, ą╗ąĖą▒ąŠ č湥čĆąĄąĘ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣.

ŌĆō 328 KB ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ DMA (ą▓čüąĄą│ąŠ ąĖą╝ąĄąĄčéčüčÅ 13 ą╝ąŠą┤čāą╗ąĄą╣ DMA).

ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī:

ŌĆō 448 KB Internal ROM.

ŌĆō 520 KB Internal SRAM.

ŌĆō 8 KB RTC FAST Memory.

ŌĆō 8 KB RTC SLOW Memory.

ąÆąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī. ąØą░čģąŠą┤čÅčēą░čÅčüčÅ ą▓ąĮąĄ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮą░čÅ ą┐ą░ą╝čÅčéčī SPI ą╝ąŠąČąĄčé ą▒čŗčéčī ąŠč鹊ą▒čĆą░ąČąĄąĮą░ ąĮą░ ą┤ąŠčüčéčāą┐ąĮąŠąĄ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ą║ą░ą║ ą▓ąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī. ą¦ą░čüčéąĖ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą║ą░ą║ ą┐čĆąŠąĘčĆą░čćąĮčŗą╣ ą║čŹčł ą┤ą╗čÅ čŹč鹊ą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ:

ŌĆō ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┤ąŠ 16 MB ą▓ąĮąĄčłąĮąĄą╣ SPI Flash.

ŌĆō ą¤ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčéčüčÅ ą┤ąŠ 8 MB ą▓ąĮąĄčłąĮąĄą╣ SPI SRAM.

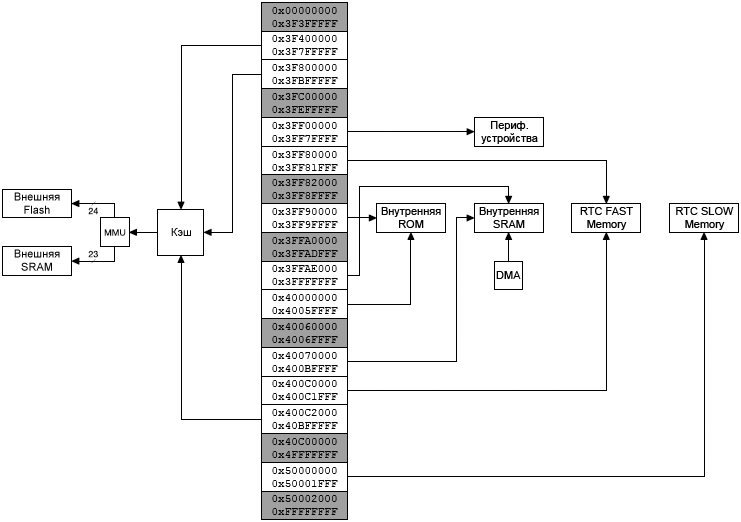

ąØą░ čĆąĖčü. 1 ą┐ąŠą║ą░ąĘą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ čüčéčĆčāą║čéčāčĆčŗ čüąĖčüč鹥ą╝čŗ, ą▒ą╗ąŠą║-čüčģąĄą╝ą░ čĆąĖčü. 2 ąĖą╗ą╗čÄčüčéčĆąĖčĆčāąĄčé čüčéčĆčāą║čéčāčĆčā ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░.

ąĀąĖčü. 1. ą×ą▒čēą░čÅ čüčéčĆčāą║čéčāčĆą░ čüąĖčüč鹥ą╝čŗ.

ąĀąĖčü. 2. ąĀą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░.

[ąÜą░čĆčéą░ ą┐ą░ą╝čÅčéąĖ]

ąÜą░ąČą┤čŗą╣ ąĖąĘ ą┤ą▓čāčģ Xtensa LX6 CPU ąōą░čĆą▓ą░čĆą┤čüą║ąŠą╣ ą░čĆčģąĖč鹥ą║čéčāčĆčŗ ąĖą╝ąĄąĄčé 4 GB ą░ą┤čĆąĄčüąĮąŠą│ąŠ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ (32-čĆą░ąĘčĆčÅą┤ąĮčŗą╣ ą░ą┤čĆąĄčü) address space. ąÉą┤čĆąĄčüąĮčŗąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ čüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗ ą╝ąĄąČą┤čā čŹčéąĖą╝ąĖ ą┤ą▓čāą╝čÅ CPU (čé. ąĄ. ąŠąĮąŠ ąŠą▒čēąĄąĄ).

ąÉą┤čĆąĄčüą░ ąĮąĖąČąĄ 0x40000000 ąŠą▒čüą╗čāąČąĖą▓ą░čÄčéčüčÅ č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ. ąÉą┤čĆąĄčüą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0x40000000 .. 0x4FFFFFFF ąŠą▒čüą╗čāąČąĖą▓ą░čÄčéčüčÅ čü ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄą╝ čłąĖąĮčŗ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąś ąĮą░ą║ąŠąĮąĄčå, ą░ą┤čĆąĄčüą░ ą▓čŗčłąĄ ąĖ ą▓ą║ą╗čÄčćą░čÅ 0x50000000 čüąŠą▓ą╝ąĄčüčéąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ čłąĖąĮą░ą╝ąĖ ą┤ą░ąĮąĮčŗčģ ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ąś čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ, ąĖ čłąĖąĮą░ ąĖąĮčüčéčĆčāą║čåąĖą╣, ąŠą▒ąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą┐čĆąĖąĮčåąĖą┐ ą┐ąŠčĆčÅą┤ą║ą░ ą▒ą░ą╣čé little-endian [3]. ąØą░ą┐čĆąĖą╝ąĄčĆ, ąĘąĮą░č湥ąĮąĖčÅ ą▒ą░ą╣č鹊ą▓čŗčģ ą░ą┤čĆąĄčüąŠą▓ 0, 1, 2, 3 čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ąŠą▒čĆą░čēą░čÄčéčüčÅ ą║ ąĮą░ąĖą╝ąĄąĮąĄąĄ ąĘąĮą░čćąĖą╝ąŠą╝čā, ą▓č鹊čĆąŠą╝čā ąĮą░ąĖą╝ąĄąĮąĄąĄ ąĘąĮą░čćąĖą╝ąŠą╝čā, ą▓č鹊čĆąŠą╝čā ą▒ąŠą╗ąĄąĄ ąĘąĮą░čćąĖą╝ąŠą╝čā ąĖ čüą░ą╝ąŠą╝čā ąĘąĮą░čćąĖą╝ąŠą╝čā ą▒ą░ą╣čéčā 32-čĆą░ąĘčĆčÅą┤ąĮąŠą│ąŠ čüą╗ąŠą▓ą░, čüąŠčģčĆą░ąĮąĄąĮąĮąŠą╝čā ą┐ąŠ ą░ą┤čĆąĄčüčā 0 (čé. ąĄ. č湥ą╝ ą▒ąŠą╗čīčłąĄ ą░ą┤čĆąĄčü, č鹥ą╝ ą▒ąŠą╗ąĄąĄ ąĘąĮą░čćąĖą╝čŗą╣ ą▒ą░ą╣čé čüą╗ąŠą▓ą░). CPU ą╝ąŠąČąĄčé ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ čłąĖąĮąĄ ą┤ą░ąĮąĮčŗčģ č湥čĆąĄąĘ ąŠą┐ąĄčĆą░čåąĖąĖ ąĮąĄ ą▓čŗčĆąŠą▓ąĮąĄąĮąĮąŠą│ąŠ ą▒ą░ą╣č鹊ą▓ąŠą│ąŠ ą┤ąŠčüčéčāą┐ą░, ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ čüą╗ąŠą▓ą░ ąĖ ą║ ą┐ąŠą╗ąĮąŠą╝čā čüą╗ąŠą▓čā ą┤ą╗čÅ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī. CPU ą╝ąŠąČąĄčé čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą┤ą░ąĮąĮčŗąĄ č湥čĆąĄąĘ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣, ąŠą┤ąĮą░ą║ąŠ č鹊ą╗čīą║ąŠ č湥čĆąĄąĘ ą┤ąŠčüčéčāą┐ ą║ čüą╗ąŠą▓ą░ą╝ (ą┐ąŠ ą▒ą░ą╣č鹊ą▓ąŠą╝čā ą░ą┤čĆąĄčüčā, ąĮą░čåąĄą╗ąŠ ą┤ąĄą╗čÅčēąĄą╝čāčüčÅ ąĮą░ 4). ąØąĄ ą▓čŗčĆąŠą▓ąĮąĄąĮąĮčŗą╣ ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣ ą┐čĆąĖą▓ąĄą┤ąĄčé ą║ ąŠčłąĖą▒ą║ąĄ ąĖčüą║ą╗čÄč湥ąĮąĖčÅ (CPU exception).

ąÜą░ąČą┤čŗą╣ CPU ą╝ąŠąČąĄčé ąĮą░ą┐čĆčÅą╝čāčÄ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ą║ą░ą║ č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ, čéą░ą║ ąĖ č湥čĆąĄąĘ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣, ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą║ąŠč鹊čĆą░čÅ ąŠč鹊ą▒čĆą░ąČąĄąĮą░ ąĮą░ ą░ą┤čĆąĄčüąĮąŠą╣ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ (č湥čĆąĄąĘ čüąĖčüč鹥ą╝čā ą┐čĆąŠąĘčĆą░čćąĮąŠą│ąŠ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ ąĖ MMU), ąĖ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝. ąóą░ą▒ą╗ąĖčåą░ 1 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ąĖą░ą┐ą░ąĘąŠąĮčŗ ą░ą┤čĆąĄčüąŠą▓, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ ąĖ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣ ą║ą░ąČą┤ąŠą│ąŠ CPU.

ąØąĄą║ąŠč鹊čĆčŗąĄ ąŠą▒ą╗ą░čüčéąĖ ą▓čüčéčĆąŠąĄąĮąĮąŠą╣ ą┐ą░ą╝čÅčéąĖ ąĖ ąĮąĄą║ąŠč鹊čĆčŗąĄ ąŠą▒ą╗ą░čüčéąĖ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ, ąĖą╗ąĖ č湥čĆąĄąĘ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣. ąÆ čŹčéąĖčģ čüą╗čāčćą░čÅčģ ąŠą┤ąĮą░ ąĖ čéą░ ąČąĄ ą┐ą░čÅčéčī ą┤ąŠčüčéčāą┐ąĮą░ ą┤ą╗čÅ ą╗čÄą▒ąŠą│ąŠ CPU ą▓ ą┤ą▓čāčģ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░čģ ą░ą┤čĆąĄčüąŠą▓.

ąóą░ą▒ą╗ąĖčåą░ 1. Address Mapping.

ą©ąĖąĮą░

|

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąĀą░ąĘą╝ąĄčĆ |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ |

| ą£ą╗ą░ą┤čłąĖą╣ ą░ą┤čĆąĄčü |

ąĪčéą░čĆčłąĖą╣ ą░ą┤čĆąĄčü |

|

0x00000000 |

0x3F3FFFFF |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| ąöą░ąĮąĮčŗąĄ |

0x3F400000 |

0x3F7FFFFF |

4 MB |

ąÆąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī |

| 0x3F800000 |

0x3FBFFFFF |

4 MB |

|

0x3FC00000 |

0x3FEFFFFF |

3 MB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| ąöą░ąĮąĮčŗąĄ |

0x3FF00000 |

0x3FF7FFFF |

512 KB |

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ |

| 0x3FF80000 |

0x3FFFFFFF |

512 KB |

ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī |

| ąśąĮčüčéčĆčāą║čåąĖąĖ |

0x40000000 |

0x400C1FFF |

776 KB |

| 0x400C2000 |

0x40BFFFFF |

11512 KB |

ąÆąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī |

|

0x40C00000 |

0x4FFFFFFF |

244 MB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

| ąöą░ąĮąĮčŗąĄ/ąĖąĮčüčéčĆčāą║čåąĖąĖ |

0x50000000 |

0x50001FFF |

8 KB |

ąÆčüčéčĆąŠąĄąĮąĮą░čÅ ą┐ą░ą╝čÅčéčī |

|

0x50002000 |

0xFFFFFFFF |

|

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

ąŁčéą░ ą┐ą░ą╝čÅčéčī čüąŠčüč鹊ąĖčé ąĖąĘ 4 čüąĄą│ą╝ąĄąĮč鹊ą▓: internal ROM (448 KB), internal SRAM (520 KB), RTC FAST memory (8 KB) ąĖ RTC SLOW memory (8 KB).

448 KB internal ROM ą┐ąŠą┤ąĄą╗ąĄąĮąŠ ąĮą░ 2 čćą░čüčéąĖ: Internal ROM 0 (384 KB) ąĖ Internal ROM 1 (64 KB). 520 KB internal SRAM ą┐ąŠą┤ąĄą╗ąĄąĮąŠ ąĮą░ 3 čćą░čüčéąĖ: Internal SRAM 0 (192 KB), Internal SRAM 1 (128 KB) ąĖ Internal SRAM 2 (200 KB). ą×ą▒ą╗ą░čüčéąĖ RTC FAST Memory ąĖ RTC SLOW Memory ąŠą▒ąĄ čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą║ą░ą║ SRAM.

ąÆ čéą░ą▒ą╗ąĖčåąĄ 2 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ ą▓čüčéčĆąŠąĄąĮąĮčŗąĄ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ ąĖ ąĖčģ ą┤ąĖą░ą┐ą░ąĘąŠąĮčŗ ą░ą┤čĆąĄčüąŠą▓ ąĮą░ čłąĖąĮą░čģ ą┤ą░ąĮąĮčŗčģ ąĖ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ąóą░ą▒ą╗ąĖčåą░ 2. Embedded Memory Address Mapping.

ą©ąĖąĮą░

|

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąĀą░ąĘą╝ąĄčĆ |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖą╣

|

| ą£ą╗ą░ą┤čłąĖą╣ ą░ą┤čĆąĄčü |

ąĪčéą░čĆčłąĖą╣ ą░ą┤čĆąĄčü |

| ąöą░ąĮąĮčŗąĄ |

0x3FF80000 |

0x3FF81FFF |

8 KB |

RTC FAST Memory |

ąóąŠą╗čīą║ąŠ PRO_CPU |

|

0x3FF82000 |

0x3FF8FFFF |

56 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

| ąöą░ąĮąĮčŗąĄ |

0x3FF90000 |

0x3FF9FFFF |

64 KB |

Internal ROM 1 |

- |

|

0x3FFA0000 |

0x3FFADFFF |

56 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

| ąöą░ąĮąĮčŗąĄ |

0x3FFAE000 |

0x3FFDFFFF |

200 KB |

Internal SRAM 2 |

DMA |

| 0x3FFE0000 |

0x3FFFFFFF |

128 KB |

Internal SRAM 1 |

| ąśąĮčüčéčĆčāą║čåąĖąĖ |

0x40000000 |

0x40007FFF |

32 KB |

Internal ROM 0 |

Remap |

| 0x40008000 |

0x4005FFFF |

352 KB |

- |

|

0x40060000 |

0x4006FFFF |

64 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

- |

| ąśąĮčüčéčĆčāą║čåąĖąĖ |

0x40070000 |

0x4007FFFF |

64 KB |

Internal SRAM 0 |

ąÜčŹčł |

| 0x40080000 |

0x4009FFFF |

128 KB |

- |

| 0x400A0000 |

0x400AFFFF |

64 KB |

Internal SRAM 1 |

- |

| 0x400B0000 |

0x400B7FFF |

32 KB |

Remap |

| 0x400B8000 |

0x400BFFFF |

32 KB |

- |

| 0x400C0000 |

0x400C1FFF |

8 KB |

RTC FAST Memory |

ąóąŠą╗čīą║ąŠ PRO_CPU |

| ąöą░ąĮąĮčŗąĄ/ąĖąĮčüčéčĆčāą║čåąĖąĖ |

0x50000000 |

0x50001FFF |

8 KB |

RTC SLOW Memory |

- |

Internal ROM 0. ąĢą╝ą║ąŠčüčéčī Internal ROM 0 čüąŠčüčéą░ą▓ą╗čÅąĄčé 384 KB. ą×ąĮą░ ą┤ąŠčüčéčāą┐ąĮą░ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ CPU č湥čĆąĄąĘ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ 0x40000000 .. 0x4005FFFF, ą║ąŠč鹊čĆčŗąĄ ąĮą░čģąŠą┤čÅčéčüčÅ ąĮą░ čłąĖąĮąĄ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ ą┐ąĄčĆą▓čŗčģ 32 KB ROM 0 (0x40000000 .. 0x40007FFF) ą╝ąŠą│čāčé ą▒čŗčéčī ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗ąĄąĮčŗ (remap), čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ čćą░čüčéąĖ Internal SRAM 1, ą║ąŠč鹊čĆą░čÅ ąĮąŠčĆą╝ą░ą╗čīąĮąŠ ąĮą░čģąŠą┤ąĖčéčüčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą░ą┤čĆąĄčüąŠą▓ 0x400B0000 .. 0x400B7FFF. ą¤čĆąĖ ą┐ąĄčĆąĄąĮą░ąĘąĮą░č湥ąĮąĖąĖ 32 KB SRAM ą▒ąŠą╗čīčłąĄ ąĮąĄ ą▒čāą┤čāčé ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ 0x400B0000 .. 0x400B7FFF, ąŠą┤ąĮą░ą║ąŠ čŹčéąĖ 32 KB SRAM ą▓čüąĄ ąĄčēąĄ ą▒čāą┤čāčé ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ (0x3FFE8000 .. 0x3FFEFFFF). ąŁč鹊 ą╝ąŠąČąĮąŠ ą┤ąĄą╗ą░čéčī ąĮą░ ą║ą░ąČą┤ąŠą╝ CPU: čāčüčéą░ąĮąŠą▓ą║ą░ ą▒ąĖčéą░ 0 čĆąĄą│ąĖčüčéčĆą░ DPORT_PRO_BOOT_REMAP_CTRL_REG ąĖą╗ąĖ DPORT_APP_BOOT_REMAP_CTRL_REG ą▒čāą┤ąĄčé ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗čÅčéčī (remap) SRAM ą┤ą╗čÅ PRO_CPU ąĖ APP_CPU čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ.

Internal ROM 1. ąĢą╝ą║ąŠčüčéčī Internal ROM 1 čüąŠčüčéą░ą▓ą╗čÅąĄčé 64 KB. ąĢą│ąŠ ą╝ąŠąČąĮąŠ ą┐čĆąŠčćąĖčéą░čéčī ą╗čÄą▒čŗą╝ CPU ą▓ ą░ą┤čĆąĄčüąĮąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 0x3FF90000 .. 0x3FF9FFFF čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ.

Internal SRAM 0. ąĢą╝ą║ąŠčüčéčī Internal SRAM 0 čüąŠčüčéą░ą▓ą╗čÅąĄčé 192 KB. ąÉą┐ą┐ą░čĆą░čéčāčĆą░ ą╝ąŠąČąĄčé ą▒čŗčéčī čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░ąĮą░ ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą┐ąĄčĆą▓čŗčģ 64 KB ą┤ą╗čÅ ą║čŹčłą░ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąÜąŠą│ą┤ą░ ą┐ąĄčĆą▓čŗąĄ 64 KB ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą║ą░ą║ ą║čŹčł, ąĖčģ ą╝ąŠąČąĮąŠ čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą╗čÄą▒čŗą╝ CPU ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 0x40070000 .. 0x4007FFFF čłąĖąĮčŗ ąĖąĮčüčéčĆčāą║čåąĖą╣. ą×čüčéą░ą╗čīąĮčŗąĄ 128 KB ą╝ąŠąČąĮąŠ ą▓čüąĄą│ą┤ą░ čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī ą╗čÄą▒čŗą╝ CPU ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 0x40080000 .. 0x4009FFFF čłąĖąĮčŗ ąĖąĮčüčéčĆčāą║čåąĖą╣.

Internal SRAM 1. ąĢą╝ą║ąŠčüčéčī Internal SRAM 1 čüąŠčüčéą░ą▓ą╗čÅąĄčé 128 KB. ąøčÄą▒ąŠą╣ CPU ą╝ąŠąČąĄčé čćąĖčéą░čéčī ąĖ ąĘą░ą┐ąĖčüčŗą▓ą░čéčī čŹčéčā ą┐ą░ą╝čÅčéčī ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 0x3FFE0000 .. 0x3FFFFFFF čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ąĖ čéą░ą║ąČąĄ ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 0x400A0000 .. 0x400B_FFFF čłąĖąĮčŗ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓, ą┤ąŠčüčéčāą┐ ą║ ą║ąŠč鹊čĆąŠą╝čā ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ č湥čĆąĄąĘ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣ ą▓ ąŠą▒čĆą░čéąĮąŠą╝ ą┐ąŠčĆčÅą┤ą║ąĄ (ą┐ąŠ čüą╗ąŠą▓ą░ą╝) ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü ą┤ąŠčüčéčāą┐ąŠą╝ č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ. ąóąŠ ąĄčüčéčī, ąŠą▒čĆą░čēąĄąĮąĖąĄ ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝:

0x3FFE0000 ąĖ 0x400BFFFC ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ čüą╗ąŠą▓čā

0x3FFE0004 ąĖ 0x400BFFF8 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ čüą╗ąŠą▓čā

0x3FFE0008 ąĖ 0x400BFFF4 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ čüą╗ąŠą▓čā

...

0x3FFFFFF4 ąĖ 0x400A0008 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ čüą╗ąŠą▓čā

0x3FFFFFF8 ąĖ 0x400A0004 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ čüą╗ąŠą▓čā

0x3FFFFFFC ąĖ 0x400A0000 ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ čüą╗ąŠą▓čā.

ą©ąĖąĮą░ ą┤ą░ąĮąĮčŗčģ ąĖ čłąĖąĮą░ ąĖąĮčüčéčĆčāą║čåąĖą╣ ą▓čüąĄ ąĄčēąĄ ąŠą▒ąĄ little-endian, čéą░ą║ čćč鹊 ą┐ąŠčĆčÅą┤ąŠą║ ą▒ą░ą╣čé ąŠčéą┤ąĄą╗čīąĮčŗčģ čüą╗ąŠą▓ ąĮąĄ čüčéą░ąĮąŠą▓ąĖčéčüčÅ ąŠą▒čĆą░čéąĮčŗą╝ ą╝ąĄąČą┤čā ą░ą┤čĆąĄčüąĮčŗą╝ąĖ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ą░ą╝ąĖ. ąØą░ą┐čĆąĖą╝ąĄčĆ, ą▒ą░ą╣č鹊ą▓čŗą╣ ą┤ąŠčüčéčāą┐ ą┐ąŠ ą░ą┤čĆąĄčüčā:

0x3FFE0000 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą░ą╝ąŠą╝čā ą╝ą╗ą░ą┤čłąĄą╝čā ąĘąĮą░čćą░čēąĄą╝čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400BFFFC.

0x3FFE0001 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400BFFFC.

0x3FFE0002 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400BFFFC.

0x3FFE0003 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą░ą╝ąŠą╝čā čüčéą░čĆčłąĄą╝čā ąĘąĮą░čćą░čēąĄą╝čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400BFFFC.

0x3FFE0004 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą░ą╝ąŠą╝čā ą╝ą╗ą░ą┤čłąĄą╝čā ąĘąĮą░čćą░čēąĄą╝čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400BFFF8.

0x3FFE0005 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400BFFF8.

0x3FFE0006 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400BFFF8.

0x3FFE0007 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą░ą╝ąŠą╝čā čüčéą░čĆčłąĄą╝čā ąĘąĮą░čćą░čēąĄą╝čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400BFFF8.

...

0x3FFFFFF8 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą░ą╝ąŠą╝čā ą╝ą╗ą░ą┤čłąĄą╝čā ąĘąĮą░čćą░čēąĄą╝čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400A0004.

0x3FFFFFF9 ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400A0004.

0x3FFFFFFA ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400A0004.

0x3FFFFFFB ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą░ą╝ąŠą╝čā čüčéą░čĆčłąĄą╝čā ąĘąĮą░čćą░čēąĄą╝čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400A0004.

0x3FFFFFFC ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą░ą╝ąŠą╝čā ą╝ą╗ą░ą┤čłąĄą╝čā ąĘąĮą░čćą░čēąĄą╝čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400A0000.

0x3FFFFFFD ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400A0000.

0x3FFFFFFE ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą╗ąĄą┤čāčÄčēąĄą╝čā ą┐ąŠ čüčéą░čĆčłąĖąĮčüčéą▓čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400A0000.

0x3FFFFFFF ą┤ą░ąĄčé ą┤ąŠčüčéčāą┐ ą║ čüą░ą╝ąŠą╝čā čüčéą░čĆčłąĄą╝čā ąĘąĮą░čćą░čēąĄą╝čā ą▒ą░ą╣čéčā čüą╗ąŠą▓ą░, ą┤ąŠčüčéčāą┐ąĮąŠą│ąŠ ą┐ąŠ ą░ą┤čĆąĄčüčā 0x400A0000.

ą¦ą░čüčéčī čŹč鹊ą╣ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąĄčĆąĄąĮą░ą┐čĆą░ą▓ą╗ąĄąĮą░ (remap) ąĮą░ ą░ą┤čĆąĄčüąĮąŠąĄ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąŠ ROM 0, čüą╝. "Internal Rom 0" ą┤ą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ.

Internal SRAM 2. ąĢą╝ą║ąŠčüčéčī Internal SRAM 2 čüąŠčüčéą░ą▓ą╗čÅąĄčé 200 KB. ą×ąĮą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮą░ ąĖ ąĘą░ą┐ąĖčüą░ąĮą░ ą╗čÄą▒čŗą╝ CPU ą┐ąŠ ą░ą┤čĆąĄčüą░ą╝ 0x3FFAE000 .. 0x3FFDFFFF čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ.

DMA. DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčé čéčā ąČąĄ čüą░ą╝čāčÄ čüčģąĄą╝čā ą░ą┤čĆąĄčüą░čåąĖąĖ, čćč鹊 ąĖ čłąĖąĮą░ ą┤ą░ąĮąĮčŗčģ CPU ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ Internal SRAM 1 ąĖ Internal SRAM 2. ąŁč鹊 ąĘąĮą░čćąĖčé, čćč鹊 DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ 0x3FFE0000 .. 0x3FFFFFFF ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ Internal SRAM 1, ąĖ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ 0x3FFAE000 .. 0x3FFD_FFFF ą┤ą╗čÅ čćč鹥ąĮąĖčÅ ąĖ ąĘą░ą┐ąĖčüąĖ Internal SRAM 2.

ąÆ ESP32 ą▒ą╗ąŠą║ą░ą╝ąĖ DMA ąŠą▒ąŠčĆčāą┤ąŠą▓ą░ąĮčŗ 13 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓, ą▓ čéą░ą▒ą╗ąĖčåąĄ 3 ą┐ąĄčĆąĄčćąĖčüą╗ąĄąĮčŗ čŹčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░.

ąóą░ą▒ą╗ąĖčåą░ 3. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░ čü ą╝ąŠą┤čāą╗čÅą╝ąĖ DMA.

| UART0 |

UART1 |

UART2 |

| SPI1 |

SPI2 |

SPI3 |

| I2S0 |

I2S1 |

| SDIO Slave |

SDMMC |

| EMAC |

| Bluetooth |

Wi-Fi |

RTC FAST Memory. RTC FAST Memory ąĘą░ąĮąĖą╝ą░ąĄčé 8 KB SRAM. ą×ąĮą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮą░ ąĖ ąĘą░ą┐ąĖčüą░ąĮą░ č鹊ą╗čīą║ąŠ čÅą┤čĆąŠą╝ PRO_CPU č湥čĆąĄąĘ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ 0x3FF80000 .. 0x3FF81FFF čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ąĖą╗ąĖ č湥čĆąĄąĘ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ 0x400C0000 .. 0x400C1FFF čłąĖąĮčŗ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąÆ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą▒ąŠą╗čīčłąĖąĮčüčéą▓ą░ ą┤čĆčāą│ąĖčģ ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ, ą║ ą┐ą░ą╝čÅčéąĖ RTC FAST ąĮąĄą╗čīąĘčÅ ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ąĖąĘ čÅą┤čĆą░ APP_CPU.

ąöą▓ą░ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ ą░ą┤čĆąĄčüąŠą▓ ą┤ąŠčüčéčāą┐ą░ PRO_CPU ą║ ą┐ą░ą╝čÅčéąĖ RTC FAST ąĖą╝ąĄčÄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą┐ąŠčĆčÅą┤ąŠą║. ąóą░ą║, ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą░ą┤čĆąĄčüą░ 0x3FF80000 ąĖ 0x400C0000 ąŠą▒čĆą░čēą░čÄčéčüčÅ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ čüą╗ąŠą▓čā. ąØą░ APP_CPU čŹčéąĖ ą░ą┤čĆąĄčüą░ ąĮąĄ ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┤ąŠčüčéčāą┐ ą║ RTC FAST Memory ąĖą╗ąĖ ą║ ą╗čÄą▒ąŠą╣ ą┤čĆčāą│ąŠą╣ ąŠą▒ą╗ą░čüčéąĖ ą┐ą░ą╝čÅčéąĖ.

RTC SLOW Memory. RTC SLOW Memory ąĘą░ąĮąĖą╝ą░ąĄčé 8 KB SRAM, ąĖ čŹčéą░ ąŠą▒ą╗ą░čüčéčī ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐čĆąŠčćąĖčéą░ąĮą░ ąĖ ąĘą░ą┐ąĖčüą░ąĮą░ ą╗čÄą▒čŗą╝ CPU ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą░ą┤čĆąĄčüąŠą▓ 0x50000000 .. 0x50001FFF. ąŁč鹊čé ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ąĖ ą┤ą╗čÅ čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ, ąĖ ą┤ą╗čÅ čłąĖąĮčŗ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ESP32 ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ SPI Flash ąĖ SPI SRAM ą▓ ą║ą░č湥čüčéą▓ąĄ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. ąóą░ą▒ą╗ąĖčåą░ 4 ą┐čĆąĄą┤ąŠčüčéą░ą▓ą╗čÅąĄčé čüą┐ąĖčüąŠą║ ąŠą▒ą╗ą░čüč鹥ą╣ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ, ą║ ą║ąŠč鹊čĆčŗą╝ ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ą╗čÄą▒ąŠą╣ CPU č湥čĆąĄąĘ čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ ąĖ čłąĖąĮčā ąĖąĮčüčéčĆčāą║čåąĖą╣. ąÜąŠą│ą┤ą░ CPU ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ č湥čĆąĄąĘ ą║čŹčł ąĖ MMU, ą║čŹčł ą▒čāą┤ąĄčé ąŠč鹊ą▒čĆą░ąČą░čéčī ą░ą┤čĆąĄčü CPU ąĮą░ ą▓ąĮąĄčłąĮąĖą╣ čäąĖąĘąĖč湥čüą║ąĖą╣ ą░ą┤čĆąĄčü ą┐ą░ą╝čÅčéąĖ (ą░ą┤čĆąĄčüąĮąŠą╝ ą┐čĆąŠčüčéčĆą░ąĮčüčéą▓ąĄ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ), ą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĖ čü ąĮą░čüčéčĆąŠą╣ą║ą░ą╝ąĖ MMU. ąĪ ą┐ąŠą╝ąŠčēčīčÄ čŹč鹊ą│ąŠ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ ą░ą┤čĆąĄčüąŠą▓ ESP32 ą╝ąŠąČąĄčé ą░ą┤čĆąĄčüąŠą▓ą░čéčī 16 MB External Flash ąĖ 8 MB External SRAM.

ąóą░ą▒ą╗ąĖčåą░ 4. External Memory Address Mapping.

ą©ąĖąĮą░

|

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąĀą░ąĘą╝ąĄčĆ |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖą╣

|

| ą£ą╗ą░ą┤čłąĖą╣ ą░ą┤čĆąĄčü |

ąĪčéą░čĆčłąĖą╣ ą░ą┤čĆąĄčü |

| ąöą░ąĮąĮčŗąĄ |

0x3F400000 |

0x3F7FFFFF |

4 MB |

External Flash |

ą¦č鹥ąĮąĖąĄ |

| 0x3F800000 |

0x3FBFFFFF |

4 MB |

External SRAM |

ą¦č鹥ąĮąĖąĄ ąĖ ąĘą░ą┐ąĖčüčī |

| ąśąĮčüčéčĆčāą║čåąĖąĖ |

0x400C2000 |

0x40BFFFFF |

11512 KB |

External Flash |

ą¦č鹥ąĮąĖąĄ |

ąÜčŹčł. ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 3, ą║ą░ąČą┤čŗą╣ ąĖąĘ ą┤ą▓čāčģ CPU ąĖą╝ąĄąĄčé 32 KB ą║čŹčłą░ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą▓ąĮąĄčłąĮąĄą╣ ą┐ą░ą╝čÅčéąĖ. PRO_CPU ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčé PRO_CACHE_ENABLE ą▓ čĆąĄą│ąĖčüčéčĆąĄ DPORT_PRO_CACHE_CTRL_REG, čćč鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī ą║čŹčł, ą▓ č鹊 ą▓čĆąĄą╝čÅ ą║ą░ą║ APP_CPU ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą▒ąĖčé APP_CACHE_ENABLE ą▓ čĆąĄą│ąĖčüčéčĆąĄ DPORT_APP_CACHE_CTRL_REG ą┤ą╗čÅ čĆą░ąĘčĆąĄčłąĄąĮąĖčÅ č鹊ą╣ ąČąĄ čüą░ą╝ąŠą╣ čäčāąĮą║čåąĖąĖ.

ąĀąĖčü. 3. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║čŹčłą░.

ESP32 ąĖčüą┐ąŠą╗čīąĘčāąĄčé ą┤ą▓čāčüč鹊čĆąŠąĮąĮąĖą╣ ą░čüčüąŠčåąĖą░čéąĖą▓ąĮčŗą╣ ą║čŹčł (two-way set-associative cache). ąÜąŠą│ą┤ą░ čäčāąĮą║čåąĖčÅ ą║čŹčłą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą╗ąĖą▒ąŠ PRO_CPU, ą╗ąĖą▒ąŠ APP_CPU, ą▒ąĖčéčŗ CACHE_MUX_MODE[1:0] ą▓ čĆąĄą│ąĖčüčéčĆąĄ DPORT_CACHE_MUX_MODE_REG ą╝ąŠąČąĮąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī ą┤ą╗čÅ ą▓čŗą▒ąŠčĆą░ POOL0 ąĖą╗ąĖ POOL1 ą▓ ą┐ą░ą╝čÅčéąĖ Internal SRAM0 ą┤ą╗čÅ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ ą║čŹčłą░. ąÜąŠą│ą┤ą░ ąŠą▒ą░ PRO_CPU ąĖ APP_CPU ąĖčüą┐ąŠą╗čīąĘčāčÄčé čäčāąĮą║čåąĖčÄ ą║čŹčłąĖčĆąŠą▓ą░ąĮąĖčÅ, POOL0 ąĖ POOL1 ą▓ ą┐ą░ą╝čÅčéąĖ Internal SRAM0 ą▒čāą┤čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ą▓ ą║ą░č湥čüčéą▓ąĄ ą║čŹčłą░, čģąŠčéčÅ ąŠąĮąĖ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čłąĖąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖą╣. ąŁč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮąĖąČąĄ ą▓ čéą░ą▒ą╗ąĖčåąĄ 5.

ąóą░ą▒ą╗ąĖčåą░ 5. ąĀąĄąČąĖą╝ ą║čŹčłą░ ą┐ą░ą╝čÅčéąĖ.

| CACHE_MUX_MODE |

POOL0 |

POOL1 |

| 0 |

PRO_CPU |

APP_CPU |

| 1 |

PRO_CPU/APP_CPU |

- |

| 2 |

- |

PRO_CPU/APP_CPU |

| 3 |

APP_CPU |

PRO_CPU |

ąÜą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ą▓ čéą░ą▒ą╗ąĖčåąĄ 5, ą║ąŠą│ą┤ą░ ą▒ąĖčéčŗ CACHE_MUX_MODE čāčüčéą░ąĮąŠą▓ą╗ąĄąĮčŗ ą▓ 1 ąĖą╗ąĖ 2, PRO_CPU ąĖ APP_CPU ąĮąĄ ą╝ąŠą│čāčé čĆą░ąĘčĆąĄčłąĖčéčī čäčāąĮą║čåąĖčÄ ą║čŹčłą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ. ąÜąŠą│ą┤ą░ čäčāąĮą║čåąĖčÅ ą║čŹčłą░ čĆą░ąĘčĆąĄčłąĄąĮą░, POOL0 ąĖą╗ąĖ POOL1 ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ č鹊ą╗čīą║ąŠ ą▓ ą║ą░č湥čüčéą▓ąĄ ą┐ą░ą╝čÅčéąĖ ą║čŹčłą░, ąĖ ąĮąĄ ą╝ąŠą│čāčé čéą░ą║ąČąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ čłąĖąĮąŠą╣ ąĖąĮčüčéčĆčāą║čåąĖą╣.

ąÜčŹčł ESP32 ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé čäčāąĮą║čåąĖčÄ Flush. ąÜąŠą│ą┤ą░ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ Flush, č鹊 ą┤ą░ąĮąĮčŗąĄ, ą║ąŠč鹊čĆčŗąĄ ąĘą░ą┐ąĖčüą░ąĮčŗ ą▓ ą║čŹčłąĄ, ą┐ąĄčĆąĄąĘą░ą┐ąĖčüčŗą▓ą░čÄčéčüčÅ ą▓ External SRAM, ąĖ čüčéą░ąĮąŠą▓čÅčéčüčÅ ą▓ ą║čŹčłąĄ ąĮąĄ ą░ą║čéčāą░ą╗čīąĮčŗą╝ąĖ. ą¦č鹊ą▒čŗ čĆą░ąĘčĆąĄčłąĖčéčī čäčāąĮą║čåąĖčÄ Flush, čüąĮą░čćą░ą╗ą░ ąŠčćąĖčüčéąĖč鹥 ą▒ąĖčé x_CACHE_FLUSH_ENA ą▓ čĆąĄą│ąĖčüčéčĆąĄ DPORT_x_CACHE_CTRL_REG, ąĘą░č鹥ą╝ čāčüčéą░ąĮąŠą▓ąĖč鹥 čŹč鹊čé ą▒ąĖčé ą▓ 1. ą¤ąŠčüą╗ąĄ čŹč鹊ą│ąŠ ą░ą┐ą┐ą░čĆą░čéčāčĆą░ čüąĖčüč鹥ą╝čŗ čāčüčéą░ąĮąŠą▓ąĖčé ą▓ 1 ą▒ąĖčé x_CACHE_FLUSH_DONE. ąŚą┤ąĄčüčī ą▒čāą║ą▓ąŠą╣ x ąŠą▒ąŠąĘąĮą░č湥ąĮąŠ "PRO" ąĖą╗ąĖ "APP", ą┐ąŠą║ą░ąĘčŗą▓ą░čÅ ą┐čĆąĖąĮą░ą┤ą╗ąĄąČąĮąŠčüčéčī ąŠą┐ąĄčĆą░čåąĖąĖ flush ą║ ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮąŠą╝čā čÅą┤čĆčā CPU.

ąöą╗čÅ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą░ą┤čĆąĄčüą░čåąĖąĖ ą║čŹčłą░ ESP32 čüą╝. ą▓čĆąĄąĘą║ąĖ "ąÆąĮčāčéčĆąĄąĮąĮčÅčÅ ą┐ą░ą╝čÅčéčī" ąĖ "ąÆąĮąĄčłąĮčÅčÅ ą┐ą░ą╝čÅčéčī".

ąĪą║ąŠčĆąŠčüčéčī ą┐ą░ą╝čÅčéąĖ. ą¤ą░ą╝čÅčéčī ROM, ą║ą░ą║ ąĖ ą┐ą░ą╝čÅčéčī SRAM, ąŠą▒ąĄ čéą░ą║čéąĖčĆčāčÄčéčüčÅ ąŠčé CPU_CLK, ąĖ ą║ ąĮąĖą╝ CPU ą╝ąŠąČąĄčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ ąĘą░ ąŠą┤ąĖąĮ čéą░ą║čé. ą¤ą░ą╝čÅčéčī RTC FAST čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé APB_CLOCK, ąĖ ą┐ą░ą╝čÅčéčī RTC SLOW čéą░ą║čéąĖčĆčāąĄčéčüčÅ ąŠčé FAST_CLOCK, čéą░ą║ čćč鹊 ą┤ąŠčüčéčāą┐ ą║ čŹčéąĖą╝ ą┤ą▓čāą╝ ąŠą▒ą╗ą░čüčéčÅą╝ ą┐ą░ą╝čÅčéąĖ ą╝ąŠąČąĄčé ą▒čŗčéčī ą╝ąĄą┤ą╗ąĄąĮąĮąĄąĄ. ąöą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ą┐ą░ą╝čÅčéąĖ DMA ąĖčüą┐ąŠą╗čīąĘčāąĄčé APB_CLK.

ąÆąĮčāčéčĆąĖ SRAM ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮą░ ą▓ ą▓ąĖą┤ąĄ ą▒ą░ąĮą║ąŠą▓ ą┐ąŠ 32K. ąÜą░ąČą┤čŗą╣ CPU ąĖ ą║ą░ąĮą░ą╗ DMA ą╝ąŠąČąĄčé ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠ ąŠą▒čĆą░čēą░čéčīčüčÅ ą║ SRAM ąĮą░ ą┐ąŠą╗ąĮąŠą╣ čüą║ąŠčĆąŠčüčéąĖ ą┐čĆąĖ čāčüą╗ąŠą▓ąĖąĖ, čćč鹊 ąŠąĮąĖ ąĖą╝ąĄčÄčé ą┤ąŠčüčéčāą┐ ą║ ą░ą┤čĆąĄčüą░ą╝ ą▓ čĆą░ąĘą╗ąĖčćąĮčŗčģ ą▒ą░ąĮą║ą░čģ ą┐ą░ą╝čÅčéąĖ.

[ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░]

ąŻ ESP32 ąĄčüčéčī 41 ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ą░. ąÆ čéą░ą▒ą╗ąĖčåąĄ 6 ą┐ąŠą║ą░ąĘą░ąĮčŗ čŹčéąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ ąĖ ąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ ą┤ąĖą░ą┐ą░ąĘąŠąĮčŗ ą░ą┤čĆąĄčüąŠą▓. ą¤ąŠčćčéąĖ ą▓čüąĄ ą╝ąŠą┤čāą╗ąĖ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ ą┤ą╗čÅ ą╗čÄą▒ąŠą│ąŠ CPU ą┐ąŠ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ ą░ą┤čĆąĄčüčā ąĘą░ č鹊ą╗čīą║ąŠ ąŠą┤ąĮąĖą╝ ąĖčüą║ą╗čÄč湥ąĮąĖąĄą╝: PID-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ.

ąóą░ą▒ą╗ąĖčåą░ 6. Peripheral Address Mapping.

ą©ąĖąĮą░

|

ąöąĖą░ą┐ą░ąĘąŠąĮ ą░ą┤čĆąĄčüąŠą▓ |

ąĀą░ąĘą╝ąĄčĆ |

ąØą░ąĘąĮą░č湥ąĮąĖąĄ |

ąÜąŠą╝ą╝ąĄąĮčéą░čĆąĖą╣

|

| ą£ą╗ą░ą┤čłąĖą╣ ą░ą┤čĆąĄčü |

ąĪčéą░čĆčłąĖą╣ ą░ą┤čĆąĄčü |

| ąöą░ąĮąĮčŗąĄ |

0x3FF00000 |

0x3FF00FFF |

4 KB |

ąĀąĄą│ąĖčüčéčĆ DPort |

|

| 0x3FF01000 |

0x3FF01FFF |

4 KB |

ąŻčüą║ąŠčĆąĖč鹥ą╗čī AES |

|

| 0x3FF02000 |

0x3FF02FFF |

4 KB |

ąŻčüą║ąŠčĆąĖč鹥ą╗čī RSA |

|

| 0x3FF03000 |

0x3FF03FFF |

4 KB |

ąŻčüą║ąŠčĆąĖč鹥ą╗čī SHA |

|

| 0x3FF04000 |

0x3FF04FFF |

4 KB |

Secure Boot |

|

|

0x3FF05000 |

0x3FF0FFFF |

44 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF10000 |

0x3FF13FFF |

16 KB |

ąóą░ą▒ą╗ąĖčåą░ ą║čŹčłą░ MMU |

|

|

0x3FF14000 |

0x3FF1EFFF |

44 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF1F000 |

0x3FF1FFFF |

4 KB |

PID-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ |

ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ ą┐čĆąĖą▓čÅąĘą░ąĮąŠ ą║ CPU |

|

0x3FF20000 |

0x3FF3FFFF |

128 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF40000 |

0x3FF40FFF |

4 KB |

UART0 |

|

|

0x3FF41000 |

0x3FF41FFF |

4 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF42000 |

0x3FF42FFF |

4 KB |

SPI1 |

|

| 0x3FF43000 |

0x3FF43FFF |

4 KB |

SPI0 |

|

| 0x3FF44000 |

0x3FF44FFF |

4 KB |

GPIO |

|

|

0x3FF45000 |

0x3FF47FFF |

12 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF48000 |

0x3FF48FFF |

4 KB |

RTC |

|

| 0x3FF49000 |

0x3FF49FFF |

4 KB |

IO MUX |

|

|

0x3FF4A000 |

0x3FF4AFFF |

4 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF4B000 |

0x3FF4BFFF |

4 KB |

SDIO Slave |

ą×ą┤ąĮą░ ąĖąĘ 3 ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ |

| 0x3FF4C000 |

0x3FF4CFFF |

4 KB |

UDMA1 |

|

|

0x3FF4D000 |

0x3FF4EFFF |

8 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF4F000 |

0x3FF4FFFF |

4 KB |

I2S0 |

|

| 0x3FF50000 |

0x3FF50FFF |

4 KB |

UART1 |

|

|

0x3FF51000 |

0x3FF52FFF |

8 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF53000 |

0x3FF53FFF |

4 KB |

I2C0 |

|

| 0x3FF54000 |

0x3FF54FFF |

4 KB |

UDMA0 |

|

| 0x3FF55000 |

0x3FF55FFF |

4 KB |

SDIO Slave |

ą×ą┤ąĮą░ ąĖąĘ 3 ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ |

| 0x3FF56000 |

0x3FF56FFF |

4 KB |

RMT |

|

| 0x3FF57000 |

0x3FF57FFF |

4 KB |

PCNT |

|

| 0x3FF58000 |

0x3FF58FFF |

4 KB |

SDIO Slave |

ą×ą┤ąĮą░ ąĖąĘ 3 ąŠą▒ą╗ą░čüč鹥ą╣ ą┐ą░ą╝čÅčéąĖ |

| 0x3FF59000 |

0x3FF59FFF |

4 KB |

LED PWM |

|

| 0x3FF5A000 |

0x3FF5AFFF |

4 KB |

ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ eFuse |

|

| 0x3FF5B000 |

0x3FF5BFFF |

4 KB |

ą©ąĖčäčĆąŠą▓ą░ąĮąĖąĄ Flash |

|

|

0x3FF5C000 |

0x3FF5DFFF |

8 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF5E000 |

0x3FF5EFFF |

4 KB |

MCPWM0 |

|

| 0x3FF5F000 |

0x3FF5FFFF |

4 KB |

TIMG0 |

|

| 0x3FF60000 |

0x3FF60FFF |

4 KB |

TIMG1 |

|

|

0x3FF61000 |

0x3FF63FFF |

12 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF64000 |

0x3FF64FFF |

4 KB |

SPI2 |

|

| 0x3FF65000 |

0x3FF65FFF |

4 KB |

SPI3 |

|

| 0x3FF66000 |

0x3FF66FFF |

4 KB |

SYSCON |

|

| 0x3FF67000 |

0x3FF67FFF |

4 KB |

I2C1 |

|

| 0x3FF68000 |

0x3FF68FFF |

4 KB |

SDMMC |

|

| 0x3FF69000 |

0x3FF6AFFF |

8 KB |

EMAC |

|

| |

0x3FF6B000 |

0x3FF6BFFF |

4 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF6C000 |

0x3FF6CFFF |

4 KB |

MCPWM1 |

|

| 0x3FF6D000 |

0x3FF6DFFF |

4 KB |

I2S1 |

|

| 0x3FF6E000 |

0x3FF6EFFF |

4 KB |

UART2 |

|

| 0x3FF6F000 |

0x3FF6FFFF |

4 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| 0x3FF70000 |

0x3FF70FFF |

4 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

|

0x3FF71000 |

0x3FF74FFF |

16 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

| ąöą░ąĮąĮčŗąĄ |

0x3FF75000 |

0x3FF75FFF |

4 KB |

RNG |

|

|

0x3FF76000 |

0x3FF7FFFF |

40 KB |

ąŚą░čĆąĄąĘąĄčĆą▓ąĖčĆąŠą▓ą░ąĮąŠ |

|

ąŚą░ą╝ąĄčćą░ąĮąĖčÅ:

ŌĆó ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮčŗąĄ čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ ą║ąŠč鹊čĆčŗą╝ CPU ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé ą┤ąŠčüčéčāą┐ č湥čĆąĄąĘ ą░ą┤čĆąĄčüą░ 0x3FF40000 .. 0x3FF7FFFF (DPORT ą░ą┤čĆąĄčü), čéą░ą║ąČąĄ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ąŠčüčéčāą┐ąĮčŗ č湥čĆąĄąĘ ą░ą┤čĆąĄčüą░ 0x60000000 ~ 0x6003FFFF (AHB ą░ą┤čĆąĄčü). ąÉą┤čĆąĄčü (0x3FF40000 + n) ąĖ (0x60000000 + n) ą┐čĆąŠąĖąĘą▓ąŠą┤čÅčé ą┤ąŠčüčéčāą┐ ą║ ąŠą┤ąĮąŠą╝čā ąĖ č鹊ą╝čā ąČąĄ čüąŠą┤ąĄčƹȹĖą╝ąŠą╝čā, ą│ą┤ąĄ n = 0 .. 0x3FFFF.

ŌĆó CPU ą╝ąŠąČąĄčé ąŠą▒čĆą░čéąĖčéčīčüčÅ ą║ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ č湥čĆąĄąĘ ą░ą┤čĆąĄčü DPORT ą▒ąŠą╗ąĄąĄ čŹčäč乥ą║čéąĖą▓ąĮąŠ, č湥ą╝ č湥čĆąĄąĘ ą░ą┤čĆąĄčü AHB. ą×ą┤ąĮą░ą║ąŠ ą░ą┤čĆąĄčü DPORT ą░ą┤čĆąĄčü čģą░čĆą░ą║č鹥čĆąĖąĘčāąĄčéčüčÅ čüą┐ąĄą║čāą╗čÅčéąĖą▓ąĮčŗą╝ąĖ čćč鹥ąĮąĖčÅą╝ąĖ, čŹč鹊 ąŠąĘąĮą░čćą░ąĄčé, čćč鹊 ąĮąĄ ą│ą░čĆą░ąĮčéąĖčĆčāąĄčéčüčÅ, čćč鹊 ą║ą░ąČą┤ąŠąĄ čćč鹥ąĮąĖąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮąŠ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ą░ą┤čĆąĄčü DPORT ąĮą░čĆčāčłąĖčé ą┐ąŠčĆčÅą┤ąŠą║ ą┤ąŠčüčéčāą┐ą░ ąŠą┐ąĄčĆą░čåąĖą╣ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ ąĮą░ čłąĖąĮąĄ, čćč鹊ą▒čŗ ą┐ąŠą▓čŗčüąĖčéčī ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗čīąĮąŠčüčéčī, čćč鹊 ą╝ąŠąČąĄčé ą┐čĆąĖą▓ąĄčüčéąĖ ą║ ą░ą▓ą░čĆąĖą╣ąĮąŠą╝čā čüą▒ąŠčÄ ą┐čĆąŠą│čĆą░ą╝ą╝, čā ą║ąŠč鹊čĆčŗčģ ąĄčüčéčī čüčéčĆąŠą│ąĖąĄ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą║ ą┐ąŠčĆčÅą┤ą║čā ą┤ąŠčüčéčāą┐ą░ čćč鹥ąĮąĖčÅ/ąĘą░ą┐ąĖčüąĖ. ąĪ ą┤čĆčāą│ąŠą╣ čüč鹊čĆąŠąĮčŗ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą░ą┤čĆąĄčüą░ AHB ą┤ą╗čÅ čćč鹥ąĮąĖčÅ čĆąĄą│ąĖčüčéčĆąŠą▓ FIFO ą▒čāą┤ąĄčé ą┐čĆąĖą▓ąŠą┤ąĖčéčī ą║ ąĮąĄą┐čĆąĄą┤čüą║ą░ąĘčāąĄą╝čŗą╝ ąŠčłąĖą▒ą║ą░ą╝. ą¦č鹊ą▒čŗ ąŠą▒ąŠą╣čéąĖ čŹčéąĖ ą┐čĆąŠą▒ą╗ąĄą╝čŗ, čüčéčĆąŠą│ąŠ čüą╗ąĄą┤čāą╣č鹥 ąĖąĮčüčéčĆčāą║čåąĖčÅą╝, ąĘą░ą┤ąŠą║čāą╝ąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗą╝ ą▓ ą┤ąŠą║čāą╝ąĄąĮč鹥 [4], ąŠčüąŠą▒ąĄąĮąĮąŠ ą▓ čüąĄą║čåąĖčÅčģ 3.3, 3.10, 3.16 ąĖ 3.17.

ąÉčüąĖą╝ą╝ąĄčéčĆąĖčćąĮčŗą╣ PID-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ. ąÆ čüąĖčüč鹥ą╝ąĄ ESP32 ąĄčüčéčī ą┤ą▓ą░ PID-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░. ą×ąĮąĖ ąŠą▒čüą╗čāąČąĖą▓ą░čÄčé čüąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ čÅą┤čĆą░ PRO_CPU ąĖ APP_CPU. PRO_CPU ąĖ APP_CPU ą╝ąŠą│čāčé ą┐ąŠą╗čāčćąĖčéčī ą┤ąŠčüčéčāą┐ č鹊ą╗čīą║ąŠ ą║ čüą▓ąŠąĄą╝čā PID-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā, ąĮąŠ ąĮąĄ ą║ čćčāąČąŠą╝čā. ąÜą░ąČą┤čŗą╣ CPU ąĖčüą┐ąŠą╗čīąĘčāąĄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą┐ą░ą╝čÅčéąĖ 0x3FF1F000 .. 3FF1FFFF ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ čüą▓ąŠąĄą╝čā PID-ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆčā.

ąØąĄčüą╝ąĄąČąĮčŗąĄ (ą┐čĆąĄčĆčŗą▓ąĖčüčéčŗąĄ) ą┤ąĖą░ą┐ą░ąĘąŠąĮčŗ ą░ą┤čĆąĄčüąŠą▓ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓. ą¤ąĄčĆąĖč乥čĆąĖą╣ąĮąŠąĄ čāčüčéčĆąŠą╣čüčéą▓ąŠ SDIO Slave čüąŠčüč鹊ąĖčé ąĖąĘ čéčĆąĄčģ čćą░čüč鹥ą╣, ąĖ ą┤ą▓ą░ CPU ąĖčüą┐ąŠą╗čīąĘčāčÄčé ąĮąĄčüą╝ąĄąČąĮčŗąĄ ą░ą┤čĆąĄčüą░ ą┤ą╗čÅ ą┤ąŠčüčéčāą┐ą░ ą║ ąĮąĖą╝. ąóčĆąĖ čćą░čüčéąĖ ą┤ąŠčüčéčāą┐ąĮčŗ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░čģ ą░ą┤čĆąĄčüąŠą▓ 0x3FF4B000 .. 3FF4BFFF, 0x3FF55000 .. 3FF55FFF ąĖ 0x3FF58000 .. 3FF58FFF čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ ą║ą░ąČą┤ąŠą│ąŠ CPU. ą¤ąŠą┤ąŠą▒ąĮąŠ ą┤čĆčāą│ąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝, ą┤ąŠčüčéčāą┐ ą║ čŹčéąĖą╝ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗą╝ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ ąĖą┤ąĄąĮčéąĖč湥ąĮ ą┤ą╗čÅ ąŠą▒ąŠąĖčģ CPU.

[ąĪą╗ąŠą▓ą░čĆąĖą║]

AHB Advanced High-speed Bus, ą┐čĆąŠą┤ą▓ąĖąĮčāčéą░čÅ ą▓čŗčüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮą░čÅ čłąĖąĮą░.

APB Advanced Peripheral Bus, ą┐čĆąŠą┤ą▓ąĖąĮčāčéą░čÅ čłąĖąĮą░ ą┐ąĄčĆąĖč乥čĆąĖą╣ąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓.

DPORT ą┐ąŠčĆčé čłąĖąĮčŗ ą┤ą░ąĮąĮčŗčģ.

CPU Central Processor Unit, ą▓čŗčćąĖčüą╗ąĖč鹥ą╗čīąĮąŠąĄ čÅą┤čĆąŠ.

ECO Engineering Change Orders, čāą║ą░ąĘą░ąĮąĖčÅ ą┐ąŠ ąĖčüą┐čĆą░ą▓ą╗ąĄąĮąĖčÄ ąŠčłąĖą▒ąŠą║ ą║čĆąĖčüčéą░ą╗ą╗ą░ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ąĄą│ąŠ ą▓ąĄčĆčüąĖąĖ [4].

IO ą▓ą▓ąŠą┤/ą▓čŗą▓ąŠą┤.

MMU Memory Management Unit, ą▒ą╗ąŠą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░ą╝čÅčéčīčÄ.

MUX ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆ.

PID ą┐čĆąŠą┐ąŠčĆčåąĖąŠąĮą░ą╗čīąĮčŗą╣ ąĖąĮč鹥ą│čĆą░ą╗čīąĮąŠ-ą┤ąĖčäč乥čĆąĄąĮčåąĖą░ą╗čīąĮčŗą╣ (ą¤ąśąö) čĆąĄą│čāą╗čÅč鹊čĆ.

ROM Read-Only Memory, ą┐ą░ą╝čÅčéčī č鹊ą╗čīą║ąŠ ą┤ą╗čÅ čćč鹥ąĮąĖčÅ, ą¤ąŚąŻ.

RTC Real Tile Clock, čćą░čüčŗ čĆąĄą░ą╗čīąĮąŠą│ąŠ ą▓čĆąĄą╝ąĄąĮąĖ.

SRAM ą▓ąĮčāčéčĆąĄąĮąĮąĄąĄ ą×ąŚąŻ čü čāčüą║ąŠčĆąĄąĮąĮčŗą╝ ą┤ąŠčüčéčāą┐ąŠą╝.

[ąĪčüčŗą╗ą║ąĖ]

1. ESP32 Technical Reference Manual site:docs.espressif.com.

2. ESP32 DMA.

3. ą¤ąŠčĆčÅą┤ąŠą║ čüą╗ąĄą┤ąŠą▓ą░ąĮąĖčÅ ą▒ą░ą╣čé (endianness).

4. ESP32 ECO and Workarounds for Bugs site:espressif.com. |