|

ąøąĖąĮąĄą╣ąĮą░čÅ čäčāąĮą║čåąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝ čü ą┤ąĖą░ą┐ą░ąĘąŠąĮąŠą╝ čéčĆąĖ ą┤ąĄą║ą░ą┤čŗ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠčüčéąĖą│ąĮčāčéą░ čü ą┐ąŠą╝ąŠčēčīčÄ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ JFET, ą▓ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ ą▓ čåąĄą┐čī ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ. ą¤ąŠą╝ąĖą╝ąŠ ą┐čĆąĄą┤ąĄą╗čīąĮąŠą╣ ą┐čĆąŠčüč鹊čéčŗ čüčģąĄą╝čŗ, ą╝ąŠą│čāčé ą▒čŗčéčī čüą║ąŠąĮčüčéčĆčāąĖčĆąŠą▓ą░ąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčģąĄą╝ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ čāčüąĖą╗ąĄąĮąĖčÅ ąĮą░ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░čģ ą┤ą▓ąŠą╣ąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗčģ čāčüąĖą╗ąĖč鹥ą╗ąĄą╣ ąĖ čüą▒ąŠčĆą║ąĖ ąĖąĘ ą┤ą▓čāčģ JFET, ą╗ąĖą▒ąŠ ąĮą░ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗčģ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗčģ čāčüąĖą╗ąĖč鹥ą╗čÅčģ ąĖ čüą▒ąŠčĆą║ąĄ ąĖąĘ č湥čéčŗčĆąĄčģ JFET. ąóą░ą║ąĖąĄ čüčģąĄą╝čŗ ą╝ąŠą│čāčé ą▒čŗčéčī ą┤ą░ąČąĄ ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮčŗ čü ąĖąŠąĮąĮąŠ-ąĖą╝ą┐ą╗ą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ JFET ąĮą░ ąŠą┤ąĮąŠą╝ ąĖą╗ąĖ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą╝ąŠąĮąŠą╗ąĖčéąĮčŗčģ ą║čĆąĖčüčéą░ą╗ą╗ą░čģ ąŠą┐ąĄčĆą░čåąĖąŠąĮąĮčŗčģ čāčüąĖą╗ąĖč鹥ą╗ąĄą╣ (ą┤ą░ą╗ąĄąĄ čüąŠą║čĆą░čēąĄąĮąĮąŠ ą×ąŻ). ąöąĖą░ą┐ą░ąĘąŠąĮ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮ čü ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ ąŠčé 2:1 ą┤ąŠ 1000:1 ąĖ ą▓čŗčłąĄ, ąĮąŠ ą▓čģąŠą┤ąĮčŗąĄ čāčĆąŠą▓ąĮąĖ ąĮą░ą┐čĆčÅąČąĄąĮąĖą╣ ąŠą│čĆą░ąĮąĖč湥ąĮčŗ ą┤ąŠą┐čāčüčéąĖą╝čŗą╝ąĖ ąĖčüą║ą░ąČąĄąĮąĖčÅą╝ąĖ. ąĀą░ą▒ąŠčćą░čÅ ą┐ąŠą╗ąŠčüą░ čćą░čüč鹊čé ąĘą░ą▓ąĖčüąĖčé ąŠčé ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ ąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╣ ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąĄą┤ąĖąĮąĖčćąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą×ąŻ.

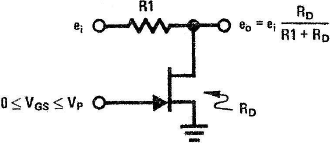

ąóčĆą░ąĮąĘąĖčüč鹊čĆ JFET ą┤ą░ą▓ąĮąŠ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą▓ ą║ą░č湥čüčéą▓ąĄ čĆąĄąĘąĖčüč鹊čĆą░, čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ (Voltage Controlled Resistor, čüąŠą║čĆą░čēąĄąĮąĮąŠ VCR), čćą░čüč鹊 ą║ą░ą║ ą┐ą╗ąĄč湊 čłčāąĮčéą░ čüčģąĄą╝čŗ ą░čéč鹥ąĮčÄą░č鹊čĆą░, ą║ą░ą║ ąĮą░ čüčģąĄą╝ąĄ čĆąĖčü. 1. ąöąŠčüč鹊ąĖąĮčüčéą▓ąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ JFET ą▓ ą║ą░č湥čüčéą▓ąĄ VCR:

1. ąĪąĖą│ąĮą░ą╗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐ąŠčćčéąĖ ąĖą┤ąĄą░ą╗čīąĮąŠ ąĖąĘąŠą╗ąĖčĆąŠą▓ą░ąĮ ąŠčé čåąĄą┐ąĖ čĆą░čüą┐čĆąŠčüčéčĆą░ąĮąĄąĮąĖčÅ čĆąĄą│čāą╗ąĖčĆčāąĄą╝ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░.

2. ąĪąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ VCR ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ąŠčé ąŠč湥ąĮčī ą╝ą░ą╗ąŠą│ąŠ ą┤ąŠ ą▒ąĄčüą║ąŠąĮąĄčćąĮąŠ ą▒ąŠą╗čīčłąŠą│ąŠ, čü ą┐ąŠčćčéąĖ ą▒ąĄčüą║ąŠąĮąĄčćąĮčŗą╝ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄą╝ max/min.

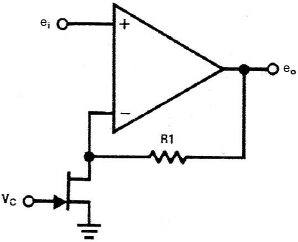

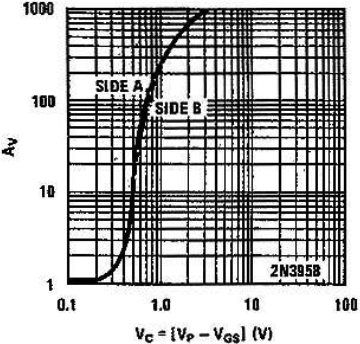

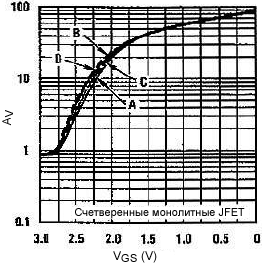

ąĀąĖčü. 1. JFET ą▓ čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą╝ ą┤ąĄą╗ąĖč鹥ą╗ąĄ čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░.

ą×ą┤ąĮą░ą║ąŠ ąĄčüčéčī ąĖ ąĮąĄą┤ąŠčüčéą░čéą║ąĖ:

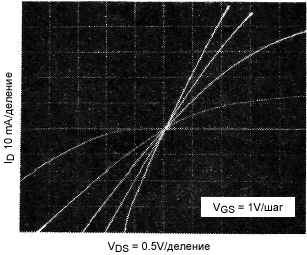

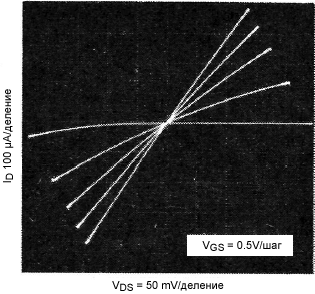

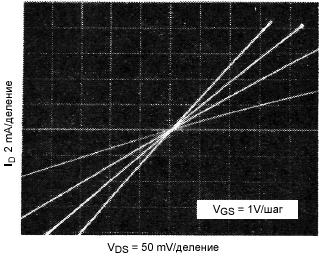

1. JFET ą▓ąĄą┤ąĄčé čüąĄą▒čÅ ą║ą░ą║ ą╗ąĖąĮąĄą╣ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ č鹊ą╗čīą║ąŠ ą┐čĆąĖ ą╝ą░ą╗čŗčģ ąĘąĮą░č湥ąĮąĖčÅčģ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüč鹊ą║-ąĖčüč鹊ą║ VDS.

2. ąØąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ą┐čĆąĖ ą┤ąŠčüčéąĖąČąĄąĮąĖąĖ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąĘą░čéą▓ąŠčĆ-ąĖčüč鹊ą║ VGS čāčĆąŠą▓ąĮčÅ ąŠčéčüąĄčćą║ąĖ VP, ą║ąŠą│ą┤ą░ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ.

3. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ RD ąŠčé VGS ąŠą▒čĆą░čéąĮą░čÅ, ą░ ąĮąĄ ą┐čĆčÅą╝ą░čÅ ą╗ąĖąĮąĄą╣ąĮą░čÅ.

4. ąØąĄčüą║ąŠą╗čīą║ąŠ VCR čü čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮčŗą╝ąĖ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ąĖ ą▓ ą┐ąŠą╗ąĮąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║čĆą░ą╣ąĮąĄ čéčĆčāą┤ąĮąŠ ą┐ąŠą╗čāčćąĖčéčī ą┐ąŠ ą╗čÄą▒ąŠą╣ čĆą░ąĘčāą╝ąĮąŠą╣ čåąĄąĮąĄ.

5. ą¤čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ąĄąĮąĮčŗą╣ čĆą░ąĘą▒čĆąŠčü ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčéčüąĄčćą║ąĖ VP čéčĆąĄą▒čāąĄčé ąŠčéą┤ąĄą╗čīąĮąŠą│ąŠ ą┐ąŠą┤ą▒ąŠčĆą░ čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą│ąŠ čüą╝ąĄčēąĄąĮąĖčÅ ąĖ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ą┐ąĄčĆąĄą┤ą░čćąĖ ą▓ ą║ą░ąČą┤ąŠą╣ čüčģąĄą╝ąĄ.

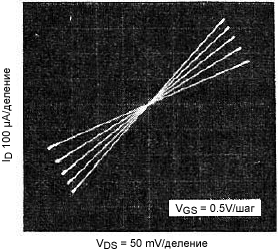

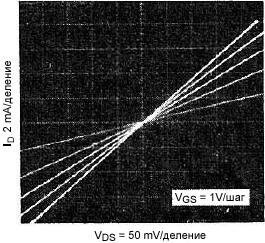

ąÉąĮą░ą╗ąĖąĘ čüč鹊ą║ąŠą▓čŗčģ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ JFET ąĮą░ čĆąĖčüčāąĮą║ą░čģ 2, 3, 4 ąĖ 5 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé čüčāčēąĄčüčéą▓ąĄąĮąĮčāčÄ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī RD ąĮą░ ą▒ąŠą╗čīčłąĖčģ čāčĆąŠą▓ąĮčÅčģ čüąĖą│ąĮą░ą╗ą░, ąŠčüąŠą▒ąĄąĮąĮąŠ ą┐čĆąĖ ą┐čĆąĖą▒ą╗ąĖąČąĄąĮąĖąĖ VGS ą║ VP. ąØčāąČąĮąŠ ąŠą▒ąŠą╣čéąĖ čŹč鹊čé ąĮąĄą╗ąĖąĮąĄą╣ąĮčŗą╣ čĆąĄą│ąĖąŠąĮ, čćč鹊ą▒čŗ ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą┐čĆąĖąĄą╝ą╗ąĄą╝čŗą╣ čāčĆąŠą▓ąĄąĮčī ąĖčüą║ą░ąČąĄąĮąĖą╣. ą×ą┤ąĖąĮ ąĖąĘ ąŠč湥ą▓ąĖą┤ąĮčŗčģ ą┐čāč鹥ą╣ ą┤ą╗čÅ čŹč鹊ą│ąŠ - ąŠą│čĆą░ąĮąĖčćąĖčéčī VDS ą╝ą░ą╗čŗą╝ąĖ ąĘąĮą░č湥ąĮąĖčÅą╝ąĖ, ą║ąŠą│ą┤ą░ RD ą▓čŗčüąŠą║ąŠąĄ, ą║ą░ą║ ą┐čĆąĄą┤ą╗ąŠąČąĄąĮąŠ čĆąĖčüčāąĮą║ą░ą╝ąĖ 4 ąĖ 5. ąöčĆčāą│ąŠą╣ čüą┐ąŠčüąŠą▒ - ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī JFET čü ą▓čŗčüąŠą║ąĖą╝ VP, ą║ą░ą║ ą┐čĆąĄą┤ą╗ąŠąČąĄąĮąŠ ąĮą░ čĆąĖčüčāąĮą║ą░čģ 3 ąĖ 5.

ąĀąĖčü. 2. VP = 2.8V.

ąĀąĖčü. 3. VP = 9V.

ąĀąĖčü. 4. VP = 2.8V.

ąĀąĖčü. 5. VP = 9V.

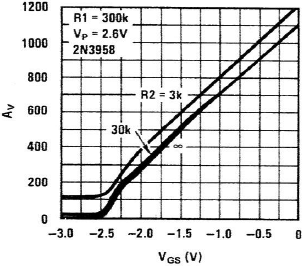

ą×ą▒čĆą░čéąĮąŠąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ RD ąĖ VG ą╝ąŠąČąĮąŠ ąŠą▒čĆą░čéąĖčéčī ą▓ ą┐čĆąĄąĖą╝čāčēąĄčüčéą▓ąŠ, ą┐ąŠčüą║ąŠą╗čīą║čā ąĖą╝ąĄąĮąĮąŠ ąŠąĮąŠ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąŠą┐ąĖčüčŗą▓ą░čéčī ą╗ąĖąĮąĄą╣ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čāčüąĖą╗ąĄąĮąĖąĄą╝ ą▓ čüčģąĄą╝ąĄ. ąØą░ą╗ąĖčćąĖąĄ čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮčŗčģ ą╝ąŠąĮąŠą╗ąĖčéąĮčŗčģ ą┤ą▓ąŠą╣ąĮčŗčģ JFET, čéą░ą║ąĖčģ ą║ą░ą║ 2N3958 (ąĮąĄ ą┐čŗčéą░ą╣č鹥čüčī ą┐ąŠą┤ąŠą▒čĆą░čéčī ąŠčéą┤ąĄą╗čīąĮčŗąĄ čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮčŗąĄ ą┐ą░čĆčŗ, ą┐ąŠč鹊ą╝čā čćč鹊 ąĖčģ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ą▒ą╗ąĖąĘą║ąŠ ą║ VP ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮąĄ ąĮą░čüč鹊ą╗čīą║ąŠ čģąŠčĆąŠčłąĖą╝, ą║ą░ą║ čā ą╝ąŠąĮąŠą╗ąĖčéąĮčŗčģ ą▓ąĄčĆčüąĖą╣ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓), ą┤ą░ąĄčé ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą┤ąŠčüčéąĖčćčī čĆą░ąĘčāą╝ąĮąŠą│ąŠ ą║ąŠą╝ą┐čĆąŠą╝ąĖčüčüą░ ą╝ąĄąČą┤čā čåąĄąĮąŠą╣ ąĖ čüąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄą╝ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ą▓ąŠ ą▓čüąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ. ąóą░ą║ąČąĄ čüčāčēąĄčüčéą▓čāčÄčé ą╝ąŠąĮąŠą╗ąĖčéąĮčŗąĄ č湥čéą▓ąĄčĆą║ąĖ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓. ąÜąŠąĮąĄčćąĮą░čÅ ą┐čĆąŠą▒ą╗ąĄą╝ą░ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ čü čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄą╝ VP ą╝ąŠąČąĄčé ą▒čŗčéčī čüąĮčÅčéą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą╝ąĄč鹊ą┤ąŠą▓ ąĖąŠąĮąĮąŠą│ąŠ ąĖą╝ą┐ą╗ą░ąĮčéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ VP ą▓ ą┐ą░čĆčéąĖąĖ ą╝ąŠąČąĄčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čéčīčüčÅ ą▓ ą┐čĆąĄą┤ąĄą╗ą░čģ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą┤ąĄčüčÅčéčŗčģ ą▓ąŠą╗čīčéą░.

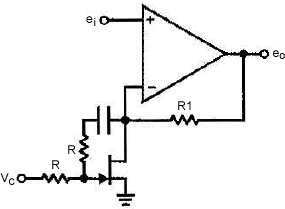

ąĀąĖčü. 6. AVMIN = 1.

ąĪčģąĄą╝ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅąĄčé čüąŠą▒ąŠą╣ ąŠą▒čŗčćąĮčāčÄ čüčģąĄą╝čā ąĮąĄ ąĖąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ, ąŠčģą▓ą░č湥ąĮąĮąŠą│ąŠ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘčīčÄ, čüą╝. čĆąĖčü. 6. ąŚą┤ąĄčüčī čĆąĄąĘąĖčüč鹊čĆ, ąŠčé ą║ąŠč鹊čĆąŠą│ąŠ ąĘą░ą▓ąĖčüąĖčé ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé čāčüąĖą╗ąĄąĮąĖčÅ AV, ąĘą░ą╝ąĄąĮąĄąĮ ąĮą░ RD ą║ą░ąĮą░ą╗ą░ ąĖčüč鹊ą║-čüč鹊ą║ ą┐ąŠą╗ąĄą▓ąŠą│ąŠ čéčĆą░ąĮąĘąĖčüč鹊čĆą░.

R1

AV = 1 + ---- (1)

RD

ąóąĄą┐ąĄčĆčī RD ą╝ąŠąČąĮąŠ ą┐čĆąĖčĆą░ą▓ąĮčÅčéčī ą║ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą╝čā ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ VC čüą╗ąĄą┤čāčÄčēąĖą╝ ąŠą▒čĆą░ąĘąŠą╝:

VP

RD = ro * ---------- (2)

VP - VGS

ąŚą┤ąĄčüčī

ro = RD | VGS = 0 (3)

VC = VP - VGS (4)

ą¤ąŠą╗čāčćą░ąĄčéčüčÅ, čćč鹊 čäčāąĮą║čåąĖčÅ čāčüąĖą╗ąĄąĮąĖčÅ ą╗ąĖąĮąĄą╣ąĮąŠ ąĘą░ą▓ąĖčüąĖčé ąŠčé VC:

R1*VC

AV = 1 + ------- (5)

ro*VP

ą¤čĆąĖ VC=0 čāčüąĖą╗ąĄąĮąĖąĄ čāą╝ąĄąĮčīčłąĖčéčīčüčÅ ą┤ąŠ 1. ą¤čĆąĖ VC=VP čāčüąĖą╗ąĄąĮąĖąĄ čāą▓ąĄą╗ąĖčćąĖčéčüčÅ ą┤ąŠ 1 + R1/ro, ąŠąĮąŠ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠčĆčÅą┤ą║ą░ 1000. ąĢčüą╗ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ąŠą│čĆą░ąĮąĖčćąĖčéčī ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠąĄ čāčüąĖą╗ąĄąĮąĖąĄ ąĮąĄą║ąŠč鹊čĆčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝, ą▒ąŠą╗čīčłąĖą╝ 1, č鹊 ą╝ąŠąČąĄčé ą▒čŗčéčī ą┤ąŠą▒ą░ą▓ą╗ąĄąĮ čĆąĄąĘąĖčüč鹊čĆ R2, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 7.

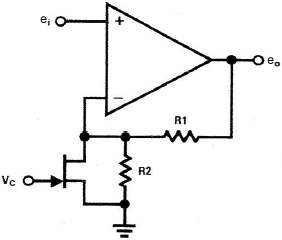

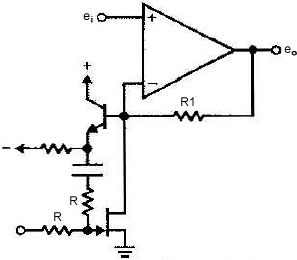

ąĀąĖčü. 7. AVMIN > 1.

ąóąŠą│ą┤ą░ č乊čĆą╝čāą╗ą░ ą┤ą╗čÅ čāčüąĖą╗ąĄąĮąĖčÅ ą┐ąŠą╗čāčćąĖčéčüčÅ čüą╗ąĄą┤čāčÄčēąĄą╣:

R1 R1*VC

AV = 1 + ---- + -------

R2 ro*VP

ąÆ ą╗čÄą▒ąŠą╝ čüą╗čāčćą░ąĄ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą╗ąĖąĮąĄą╣ąĮą░čÅ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéčī čāčüąĖą╗ąĄąĮąĖčÅ ąŠčé VC.

ąÆ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ čüčģąĄą╝čŗ ąĮą░ čĆąĖčü. 6 ąĖ 7 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą╗ąĖąĮąĄą╣ąĮčāčÄ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéčī ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ čāčüąĖą╗ąĄąĮąĖčÅ ąŠčé čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ąĘąĮą░č湥ąĮąĖą╣ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ, čćč鹊 ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 8 ą┤ą╗čÅ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ čü ą║ąŠčĆąŠčéą║ąĖą╝ ą║ą░ąĮą░ą╗ąŠą╝. ąĢčüčéčī ąĮąĄą║ąŠč鹊čĆą░čÅ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéčī, ą┐ąŠčÅą▓ą╗čÅčÄčēą░čÅčüčÅ ąĮą░ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░čģ čāčüąĖą╗ąĄąĮąĖčÅ, ą▒ą╗ąĖąĘą║ąĖčģ ą║ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╝, čćč鹊 ą▓ąĖą┤ąĮąŠ ąĮą░ ą▓čüąĄčģ ą║čĆąĖą▓čŗčģ. ąŁč鹊 ą▒ąĄąĘčāčüą╗ąŠą▓ąĮąŠ, čüą▓čÅąĘą░ąĮąŠ čü ąĮąĄąĖą┤ąĄą░ą╗čīąĮąŠą╣ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąŠą╣ JFET, ą▓čŗąĘą▓ą░ąĮąĮąŠą╣ ą║ąŠąĮąĄčćąĮčŗą╝ ą║ąŠąĮčéą░ą║č鹊ą╝ ąĖ ąŠą▒čŖąĄą╝ąĮčŗą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ čā ąĖčüč鹊ą║ą░ ąĖ čüč鹊ą║ą░.

ąĀąĖčü. 8. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī čāčüąĖą╗ąĄąĮąĖčÅ ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ JFET čü ą║ąŠčĆąŠčéą║ąĖą╝ ą║ą░ąĮą░ą╗ąŠą╝.

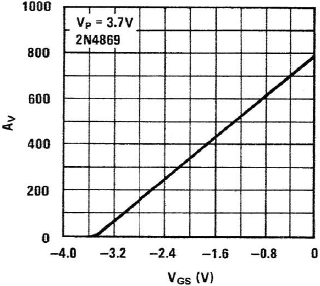

ąĀąĖčü. 9 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┐ąŠą┤ąŠą▒ąĮčāčÄ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéčī čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ JFET čü ą▒ąŠą╗ąĄąĄ ą┤ą╗ąĖąĮąĮčŗą╝ ą║ą░ąĮą░ą╗ąŠą╝, ą▓ ą║ąŠč鹊čĆąŠą╝ čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ čÅą▓ą╗čÅąĄčéčüčÅ ą▒ąŠą╗čīčłąĄą╣ čćą░čüčéčīčÄ ąŠą▒čēąĄą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ, č湥ą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ čéčĆą░ąĮąĘąĖčüč鹊čĆą░ čü ą║ąŠčĆąŠčéą║ąĖą╝ ą║ą░ąĮą░ą╗ąŠą╝, ą║čĆąĖą▓ą░čÅ ą║ąŠč鹊čĆąŠą│ąŠ ą┐ąŠą║ą░ąĘą░ąĮą░ ąĮą░ čĆąĖčü. 8. ąöą╗čÅ ą┐čĆąĖą╗ąŠąČąĄąĮąĖą╣ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ, čéčĆąĄą▒čāčÄčēąĖčģ ą▒ąŠą╗ąĄąĄ č鹊čćąĮąŠą╣ ą╗ąĖąĮąĄą╣ąĮąŠą╣ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝, ą┐čĆąĄą┤ą┐ąŠčćčéąĖč鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čéčĆą░ąĮąĘąĖčüč鹊čĆčŗ čü ą┤ą╗ąĖąĮąĮčŗą╝ ą║ą░ąĮą░ą╗ąŠą╝.

ąĀąĖčü. 9. ąŚą░ą▓ąĖčüąĖą╝ąŠčüčéčī čāčüąĖą╗ąĄąĮąĖčÅ ąŠčé ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ JFET čü ą┤ą╗ąĖąĮąĮčŗą╝ ą║ą░ąĮą░ą╗ąŠą╝.

ą£ąŠąČąĄčé ą▒čŗčéčī ą▓čŗą┐ąŠą╗ąĮąĄąĮąŠ ąĮąĄčüą║ąŠą╗čīą║ąŠ čüčģąĄą╝ čü ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗą╝ čāčüąĖą╗ąĄąĮąĖąĄą╝, ą║ąŠą│ą┤ą░ ą▓ ą║ą░č湥čüčéą▓ąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĖčģ 菹╗ąĄą╝ąĄąĮč鹊ą▓ čü čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮčŗą╝ąĖ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅą╝ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčéčüčÅ ą╝ąŠąĮąŠą╗ąĖčéąĮčŗąĄ čüą▒ąŠčĆą║ąĖ čü ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ JFET. ąöą▓ąŠą╣ąĮąŠą╣ JFET, čéą░ą║ąŠą╣ ą║ą░ą║ 2N3958 [2], ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗą╣ ą▓ ąŠą┤ąĖąĮą░ą║ąŠą▓čŗčģ čüčģąĄą╝ą░čģ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ąŠą┤ąĖąĮą░ą║ąŠą▓čāčÄ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║čā ą▓ąŠ ą▓čüąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ, ą┤ą░ąČąĄ ą║ąŠą│ą┤ą░ VGS ą┐čĆąĖą▒ą╗ąĖąČą░ąĄčéčüčÅ ą║ VP, ą║ąŠą│ą┤ą░ ąŠąČąĖą┤ą░čÄčéčüčÅ ąĮą░ąĖą▒ąŠą╗čīčłąĖąĄ čĆą░čüčģąŠąČą┤ąĄąĮąĖčÅ, čüą╝. ą│čĆą░čäąĖą║ąĖ ąĮą░ čĆąĖčü. 10. ą¤ąŠą┤ąŠą▒ąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┤ą╗čÅ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗčģ čüčģąĄą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┐čĆąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą╝ąŠąĮąŠą╗ąĖčéąĮąŠą╣ ą╝ąĖą║čĆąŠčüčģąĄą╝čŗ čü č湥čéčŗčĆčīą╝čÅ P-ą║ą░ąĮą░ą╗čīąĮčŗą╝ąĖ JFET (AM97C09 ąĖą╗ąĖ AM9709 ą║ąŠą╝ą┐ą░ąĮąĖąĖ National Semiconductor) ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčü. 11.

ąĀąĖčü. 10. ąĪąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝ ą┤ą╗čÅ ą┤ą▓ąŠą╣ąĮčŗčģ JFET.

ąĀąĖčü. 11. ąĪąŠą▓ą┐ą░ą┤ąĄąĮąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝ ą┤ą╗čÅ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗčģ JFET.

[ąśčüą║ą░ąČąĄąĮąĖčÅ]

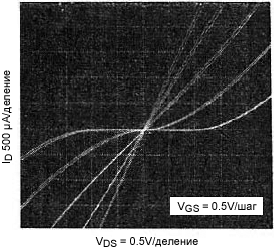

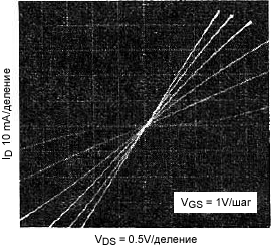

ąØą░ čĆąĖčüčāąĮą║ą░čģ 2, 3, 4 ąĖ 5 ą┐ąŠą║ą░ąĘą░ąĮąŠ, čćč鹊 JFET čĆą░ą▒ąŠčéą░čÄčé ą║ą░ą║ ą╗ąĖąĮąĄą╣ąĮąŠąĄ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ąĮąĖąĘą║ąŠą│ąŠ ąĘąĮą░č湥ąĮąĖčÅ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ čüč鹊ą║-ąĖčüč鹊ą║ VDS, ą┐čĆąĖą╗ąŠąČąĄąĮąĮąŠą│ąŠ ą▓ ą╗čÄą▒ąŠą╣ ą┐ąŠą╗čÅčĆąĮąŠčüčéąĖ. ąŁč鹊 ąŠčüąŠą▒ąĄąĮąĮąŠ ąŠč湥ą▓ąĖą┤ąĮąŠ ą┤ą╗čÅ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą│ąŠ VDS (ą┤ą╗čÅ N-ą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ JFET) ąĖ VGS, ą┐čĆąĖą▒ą╗ąĖąČą░čÄčēąĄą│ąŠčüčÅ ą║ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÄ ąŠčéčüąĄčćą║ąĖ VP. ą×čéą╗ąĖčćąĖčÅ čĆąĖčüčāąĮą║ąŠą▓ 4 ąĖ 5 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé, čćč鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą┤ąŠą┐čāčüčéąĖą╝čŗą╣ čüąĖą│ąĮą░ą╗ ą▒ąŠą╗čīčłąĄ ą┤ą╗čÅ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ čü ą▓čŗčüąŠą║ąĖą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝ ąŠčéčüąĄčćą║ąĖ VP ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü čéčĆą░ąĮąĘąĖčüč鹊čĆą░ą╝ąĖ, čā ą║ąŠč鹊čĆčŗčģ ą╝ąĄąĮčīčłąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ ąŠčéčüąĄčćą║ąĖ.

ą£ąŠąČąĮąŠ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čāą╗čāčćčłąĖčéčī čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ ą╗ąĖąĮąĄą╣ąĮąŠčüčéąĖ, ą┐čĆąĖą║ą╗ą░ą┤čŗą▓ą░čÅ čćą░čüčéčī VDS ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠ čü čāą┐čĆą░ą▓ą╗čÅčÄčēąĖą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄą╝, ą┐čĆąĖą╗ąŠąČąĄąĮąĮčŗą╝ ą║ VGS. ąĪčģąĄą╝čŗ, ą│ą┤ąĄ čŹč鹊 čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ, ą┐ąŠą║ą░ąĘą░ąĮčŗ ąĮą░ čĆąĖčüčāąĮą║ą░čģ 12 ąĖ 13.

ąĀąĖčü. 12. ą×ą▒čĆą░čéąĮą░čÅ čüą▓čÅąĘčī VDS/2, ą┐čĆąĖą╗ąŠąČąĄąĮąĮą░čÅ ą║ ąĘą░čéą▓ąŠčĆčā.

ąæčŗą▓ą░ąĄčé, čćč鹊 ąŠą║ąŠą╗ąŠ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ VDS, ą┐čĆąĖą╗ąŠąČąĄąĮąĮčŗčģ ą║ ąĘą░čéą▓ąŠčĆčā, ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ąĮą░ąĖą▒ąŠą╗čīčłąĄąĄ čāą╗čāčćčłąĄąĮąĖąĄ ą╗ąĖąĮąĄą╣ąĮąŠčüčéąĖ ą┤ą╗čÅ ą╝ą░ą╗čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ čüčéą░ą▓čÅčéčüčÅ ą┤ą▓ą░ čĆąĄąĘąĖčüč鹊čĆą░ ąĖ ąŠą┤ąĖąĮ ą║ąŠąĮą┤ąĄąĮčüą░č鹊čĆ, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 12. ąÜąŠąĮą┤ąĄąĮčüą░č鹊čĆ ą┐čĆąŠčüč鹊 ą▒ą╗ąŠą║ąĖčĆčāąĄčé ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĄ čāą┐čĆą░ą▓ą╗čÅčÄčēąĄą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ąŠčé čüč鹊ą║ą░ JFET ąĮą░ ą▓čģąŠą┤ ą×ąŻ.

ąĀąĖčü. 13. ą£ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░ąĮąĮą░čÅ čüčģąĄą╝ą░ čü ą▒čŗčüčéčĆčŗą╝ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄą╝.

ąĀąĖčü. 13 ą┐ąŠą║ą░ąĘčŗą▓ą░ąĄčé ą┤ąŠą▒ą░ą▓ą╗ąĄąĮąĖąĄ 菹╝ąĖčéč鹥čĆąĮąŠą│ąŠ ą┐ąŠą▓č鹊čĆąĖč鹥ą╗čÅ, čćč鹊ą▒čŗ ą┐čĆąĄą┤ąŠčéą▓čĆą░čéąĖčéčī čĆąĄąĘą║ąŠąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ VC ąŠčé ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖčÅ ąĮą░ ą×ąŻ.

ąĀąĖčü. 14. VP = 2.8V.

ąĀąĖčü. 15. VP = 9V.

ąĀąĖčüčāąĮą║ąĖ 14 ąĖ 15 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé čāą╗čāčćčłąĄąĮąĖąĄ ą╗ąĖąĮąĄą╣ąĮąŠčüčéąĖ čüč鹊ą║ą░ ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü čĆąĖčüčāąĮą║ą░ą╝ąĖ 2, 3, 4 ąĖ 5. ąŻą╗čāčćčłąĄąĮąĖąĄ čéą░ą║ąČąĄ ą▓ąĖą┤ąĮąŠ ą┐ąŠ ą│čĆą░čäąĖą║ą░ą╝ ąĖčüą║ą░ąČąĄąĮąĖą╣ ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąĮą░ čĆąĖčüčāąĮą║ą░čģ 16, 17, 20 ąĖ 21.

ąĀąĖčü. 16. ąśčüą║ą░ąČąĄąĮąĖąĄ čü VP = 2.8V.

ąĀąĖčü. 17. ąśčüą║ą░ąČąĄąĮąĖąĄ ą┐čĆąĖ VP = 2.8V čü ą╗ąĖąĮąĄą░čĆąĖąĘą░čåąĖąĄą╣.

ąĀąĖčü. 18. VP = 2.8V.

ąĀąĖčü. 19. VP = 9V.

ąĀąĖčü. 20. ąśčüą║ą░ąČąĄąĮąĖąĄ čü VP = 8.2V.

ąĀąĖčü. 21. ąśčüą║ą░ąČąĄąĮąĖąĄ ą┐čĆąĖ VP = 8.2V čü ą╗ąĖąĮąĄą░čĆąĖąĘą░čåąĖąĄą╣.

ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 čāčĆąŠą▓ąĄąĮčī ąĖčüą║ą░ąČąĄąĮąĖą╣ ą┐čĆąĖ ą╗čÄą▒ąŠą╝ ąĘąĮą░č湥ąĮąĖąĖ VC čÅą▓ą╗čÅąĄčéčüčÅ ą▓ ą┐ąĄčĆą▓čāčÄ ąŠč湥čĆąĄą┤čī čäčāąĮą║čåąĖąĄą╣ ąŠčé ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ (ą║ąŠč鹊čĆčŗą╣ čĆą░ą▓ąĄąĮ čüąĖą│ąĮą░ą╗čā ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ, ą┐ąŠą┤ą░ą▓ą░ąĄą╝ąŠą╝čā ąĮą░ čüč鹊ą║ JFET, ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮčŗą╣ ą║ ąĖąĮą▓ąĄčĆčüąĮąŠą╝čā ą▓čģąŠą┤čā ą×ąŻ). ąÆ čŹč鹊ą╣ ą┐čĆčÅą╝ąŠą╣ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ą┤ąĄą╗ą░ąĄčéčüčÅ ąĮąĄą║ąŠč鹊čĆą░čÅ ą╝ąŠą┤ąĖčäąĖą║ą░čåąĖčÅ, ąĄčüą╗ąĖ R2 čłčāąĮčéąĖčĆčāąĄčé JFET, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 7. ąóąŠą│ą┤ą░ ąĖąĘą╝ąĄčĆąĄąĮąĮąŠąĄ ąĖčüą║ą░ąČąĄąĮąĖąĄ ąĮą░ ąĮąĖąĘą║ąŠą╝ čāčĆąŠą▓ąĮąĄ čüąĖą│ąĮą░ą╗ą░ čÅą▓ą╗čÅąĄčéčüčÅ čĆąĄąĘčāą╗čīčéą░č鹊ą╝ čłčāą╝ą░, čüąĖą│ąĮą░ą╗ ą╝ą░ą╗ąŠ ą▓ą╗ąĖčÅąĄčé ąĮą░ čāčĆąŠą▓ąĄąĮčī ąĖčüą║ą░ąČąĄąĮąĖą╣. ąØą░ čŹčéąĖčģ ą│čĆą░čäąĖą║ą░čģ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ čāčüąĖą╗ąĄąĮąĖąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ ąŠą║ąŠą╗ąŠ 100, čćč鹊ą▒čŗ ąĖąĘą▒ąĄąČą░čéčī ąŠą▒ą╗ą░čüčéąĖ čü ąĮąĖąĘą║ąĖą╝ ąŠčéąĮąŠčłąĄąĮąĖąĄą╝ čüąĖą│ąĮą░ą╗/čłčāą╝. ąŚą┤ąĄčüčī čłčāą╝ ą┐čĆąĄą┤čüčéą░ą▓ą╗ąĄąĮ čłčāą╝ąŠą╝ ą▓čģąŠą┤ąĮąŠą│ąŠ ą║ą░čüą║ą░ą┤ą░ ą×ąŻ ąĖ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝ ąĖčüč鹊čćąĮąĖą║ą░ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░, ą┐ą╗čÄčü ą▓ą║ą╗ą░ą┤ čłčāą╝ą░ JFET, ą║ąŠč鹊čĆčŗą╣ ą▓ čüčāčēąĮąŠčüčéąĖ čÅą▓ą╗čÅąĄčéčüčÅ č鹥ą┐ą╗ąŠą▓čŗą╝ čłčāą╝ąŠą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ą║ą░ąĮą░ą╗ą░ RD.

[ą¤ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąĖ ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ]

ą¤ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ čüčģąĄą╝čŗ čŹč鹊 ą┐ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąĘą░ą╝ą║ąĮčāč鹊ą│ąŠ ą║ąŠąĮčéčāčĆą░ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ą×ąŻ, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝ąŠą│ąŠ ą┐čĆąĖ (ą╝ą│ąĮąŠą▓ąĄąĮąĮąŠą╝) čāčüčéą░ąĮąŠą▓ą╗ąĄąĮąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ. ą¤ąŠčüč鹊čÅąĮąĮąŠą╣ ą▓čĆąĄą╝ąĄąĮąĖ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ čāčüąĖą╗ąĄąĮąĖčÅ čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ ą▓čģąŠą┤ąĮąŠą╣ čåąĄą┐ąĖ ąĮą░ JFET (ąĘą░ą▓ąĖčüąĖčé ąŠčé ąĘąĮą░č湥ąĮąĖčÅ R ąĮą░ čĆąĖčü. 13), ąŠą│čĆą░ąĮąĖč湥ąĮąĮą░čÅ ą▒čŗčüčéčĆąŠą┤ąĄą╣čüčéą▓ąĖąĄą╝ ą×ąŻ. ąĪą░ą╝ JFET čĆąĄą░ą│ąĖčĆčāąĄčé ą┐čĆą░ą║čéąĖč湥čüą║ąĖ ą╝ą│ąĮąŠą▓ąĄąĮąĮąŠ, ą│ąĄąĮąĄčĆąĖčĆčāčÅ čüą║ą░č湊ą║ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčéą░ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┐ąŠčüč鹊čÅąĮąĮą░čÅ ą▓čĆąĄą╝ąĄąĮąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé ąĮąĄ ą▒ąŠą╗ąĄąĄ ąĮąĄčüą║ąŠą╗čīą║ąĖčģ ą╝ąĖą║čĆąŠčüąĄą║čāąĮą┤.

[ą×ą▒ą╗ą░čüčéąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖčÅ]

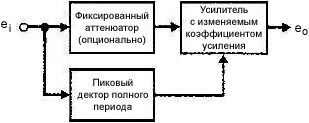

ąĪčģąĄą╝čŗ 菹╗ąĄą║čéčĆąŠąĮąĮąŠą╣ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ čāčüąĖą╗ąĄąĮąĖčÅ ą╝ąŠą│čāčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ą▓ čüą╗ąĄą┤čāčÄčēąĖčģ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ:

1. ąöąĖčüčéą░ąĮčåąĖąŠąĮąĮąŠąĄ ąĖą╗ąĖ ą╝ąĮąŠą│ąŠą║ą░ąĮą░ą╗čīąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čāčüąĖą╗ąĄąĮąĖąĄą╝.

2. ąĪąĖčüč鹥ą╝čŗ čłčāą╝ąŠą┐ąŠąĮąĖąČąĄąĮąĖčÅ, ąŠčüąĮąŠą▓ą░ąĮąĮčŗąĄ ąĮą░ čüąČą░čéąĖąĖ ąĖ čĆą░čüčłąĖčĆąĄąĮąĖąĖ ą┤ąĖąĮą░ą╝ąĖč湥čüą║ąŠą│ąŠ ą┤ąĖą░ą┐ą░ąĘąŠąĮą░ čüąĖą│ąĮą░ą╗ą░.

3. ą×ą│čĆą░ąĮąĖč湥ąĮąĖąĄ ą│čĆąŠą╝ą║ąŠčüčéąĖ, ą░ą▓č鹊ą╝ą░čéąĖč湥čüą║ąŠąĄ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖąĄ čāčĆąŠą▓ąĮčÅ.

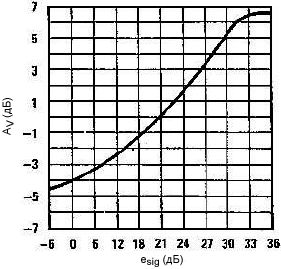

ąØą░ čĆąĖčü. 22 ą┐ąŠą║ą░ąĘą░ąĮ ą┐čĆąĖą╝ąĄčĆ čüčģąĄą╝čŗ čü čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╝ ą║ąŠčŹčäčäąĖčåąĖąĄąĮč鹊ą╝ čāčüąĖą╗ąĄąĮąĖčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ 1-1000, ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮčŗą╝ čāčĆąŠą▓ąĮąĄą╝ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ 8.5 Vrms, ąĖ ą┐ąŠą╗ąŠčüąŠą╣ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ čüą▓čŗčłąĄ 20 ą║ąōčå ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ. ąśčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ JFET čü ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▓čŗčüąŠą║ąĖą╝ VP, čćč鹊ą▒čŗ ą┐ąŠą╗čāčćąĖčéčī ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗąĄ ąĖčüą║ą░ąČąĄąĮąĖčÅ.

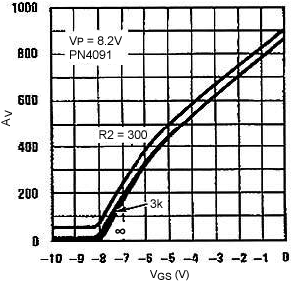

ąĀąĖčü. 22. ąĀąĄą│čāą╗ąĖčĆčāąĄą╝čŗą╣ čāčüąĖą╗ąĖč鹥ą╗čī čü ą┤ąĖą░ą┐ą░ąĘąŠąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖčÅ ąŠčé 1 ą┤ąŠ 1000.

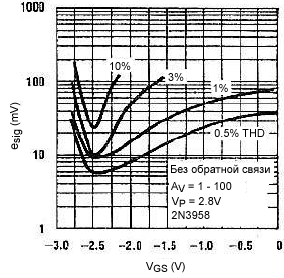

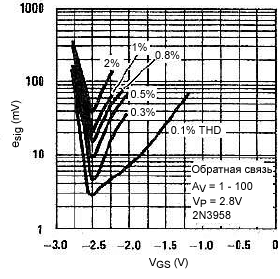

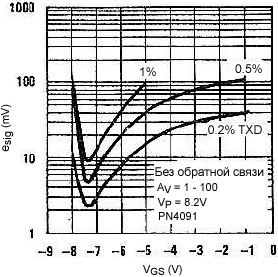

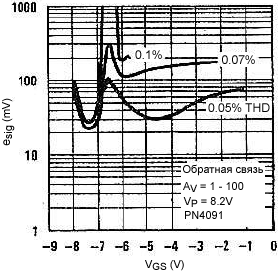

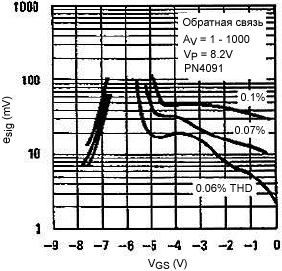

ąĀąĖčüčāąĮą║ąĖ 23 ąĖ 24 ą┐ąŠą║ą░ąĘčŗą▓ą░čÄčé ą│čĆą░čäąĖą║ąĖ ą┐ąŠčüč鹊čÅąĮąĮąŠą│ąŠ ąĖčüą║ą░ąČąĄąĮąĖčÅ. ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 ą║čĆąĖą▓ą░čÅ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝ ąĮąĄą╗ąĖąĮąĄą╣ąĮą░čÅ ą▓ą▒ą╗ąĖąĘąĖ ąĄą┤ąĖąĮąĖčćąĮąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ, ą┐ąŠč鹊ą╝čā čćč鹊 ą┐čĆąĖą╝ąĄąĮčÅąĄą╝čŗą╣ PN4091 čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą╗ąĄą▓čŗą╝ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą╝ čü ą║ąŠčĆąŠčéą║ąĖą╝ ą║ą░ąĮą░ą╗ąŠą╝ (short channel JFET).

ąĀąĖčü. 23. ąŻčüąĖą╗ąĄąĮąĖąĄ čüčģąĄą╝čŗ ąĮą░ čĆąĖčü. 22.

ąĀąĖčü. 24. ąśčüą║ą░ąČąĄąĮąĖąĄ čüčģąĄą╝čŗ ąĮą░ čĆąĖčü. 22. THD ąŠąĘąĮą░čćą░ąĄčé Total Harmonic Distortion, čé. ąĄ. ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé ąĮąĄą╗ąĖąĮąĄą╣ąĮčŗčģ ąĖčüą║ą░ąČąĄąĮąĖą╣.

ąśčüą║ą░ąČąĄąĮąĖąĄ ą┤ąŠčüčéą░č鹊čćąĮąŠ ąĮąĖąĘą║ąŠąĄ, ą║čĆąŠą╝ąĄ ąŠą│čĆą░ąĮąĖč湥ąĮąĖčÅ ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ ą▓čŗčģąŠą┤ąĮąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ. ą×č湥ą▓ąĖą┤ąĮąŠ, čćč鹊 ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ ein ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮą░čüčŗčēąĄąĮąĖąĄą╝ ąĮą░ ą▓čŗčģąŠą┤ąĄ. ąÆ čŹč鹊ą╝ ą┐čĆąĖą╝ąĄčĆąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ LM318 č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ čłąĖčĆąŠą║ąŠą┐ąŠą╗ąŠčüąĮąŠą│ąŠ ąŠčéą║ą╗ąĖą║ą░ ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ. ąÆčģąŠą┤ąĮąŠąĄ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĄ čāčüąĖą╗ąĖč鹥ą╗čÅ ą┤ąŠą╗ąČąĮąŠ ą▒čŗčéčī ąŠą│čĆą░ąĮąĖč湥ąĮąŠ ąĘąĮą░č湥ąĮąĖąĄą╝ ąŠą║ąŠą╗ąŠ 8 mVrms ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ, ą║ąŠą│ą┤ą░ ąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ čüąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą║ąŠą╗ąŠ 60 dB ąĮą░ ą┐ąŠą╗ąŠčüąĄ čćą░čüč鹊čé 10 ą║ąōčå.

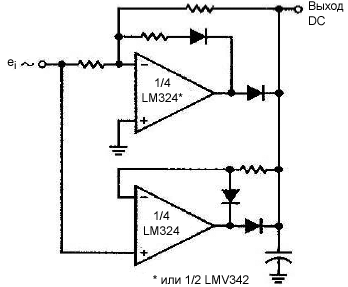

ąæąŠą╗ąĄąĄ ą┐čĆą░ą║čéąĖčćąĮą░čÅ čüčģąĄą╝ą░ ą╝ąŠąČąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą┤ąĖą░ą┐ą░ąĘąŠąĮ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ čāčüąĖą╗ąĄąĮąĖčÅ 1-100. ąóąŠą│ą┤ą░ ą╝ąŠąČąĮąŠ ą┐čĆąĖą╝ąĄąĮąĖčéčī ą×ąŻ LM301A, ąĖ ą▓čüąĄ ąĄčēąĄ ą▒čāą┤ąĄčé ąŠą▒ąĄčüą┐ąĄč湥ąĮą░ ą┐ąŠą╗ąŠčüą░ 10 ą║ąōčå ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ. ąĪąŠąŠčéą▓ąĄčéčüčéą▓ąĄąĮąĮąŠ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą╝ąŠąČąĄčé ą▒čŗčéčī čāą▓ąĄą╗ąĖč湥ąĮ ą┤ąŠ 80 mVrms ą┤ą╗čÅ ąŠčéąĮąŠčłąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗/čłčāą╝ 80 dB. ąŁčéąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą╝ąŠą│čāčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮčŗ ą┤ą╗čÅ čüčģąĄą╝ čü ą┤ą▓čāą╝čÅ ąĖą╗ąĖ č湥čéčŗčĆčīą╝čÅ ą║ą░ąĮą░ą╗ą░ą╝ąĖ, ąĮąŠ ąĮčāąČąĮąŠ čāą┤ąĄą╗ąĖčéčī ą▓ąĮąĖą╝ą░ąĮąĖąĄ čéčĆąĄą▒čāąĄą╝ąŠą╣ ą┐ąŠą╗ąŠčüąĄ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ ąĮą░ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ. ą£ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą╗čÄą▒ąŠą╣ čüą┤ą▓ąŠąĄąĮąĮčŗą╣ ą×ąŻ ą▓ą╝ąĄčüč鹥 čü 2N3958 (ą╝ąŠąĮąŠą╗ąĖčéąĮąŠ ąŠčĆą│ą░ąĮąĖąĘąŠą▓ą░ąĮąĮą░čÅ ą┐ą░čĆą░ JFET [2]), ąĖą╗ąĖ čüč湥čéą▓ąĄčĆąĄąĮąĮčŗą╣ ą×ąŻ LM324 ą▓ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅčģ čü ąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠą╣ ą┐ąŠą╗ąŠčüąŠą╣ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ, ą▓ą╝ąĄčüč鹥 čü ą╝ąŠąĮąŠą╗ąĖčéąĮčŗą╝ąĖ ą╝ąĖą║čĆąŠčüčģąĄą╝ą░ą╝ąĖ č湥čéčŗčĆąĄčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ JFET. ąØą░ čĆąĖčü. 25 ą┐ąŠą║ą░ąĘą░ąĮą░ čüčģąĄą╝ą░ ąŠą┤ąĮąŠą▓čĆąĄą╝ąĄąĮąĮąŠą│ąŠ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝ č湥čéčŗčĆąĄčģ ą║ą░ąĮą░ą╗ąŠą▓ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ 40 dB. ąĀąĄą│čāą╗ąĖčĆčāąĄą╝ąŠąĄ čāčüąĖą╗ąĄąĮąĖąĄą╝ ą┐čĆąĄą▓čŗčłą░ąĄčé ą┤ąĖą░ą┐ą░ąĘąŠąĮ 1-100, ą┐ąŠą╗ąŠčüą░ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé ą╝ąĖąĮąĖą╝čāą╝ 10 ą║ąōčå, čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ ą╗čāčćčłąĄ 70 dB ą┐čĆąĖ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠą╝ ąĮą░ą┐čĆčÅąČąĄąĮąĖąĖ ąĮą░ ą▓čŗčģąŠą┤ąĄ 4.3 Vrms. ąØą░ čĆąĖčü. 12 ą┐ąŠą║ą░ąĘą░ąĮą░ ą║čĆąĖą▓ą░čÅ čāčüąĖą╗ąĄąĮąĖčÅ ąĖ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ.

ąĀąĖčü. 25. ąŁą╗ąĄą║čéčĆąŠąĮąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čāčüąĖą╗ąĄąĮąĖąĄą╝ ą┤ą╗čÅ 4 ą║ą░ąĮą░ą╗ąŠą▓.

R = 1M

R1 = 20k

R2 = 5k

R3 = 240k

R4 = 10k

R5 = 10k

C1 = 0.01╬╝F

C2 = 1╬╝F

ąĪąŠąŠą▒čĆą░ąČąĄąĮąĖčÅ čłčāą╝ą░ ą╝ąŠą│čāčé ą▒čŗčéčī ą▓ą░ąČąĮčŗ ą▓ čŹč鹊ą╝ čüą┐ąŠčüąŠą▒ąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝, ą┐ąŠčüą║ąŠą╗čīą║čā čüąĖą│ąĮą░ą╗ čāčüąĖą╗ąĖą▓ą░ąĄčéčüčÅ, ą░ ąĮąĄ ąŠčüą╗ą░ą▒ą╗čÅąĄčéčüčÅ. ąöą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ čäčāąĮą║čåąĖąĖ čĆąĄą│čāą╗ąĖčĆčāąĄą╝ąŠą│ąŠ ą░čéč鹥ąĮčÄą░č鹊čĆą░ 40 dB ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čāčüčéą░ąĮąŠą▓ąĖčéčī čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮčŗą╣ ą░čéč鹥ąĮčÄą░č鹊čĆ ąĮą░ ą▓čģąŠą┤ąĄ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĖ ą▓ąŠąĘą╝ąŠąČąĮąŠ čéą░ą║ąČąĄ ąĮą░ ą▓čŗčģąŠą┤ąĄ. ąŁč鹊 čüąĮąĖąĘąĖčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗą╣ čāčĆąŠą▓ąĄąĮčī čüąĖą│ąĮą░ą╗ą░ ą┤ąŠ ą╝ąĖą╗ą╗ąĖą▓ąŠą╗čīčé, ą┐ąŠčŹč鹊ą╝čā ąČąĄą╗ą░č鹥ą╗ąĄąĮ ą╝ą░ą╗ąŠčłčāą╝čÅčēąĖą╣ čāčüąĖą╗ąĖč鹥ą╗čī. ą£ąŠąČąĄčé ą▒čŗčéčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮ čüą┤ą▓ąŠąĄąĮąĮčŗą╣ ą╝ą░ą╗ąŠčłčāą╝čÅčēąĖą╣ ą×ąŻ LM381 ą▓ ą░čéč鹥ąĮčÄą░č鹊čĆąĄ ąĘą▓čāą║ą░ 40 dB ą┐čĆąĖ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĖ čüąĖą│ąĮą░ą╗/čłčāą╝ ąŠą║ąŠą╗ąŠ 100 dB, ąĖą╗ąĖ ą▓ ą░čéč鹥ąĮčÄą░č鹊čĆąĄ 60 dB ą┐čĆąĖ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĖ čüąĖą│ąĮą░ą╗/čłčāą╝ 80 dB. ąŻą╗čāčćčłąĄąĮąĖąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖčÅ čüąĖą│ąĮą░ą╗/čłčāą╝ ą╝ąŠąČąĄčé ą▒čŗčéčī čĆąĄą░ą╗ąĖąĘąŠą▓ą░ąĮąŠ čüąĮąĖąČąĄąĮąĖąĄą╝ ą┐ąŠą╗ąŠčüčŗ ą┐čĆąŠą┐čāčüą║ą░ąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąŠą▒čĆą░ą▒ą░čéčŗą▓ą░ąĄčéčüčÅ čäąĖą║čüąĖčĆąŠą▓ą░ąĮąĮą░čÅ čćą░čüč鹊čéą░ ąĖą╗ąĖ ąĮąĖąĘą║ą░čÅ čćą░čüč鹊čéą░. ą£ąĖąĮąĖą╝ą░ą╗čīąĮąŠą│ąŠ čłčāą╝ą░ čéą░ą║ąČąĄ ą╝ąŠąČąĮąŠ ą┤ąŠčüčéąĖčćčī ą┐čāč鹥ą╝ čüąĮąĖąČąĄąĮąĖčÅ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĖčüč鹊čćąĮąĖą║ą░ čüąĖą│ąĮą░ą╗ą░, ąČąĄą╗ą░č鹥ą╗čīąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖčÅ ąĮąĖąČąĄ 1 ą║ą×ą╝.

ąśąĘą╝ąĄąĮąĄąĮąĖąĄ č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ ą▒čāą┤ąĄčé ą▓ą╗ąĖčÅčéčī ąĮą░ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ čāčüąĖą╗ąĄąĮąĖčÅ, ą┐ąŠč鹊ą╝čā čćč鹊 čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄ ą║ą░ąĮą░ą╗ą░ JFET ąĘą░ą▓ąĖčüąĖčé ąŠčé č鹥ą╝ą┐ąĄčĆą░čéčāčĆčŗ. ąŁč鹊čé čŹčäč乥ą║čé ą╝ąŠąČąĮąŠ čüąĮąĖąĘąĖčéčī ą┐čāč鹥ą╝ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ ą║čĆąĄą╝ąĮąĖąĄą▓ąŠą│ąŠ čĆąĄąĘąĖčüč鹊čĆą░ R1 ą┤ą╗čÅ čåąĄą┐ąĖ ąŠą▒čĆą░čéąĮąŠą╣ čüą▓čÅąĘąĖ ą×ąŻ. ąĢčüą╗ąĖ JFET ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░ąĮ ąĮą░ ą║čĆąĖčüčéą░ą╗ą╗ ą×ąŻ, č鹊 ąĮą░ čŹč鹊čé ąČąĄ ą║čĆąĖčüčéą░ą╗ą╗ ą╝ąŠąČąĮąŠ ą▒čŗą╗ąŠ ą▒čŗ ąĖąĮč鹥ą│čĆąĖčĆąŠą▓ą░čéčī ąĖ R1.

ąÆ ą┐čĆąĖą╗ąŠąČąĄąĮąĖąĖ 菹║čüą┐ą░ąĮą┤ąĄčĆą░ čāčĆąŠą▓ąĮčÅ (ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą▓ čüąĖčüč鹥ą╝ą░čģ čłčāą╝ąŠą┐ąŠąĮąĖąČąĄąĮąĖčÅ, čüą╝. čĆąĖčü. 26) čéčĆąĄą▒čāąĄą╝čŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čĆąĄą│čāą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ čüąŠčüčéą░ą▓ą╗čÅąĄčé ąŠą║ąŠą╗ąŠ 1:4, ąĖ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą╝ą░ą╗ ą┤ą╗čÅ čāčüą╗ąŠą▓ąĖą╣ ąĮąĖąĘą║ąŠą│ąŠ čāčüąĖą╗ąĄąĮąĖčÅ, ą║ąŠą│ą┤ą░ ąĖčüą║ą░ąČąĄąĮąĖąĄ ą╝ąŠąČąĄčé ą▒čŗčéčī ąĮą░ąĖą▒ąŠą╗ąĄąĄ ąŠč湥ą▓ąĖą┤ąĮčŗą╝.

ąĀąĖčü. 26. ąæą╗ąŠą║-čüčģąĄą╝ą░ ą║ąŠą╝ą┐čĆąĄčüčüąŠčĆą░/菹║čüą┐ą░ąĮą┤ąĄčĆą░ ą│čĆąŠą╝ą║ąŠčüčéąĖ.

ąöą╗čÅ čāą┐čĆą░ą▓ą╗čÅąĄą╝ąŠą│ąŠ čāčüąĖą╗ąĖč鹥ą╗čÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąĄčĆąĄą║čĆčŗčéčī ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖčÅ č鹊ą╗čīą║ąŠ 12 dB, čüą░ą╝čŗą╣ ąĮąĖąĘą║ąĖą╣ ą┤ą╗čÅ čüą╗ą░ą▒čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓. ąØą░ą║ą╗ąŠąĮ ą║čĆąĖą▓ąŠą╣ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ čāčüąĖą╗ąĄąĮąĖčÅ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą╗ąĖąĮąĄą╣ąĮčŗą╝, č鹊čćąĮąĄąĄ ą╗ąĖąĮąĄą╣ąĮąŠą╣ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéčī ąĮą░ą║ą╗ąŠąĮą░ čāčüąĖą╗ąĄąĮąĖčÅ dB (ą▓ ą╗ąŠą│ą░čĆąĖčäą╝ąĖč湥čüą║ąŠą╣ čłą║ą░ą╗ąĄ) ąŠčé čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░ (ą▓ ą╗ąŠą│ą░čĆąĖčäą╝ąĖč湥čüą║ąŠą╣ čłą║ą░ą╗ąĄ). ąØą░ ą┐čĆą░ą║čéąĖą║ąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┤ąĖą░ą┐ą░ąĘąŠąĮ čĆąĄą│čāą╗ąĖčĆąŠą▓ą║ąĖ čāčüąĖą╗ąĄąĮąĖčÅ 12 dB ą┐čĆąĖ ąĖąĘą╝ąĄąĮąĄąĮąĖąĖ ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čüą▓čŗčłąĄ 30 dB. ą¤ąĖą║ąŠą▓čŗą╣ ą┤ąĄč鹥ą║č鹊čĆ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą╗ąĖąĮąĄą╣ąĮčŗą╝ ą▓ą┐ą╗ąŠčéčī ą┤ąŠ ąŠč湥ąĮčī ą╝ą░ą╗čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓, ą┤ąĄą╝ąŠąĮčüčéčĆąĖčĆčāčÅ ą▒čŗčüčéčĆčāčÄ ą░čéą░ą║čā ąĖą╗ąĖ ą▓čĆąĄą╝čÅ ąĘą░čĆčÅą┤ą░ ą▓ ą╝ąĖą╗ą╗ąĖčüąĄą║čāąĮą┤čā ąĖą╗ąĖ ą╝ąĄąĮąĄąĄ, ą┐ąŠčüč鹊čÅąĮąĮčāčÄ ą▓čĆąĄą╝ąĄąĮąĖ ąĘą░čĆčÅą┤ą░ ąŠą║ąŠą╗ąŠ 2 čüąĄą║čāąĮą┤, ąĖ ąŠąĮ ą┤ąŠą╗ąČąĄąĮ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ ą┤ąĄč鹥ą║č鹊čĆ ą┐ąŠą╗ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░ čüąĖą│ąĮą░ą╗ą░. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝, ą┤ąĄč鹥ą║č鹊čĆ ą┤ąŠą╗ąČąĄąĮ čüąŠčģčĆą░ąĮčÅčéčī ą╗ąĖąĮąĄą╣ąĮąŠčüčéčī ą┐ąĖą║ąŠą▓ąŠą│ąŠ ą┤ąĄč鹥ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ ą┐ąŠą╗ąĮąŠą╝ ą┐ąĄčĆąĖąŠą┤ąĄ ąĖ ąŠą▒ą╗ą░ą┤ą░čéčī ąĮąĖąĘą║ąĖą╝ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╝ čüąŠą┐čĆąŠčéąĖą▓ą╗ąĄąĮąĖąĄą╝. ąŁčéąĖ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą╝ąŠąČąĮąŠ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖčéčī čüčģąĄą╝ąŠą╣ ąĮą░ čĆąĖčü. 27.

ąĀąĖčü. 27. ą¤ąĖą║ąŠą▓čŗą╣ ą╗ąĖąĮąĄą╣ąĮčŗą╣ ą┤ąĄč鹥ą║č鹊čĆ ą┐ąŠą╗ąĮąŠą│ąŠ ą┐ąĄčĆąĖąŠą┤ą░.

ą¢ąĄą╗ą░ąĄą╝čŗąĄ čĆą░ą▒ąŠčćąĖąĄ ą┐ąŠą║ą░ąĘą░č鹥ą╗ąĖ ą╝ąŠąČąĄčé ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüčģąĄą╝ą░, ą┐ąŠą║ą░ąĘą░ąĮąĮą░čÅ ąĮą░ čĆąĖčü. 28. ąōčĆą░čäąĖą║ čäčāąĮą║čåąĖąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čāčüąĖą╗ąĄąĮąĖąĄą╝ ą┐ąŠą║ą░ąĘą░ąĮ ąĮą░ čĆąĖčü. 29, ą┐čĆąĖ ą▓čüąĄčģ čāčĆąŠą▓ąĮčÅčģ čüąĖą│ąĮą░ą╗ą░ ąĖčüą║ą░ąČąĄąĮąĖčÅ ąĮąĖąČąĄ 0.1%. ąöąŠą▒ą░ą▓ą╗ąĄąĮčŗ čĆąĄąĘąĖčüč鹊čĆčŗ R3 ąĖ R4, čćč鹊ą▒čŗ ą╝ąŠą┤ąĖčäąĖčåąĖčĆąŠą▓ą░čéčī ą╗ąĖąĮąĄą╣ąĮčāčÄ ą║čĆąĖą▓čāčÄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čü ą┐čĆąĖą▓ąĄą┤ąĄąĮąĖąĄą╝ ąĄčæ ą║ ą╗ąŠą│ą░čĆąĖčäą╝ąĖč湥čüą║ąŠą╣ ą║čĆąĖą▓ąŠą╣.

ąĀąĖčü. 28. ąĪčģąĄą╝ą░ 菹║čüą┐ą░ąĮą┤ąĄčĆą░ čāčĆąŠą▓ąĮčÅ.

ąĀąĖčü. 29. ąźą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ čāčüąĖą╗ąĄąĮąĖčÅ čŹą║čüą┐ą░ąĮą┤ąĄčĆą░.

ąĪą╗ąĄą┤čāąĄčé ąŠčéą╝ąĄčéąĖčéčī, čćč鹊 ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ąŠčüą╗ą░ą▒ą╗čÅąĄčéčüčÅ ą┐ąĄčĆąĄą┤ čāčüąĖą╗ąĄąĮąĖąĄą╝, čćč鹊ą▒čŗ čāą╝ąĄąĮčīčłąĖčéčī ąĖčüą║ą░ąČąĄąĮąĖąĄ ąĖ ą┐ąŠą┤ą┤ąĄčƹȹ░čéčī ąŠą▒čēąĖą╣ ą║ąŠčŹčäčäąĖčåąĖąĄąĮčé čāčüąĖą╗ąĄąĮąĖčÅ ą┐čĆąĖą╝ąĄčĆąĮąŠ 0 dB ą▓ čüčĆąĄą┤ąĮąĄą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ čāčĆąŠą▓ąĮąĄą╣ 菹║čüą┐ą░ąĮą┤ąĄčĆą░. ą©čāą╝ LM124 ąĮą░ ą┐ąŠą╗ąŠčüąĄ čćą░čüč鹊čé 20 ą║ąōčå ąĘą░ą▓ąĖčüąĖčé, ą║ąŠąĮąĄčćąĮąŠ, ąŠčé čāčĆąŠą▓ąĮčÅ čüąĖą│ąĮą░ą╗ą░; ąŠą┤ąĮą░ą║ąŠ ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ čüąŠčüčéą░ą▓ą╗čÅąĄčé 80 dB. ąĪčģąĄą╝ą░ ą╝ąŠąČąĄčé ą▒čŗčéčī ą░ą┤ą░ą┐čéąĖčĆąŠą▓ą░ąĮą░ ą┤ą╗čÅ čüč鹥čĆąĄąŠ ąĖą╗ąĖ ą║ą▓ą░ą┤čĆąŠ. ąÆąŠą┐čĆąŠčüčŗ ą┐ąŠ ąĖąĮą┤ąĖą▓ąĖą┤čāą░ą╗čīąĮąŠą╝čā ą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮąĖčÄ ą║ą░čüą░čÄčéčüčÅ čüą┐ąŠčüąŠą▒ą░ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ - čüą╗ąĄą┤čāąĄčé ą╗ąĖ ą▓čŗą┐ąŠą╗ąĮčÅčéčī 菹║čüą┐ą░ąĮą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ą▓čüąĄčģ ą║ą░ąĮą░ą╗ąŠą▓ čüčĆą░ąĘčā, ąĖ čüą╗ąĄą┤čāąĄčé ą╗ąĖ ą┐ąŠą╗čāčćą░čéčī čüąĖą│ąĮą░ą╗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ąŠčéą┤ąĄą╗čīąĮąŠ ąŠčé ą║ą░ąČą┤ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░, ą╗ąĖą▒ąŠ ąŠčé čüčāą╝ą╝čā ąŠčé 2 ą┤ąŠ 4 ą║ą░ąĮą░ą╗ąŠą▓, ą╗ąĖą▒ąŠ č鹊ą╗čīą║ąŠ ąŠčé ąŠą┤ąĮąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ (ąĄčüą╗ąĖ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čéčī, čćč鹊 ą▓čŗčüąŠą║ąĖą╣ čāčĆąŠą▓ąĄąĮčī ąĮą░ ą╗čÄą▒ąŠą╝ ą║ą░ąĮą░ą╗ąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓čāąĄčé ą▓čŗčüąŠą║ąŠą╝čā čāčĆąŠą▓ąĮčÄ ą▓čüąĄčģ ą║ą░ąĮą░ą╗ąŠą▓). ą×ą▒čĆą░čéąĖč鹥 ą▓ąĮąĖą╝ą░ąĮąĖąĄ, čćč鹊 JFET čüą╝ąĄčēą░ąĄčéčüčÅ ą▓ čüč鹊čĆąŠąĮčā ąĘą░ą║čĆčŗčéąĖčÅ (ą┐čĆąĖ ą╝ąĖąĮąĖą╝ą░ą╗čīąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ) ą┤ą╗čÅ čüą╗ą░ą▒čŗčģ čüąĖą│ąĮą░ą╗ąŠą▓, ąĖ ą┐čĆąĖ čāą▓ąĄą╗ąĖč湥ąĮąĖąĖ čāčĆąŠą▓ąĮąĄą╣ čüąĖą│ąĮą░ą╗ąŠą▓ čüą╝ąĄčēąĄąĮąĖąĄ čāą▓ąĄą╗ąĖčćąĖą▓ą░ąĄčéčüčÅ ą▓ čüč鹊čĆąŠąĮčā ąŠčéą║čĆčŗčéąĖčÅ JFET (ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠąĄ čāčüąĖą╗ąĄąĮąĖąĄ).

[ąÆčŗą▓ąŠą┤čŗ]

ąÜąŠą╝ą▒ąĖąĮą░čåąĖčÅ JFET ąĖ ą×ąŻ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé čĆąĄą░ą╗ąĖąĘąŠą▓ą░čéčī ą╗ąĖąĮąĄą╣ąĮąŠąĄ čāą┐čĆą░ą▓ą╗ąĄąĮąĖąĄ čāčüąĖą╗ąĄąĮąĖąĄą╝ čāčĆąŠą▓ąĮčÅ ą▓ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ ą┤ąŠ 60 dB. ą¤ąŠčüą║ąŠą╗čīą║čā čüčģąĄą╝ą░ čĆąĄą░ą╗ąĖąĘčāąĄčé čĆąĄą│čāą╗ąĖčĆąŠą▓ą║čā ąĮą░ ą┐ąŠą╗ąŠąČąĖč鹥ą╗čīąĮąŠą╝ čāčüąĖą╗ąĄąĮąĖąĖ ą▓ą╝ąĄčüč鹊 ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą│ąŠ, čāčĆąŠą▓ąĄąĮčī ą▓čģąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčéčüčÅ. ąÆčģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąŠą│čĆą░ąĮąĖčćąĖą▓ą░ąĄčéčüčÅ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ąĖ čüąŠčéąĮčÅą╝ąĖ ą╝ąĖą╗ą╗ąĖą▓ąŠą╗čīčé ąĖąĘ-ąĘą░ ąĮąĄą╗ąĖąĮąĄą╣ąĮąŠčüčéąĖ JFET (ą║ąŠč鹊čĆčŗą╣ ą▓ąĖą┤ąĖčé ą┐ąŠą╗ąĮčŗą╣ ą▓čģąŠą┤ąĮąŠą╣ čüąĖą│ąĮą░ą╗). ą¤ąŠčüą║ąŠą╗čīą║čā ą┤ąĖą░ą┐ą░ąĘąŠąĮ ą▓čģąŠą┤ąĮčŗčģ čüąĖą│ąĮą░ą╗ąŠą▓ ąŠą▒čŗčćąĮąŠ čüąŠčüčéą░ą▓ą╗čÅąĄčé 10-300 mV, ą▓ą░ąČąĮčŗ čłčāą╝ąŠą▓čŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą▓čŗą▒čĆą░ąĮąĮąŠą│ąŠ ą×ąŻ. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ čŹč鹊 ą╝ąŠąČąĮąŠ ą┐ąŠą╗čāčćąĖčéčī čüąŠąŠčéąĮąŠčłąĄąĮąĖąĄ čüąĖą│ąĮą░ą╗/čłčāą╝ 60..100 dB ąĮą░ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą×ąŻ. ąĪąŠą│ą╗ą░čüąŠą▓ą░ąĮąĮą░čÅ ą┐ą░čĆą░ ąĖą╗ąĖ č湥čéą▓ąĄčĆą║ą░ čāčüąĖą╗ąĖč鹥ą╗ąĄą╣ čĆąĄą░ą╗ąĖąĘčāąĄą╝ą░ čü ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝ ą╝ąŠąĮąŠą╗ąĖčéąĮčŗčģ čéčĆą░ąĮąĘąĖčüč鹊čĆąŠą▓ JFET (2 ąĖą╗ąĖ 4 JFET ąĮą░ ąŠą┤ąĮąŠą╝ ą║čĆąĖčüčéą░ą╗ą╗ąĄ), ą░ čéą░ą║ąČąĄ ąĖąĮč鹥ą│čĆą░čåąĖąĄą╣ čŹčéąĖčģ JFET ą▓ą╝ąĄčüč鹥 čü ą×ąŻ ąĮą░ ąŠą┤ąĮąŠą╝ ą║čĆąĖčüčéą░ą╗ą╗ąĄ.

[ąĪčüčŗą╗ą║ąĖ]

1. AN-6603 A Linear Gain Controlled Amplifier site:onsemi.cn.

2. 2N3958 Monolithic N-Channel JFET Dual (VISHAY SILICONIX). |